# Four-Channel Video Driver with Selectable SD / HD Reconstruction Filters

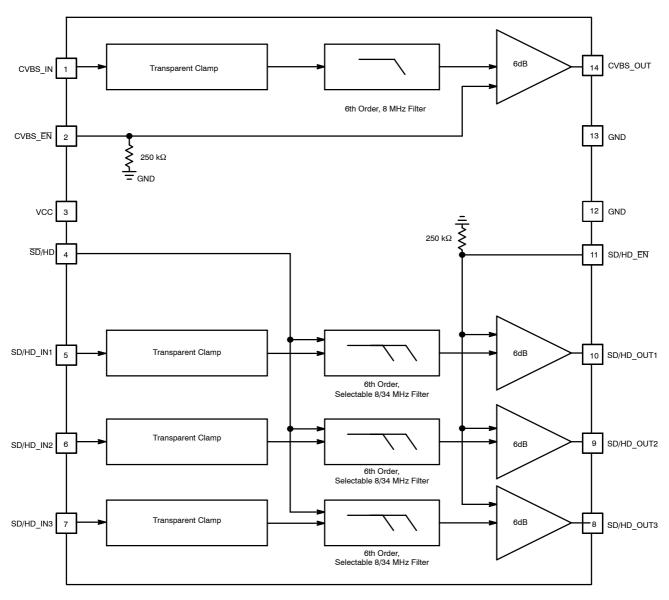

The NCS2564 is a 4-channel high speed video driver with 6th order Butterworth Reconstruction filters on each channel. A first set of 3-channel has selectable Standard Definition (SD) / High Definition (HD) filters, one per channel. A fourth channel offers an extra filter driver for driving CVBS-type video signal. The NCS2564 is in fact a combination of a triple SD/HD video driver plus a single CVBS video driver.

It is designed to be compatible with Digital-to-Analog Converters (DAC) embedded in most video processors.

To further reduce power consumption, 2 enable pins are provided one for the triple driver and another one for the single driver. One pin allows selecting the filter frequency of the triple driver. All channels can accept DC– or AC–coupled signals. In case of AC–coupled inputs, the internal clamps are enabled. The outputs can drive both AC and DC coupled 150  $\Omega$  loads.

#### **Features**

- 3-Channel with per Channel a Selectable Sixth-Order Butterworth 8/34 MHz Filter

- One CVBS Driver Including 6th Order Butterworth 8 MHz Filter

- Transparent Clamp

- Internal Fixed Gain: 6 dB ± 0.2

- Integrated Level Shifter

- AC- or DC-Coupled Inputs and Outputs

- Low Quiescent Current

- Shutdown Current 42 µA Typical (Disabled)

- Each channel Capable to Drive 2 by 150 Ω Loads

- Wide Operating Supply Voltage Range: +4.7 V to +5.3 V

- 8 kV ESD Protection (IEC61000-4-2 Compatible)

- TSSOP-14 Package

- These are Pb-Free Devices

#### **Typical Application**

- Set Top Box Decoder

- DVD Player / Recorder

- HDTV

# ON Semiconductor®

http://onsemi.com

# TSSOP-14 TBD SUFFIX CASE 948G

# MARKING DIAGRAM 14 HIIIII II

NCS2564 = Specific Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb-Free Package

#### **PINOUT** 14 CVBS OUT CVBS IN I CVBS\_EN \_\_\_\_2 13 GND vcc 🖂 з 12 GND SD/HD \_\_\_\_4 11 SD/HD\_EN SD/HD\_IN1 \_\_\_\_5 10 SD/HD\_OUT1 SD/HD IN2 6 9 SD/HD\_OUT2 SD/HD\_IN3 \_\_\_\_\_7 8 SD/HD\_OUT3 (Top View)

### ORDERING INFORMATION

| Device        | Package               | Shipping <sup>†</sup> |  |

|---------------|-----------------------|-----------------------|--|

| NCS2564DTBR2G | TSSOP-14<br>(Pb-Free) | 2500 /<br>Tape & Reel |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1

Figure 1. NCS2564 Block Diagram

# **PIN DESCRIPTION**

| Pin No. | Name                 | Туре   | Description                                                                                                                                                                             |

|---------|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CVBS_IN              | Input  | Video Input for Video Signal featuring a frequency bandwidth compatible with NTSC / PAL / SECAM Video (8 MHz) – CVBS Channel                                                            |

| 2       | CVBS_EN              | Input  | CVBS Channel Enable /Disable Function: Low = Enable, High = Disable. When left open the default state is Enable.                                                                        |

| 3       | VCC                  | Power  | Power Supply / 4.7 V to 5.3 V                                                                                                                                                           |

| 4       | SD/HD                | Input  | Pin of selection enabling the Standard Definition or High Definition Filters (8 MHz / 34 MHz) for channels SD/HD – when Low SD filters are selected, when High HD filters are selected. |

| 5       | SD/HD_IN1            | Input  | Selectable SD or HD Video Input 1 - SD/HD Channel 1                                                                                                                                     |

| 6       | SD/HD_IN2            | Input  | Selectable SD or HD Video Input 2 - SD/HD Channel 2                                                                                                                                     |

| 7       | SD/HD_IN3            | Input  | Selectable SD or HD Video Input 3 – SD/HD Channel 3                                                                                                                                     |

| 8       | SD/HD_OUT3           | Output | SD/HD Video Output 3 – SD/HD Channel 3                                                                                                                                                  |

| 9       | SD/HD_OUT2           | Output | SD/HD Video Output 2 - SD/HD Channel 2                                                                                                                                                  |

| 10      | SD/HD_OUT1           | Output | SD/HD Video Output 1 - SD/HD Channel 1                                                                                                                                                  |

| 11      | SD/HD_ <del>EN</del> | Input  | SD/HD Channel Enable/Disable Function: Low = Enable, High = Disable. When left open the default state is Enable.                                                                        |

| 12      | GND                  | Ground | Ground                                                                                                                                                                                  |

| 13      | GND                  | Ground | Ground                                                                                                                                                                                  |

| 14      | CVBS_OUT             | Output | CVBS Video Output – CVBS Channel                                                                                                                                                        |

#### **MAXIMUM RATINGS**

| Rating                                    | Symbol           | Value                       | Unit |

|-------------------------------------------|------------------|-----------------------------|------|

| Power Supply Voltages                     | V <sub>CC</sub>  | $-0.3 \le V_{CC} \le 5.5$   | Vdc  |

| I/O Voltage Range                         | V <sub>IO</sub>  | $-0.3 \le V_{I} \le V_{CC}$ | Vdc  |

| Input Differential Voltage Range          | V <sub>ID</sub>  | $-0.3 \le V_{I} \le V_{CC}$ | Vdc  |

| Output Current (Indefinitely) per Channel | I <sub>O</sub>   | 40                          | mA   |

| Maximum Junction Temperature (Note 1)     | TJ               | 150                         | °C   |

| Operating Ambient Temperature             | T <sub>A</sub>   | -40 to +85                  | °C   |

| Storage Temperature Range                 | T <sub>stg</sub> | -60 to +150                 | °C   |

| Thermal Resistance, Junction-to-Air       | $R_{	heta JA}$   | 125                         | °C/W |

| ESD Protection Voltage (IEC61000-4-2)     | V <sub>esd</sub> | >8000                       | V    |

| ESD HBM - Human Body Model                | НВМ              | 4000                        | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

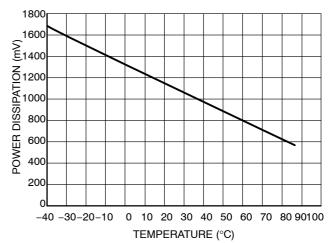

#### **Maximum Power Dissipation**

The maximum power that can be safely dissipated is limited by the associated rise in junction temperature. For the plastic packages, the maximum safe junction temperature is 150°C. If the maximum is exceeded momentarily, proper circuit operation will be restored as soon as the die temperature is reduced. Leaving the device in the "overheated" condition for an extended period can result in device burnout. To ensure proper operation, it is important to observe the derating curves.

Figure 2. Power Dissipation vs Temperature

<sup>1.</sup> Power dissipation must be considered to ensure maximum junction temperature (T<sub>J</sub>) is not exceeded.

**DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = +5.0 V,  $R_{source}$  = 37.5  $\Omega$ ,  $T_A$  = 25°C, inputs AC–coupled with 0.1  $\mu$ F, all outputs AC–coupled with 220  $\mu$ F into 150  $\Omega$  referenced to 400 kHz; unless otherwise specified)

| Symbol                 | Characteristics                                  | Conditions                                                                         | Min | Тур      | Max      | Unit     |  |  |

|------------------------|--------------------------------------------------|------------------------------------------------------------------------------------|-----|----------|----------|----------|--|--|

| POWER S                | POWER SUPPLY                                     |                                                                                    |     |          |          |          |  |  |

| V <sub>CC</sub>        | Supply Voltage Range                             |                                                                                    | 4.7 | 5.0      | 5.3      | V        |  |  |

| Icc                    | Supply Current                                   | SD Channels Selected + C <sub>vbs</sub><br>HD Channels Selected + C <sub>vbs</sub> |     | 40<br>50 | 55<br>70 | mA       |  |  |

| I <sub>SD</sub>        | Shutdown Current (CVBS_EN and SD/HD_EN High)     |                                                                                    |     | 42       | 60       | μΑ       |  |  |

| DC PERF                | DC PERFORMANCE                                   |                                                                                    |     |          |          |          |  |  |

| Vi                     | Input Common Mode Voltage Range                  |                                                                                    | GND |          | 1.4      | $V_{PP}$ |  |  |

| V <sub>IL</sub>        | Input Low Level for the Control Pins (2, 4, 11)  |                                                                                    | 0   |          | 0.8      | V        |  |  |

| V <sub>IH</sub>        | Input High Level for the Control Pins (2, 4, 11) |                                                                                    | 2.4 |          | $V_{CC}$ | V        |  |  |

| R <sub>pd</sub>        | Pulldown Resistors on Pins CVBS_EN and SD/HD_EN  |                                                                                    |     | 250      |          | kΩ       |  |  |

| OUTPUT CHARACTERISTICS |                                                  |                                                                                    |     |          |          |          |  |  |

| V <sub>OH</sub>        | Output Voltage High Level                        |                                                                                    |     | 2.8      |          | V        |  |  |

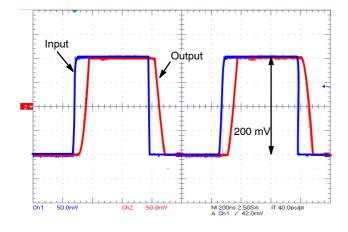

| V <sub>OL</sub>        | Output Voltage Low Level                         |                                                                                    |     | 200      |          | mV       |  |  |

| I <sub>O</sub>         | Output Current                                   |                                                                                    |     | 40       |          | mA       |  |  |

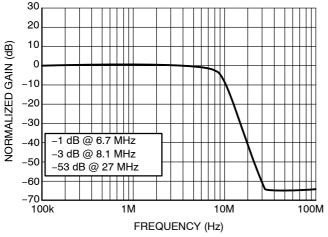

AC ELECTRICAL CHARACTERISTICS FOR STANDARD DEFINITION CHANNELS (pin numbers (1, 14) (5, 10), (6, 9), (7, 8)) ( $V_{CC}$  = +5.0 V,  $V_{in}$  = 1  $V_{PP}$ ,  $R_{source}$  = 37.5  $\Omega$ ,  $T_A$  = 25°C, inputs AC–coupled with 0.1  $\mu$ F, all outputs AC–coupled with 220  $\mu$ F into 150  $\Omega$  referenced to 400 kHz; unless otherwise specified,  $\overline{SD}/HD$  = Low)

| Symbol            | Characteristics                       | Conditions                                        | Min        | Тур        | Max | Unit |

|-------------------|---------------------------------------|---------------------------------------------------|------------|------------|-----|------|

| A <sub>VSD</sub>  | Voltage Gain                          | V <sub>in</sub> = 1 V - All SD Channels           | 5.8        | 6.0        | 6.2 | dB   |

| BW <sub>SD</sub>  | Low Pass Filter Bandwidth (Note 3)    | -1 dB<br>-3 dB                                    | 5.5<br>6.5 | 7.2<br>8.0 |     | MHz  |

| A <sub>RSD</sub>  | Stop-band Attenuation (Notes 3 and 4) | @ 27 MHz                                          | 43         | 50         |     | dB   |

| dG <sub>SD</sub>  | Differential Gain Error               |                                                   |            | 0.7        |     | %    |

| $d\Phi_{SD}$      | Differential Phase Error              |                                                   |            | 0.7        |     | 0    |

| THD               | Total Harmonic Distortion             | V <sub>out</sub> = 1.4 V <sub>PP</sub> @ 3.58 MHz |            | 0.35       |     | %    |

| X <sub>SD</sub>   | Channel-to-Channel Crosstalk          | @ 1 MHz and Vi <sub>n</sub> = 1.4 V <sub>PP</sub> |            | -57        |     | dB   |

| SNR <sub>SD</sub> | Signal-to-Noise Ratio                 | NTC-7 Test Signal, 100 kHz to 4.2 MHz (Note 2)    |            | 72         |     | dB   |

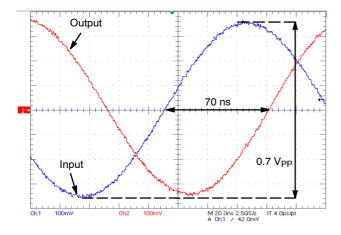

| $\Delta t_{SD}$   | Propagation Delay                     | @ 4.5 MHz                                         |            | 70         |     | ns   |

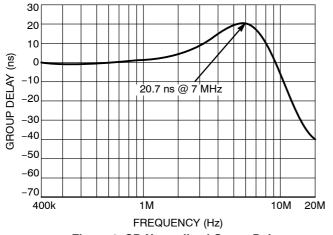

| $\Delta GD_SD$    | Group Delay Variation                 | 100 kHz to 8 MHz                                  |            | 20         |     | ns   |

<sup>2.</sup> SNR = 20 x log (714 mV / RMS noise)

<sup>3. 100%</sup> of Tested ICs fit the bandwidth and attenuation tolerance at 25°C.

<sup>4.</sup> Guaranteed by characterization.

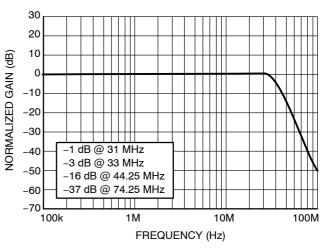

# AC ELECTRICAL CHARACTERISTICS FOR HIGH DEFINITION CHANNELS (pin numbers (5, 10) (6, 9), (7, 8))

$(V_{CC} = +5.0 \text{ V}, V_{in} = 1 \text{ V}_{PP}, R_{source} = 37.5 \ \Omega, T_A = 25^{\circ}\text{C}, \text{ inputs AC-coupled with } 0.1 \ \mu\text{F}, \text{ all outputs AC-coupled with } 220 \ \mu\text{F} \text{ into } 150 \ \Omega \text{ referenced to } 400 \ \text{kHz}; \text{ unless otherwise specified}, \overline{SD}/\text{HD} = \text{High})$

| Symbol            | Characteristics                              | Conditions                                                                                                                                            | Min      | Тур               | Max | Unit |

|-------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|-----|------|

| A <sub>VHD</sub>  | Voltage Gain                                 | V <sub>in</sub> = 1 V - All HD Channels                                                                                                               | 5.8      | 6.0               | 6.2 | dB   |

| BW <sub>HD</sub>  | Low Pass Filter Bandwidth                    | -1 dB (Note 6)<br>-3 dB (Note 7)                                                                                                                      | 26<br>30 | 31<br>34          |     | MHz  |

| A <sub>RHD</sub>  | Stop-band Attenuation                        | @ 44.25 MHz (Note 7)<br>@ 74.25 MHz (Note 6)                                                                                                          | 33       | 15<br>42          |     | dB   |

| THD <sub>HD</sub> | Total Harmonic Distortion                    | V <sub>out</sub> = 1.4 V <sub>PP</sub> @ 10 MHz<br>V <sub>out</sub> = 1.4 V <sub>PP</sub> @ 15 MHz<br>V <sub>out</sub> = 1.4 V <sub>PP</sub> @ 20 MHz |          | 0.4<br>0.6<br>0.8 |     | %    |

| X <sub>HD</sub>   | Channel-to-Channel Crosstalk                 | @ 1 MHz and V <sub>in</sub> = 1.4 V <sub>PP</sub>                                                                                                     |          | -60               |     | dB   |

| SNR <sub>HD</sub> | Signal-to-Noise Ratio                        | White Signal, 100 kHz to 30 MHz, (Note 5)                                                                                                             |          | 72                |     | dB   |

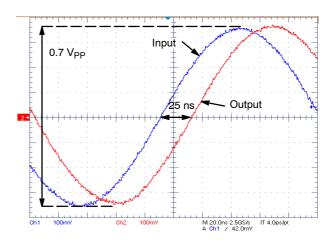

| $\Delta t_{HD}$   | Propagation Delay                            |                                                                                                                                                       |          | 25                |     | ns   |

| ∆GD <sub>HD</sub> | Group Delay Variation from 100 kHz to 30 MHz |                                                                                                                                                       |          | 10                |     | ns   |

SNR = 20 x log (714 mV / RMS noise)

Guaranteed by Characterization.

100% of Tested ICs fit the bandwidth and attenuation tolerance at 25°C.

#### TYPICAL CHARACTERISTICS

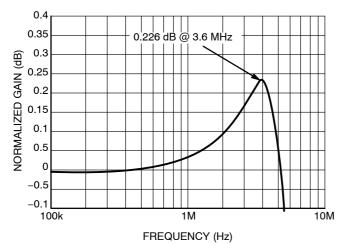

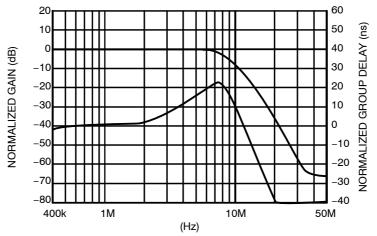

Figure 3. SD Normalized Frequency Response

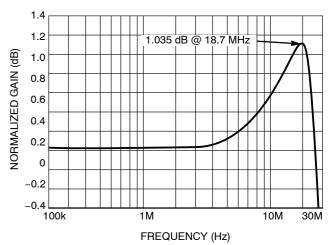

Figure 4. HD Normalized Frequency Response

Figure 5. SD Passband Flatness

Figure 6. HD Passband Flatness

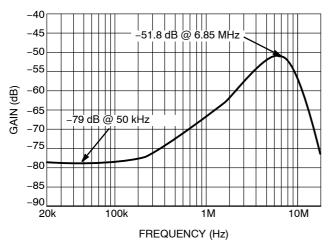

Figure 7. SD Channel-to-Channel Crosstalk

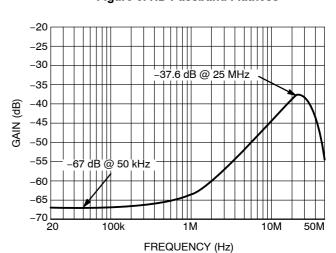

Figure 8. HD Channel-to-Channel Crosstalk

# **TYPICAL CHARACTERISTICS**

10 5 GROUP DELAY (ns) 0 -5 9.1 ns @ 24 -10 -15 -20 -25 -30 -35 400k 1M 10M 100M FREQUENCY (Hz)

Figure 9. SD Normalized Group Delay

Figure 10. HD Normalized Group Delay

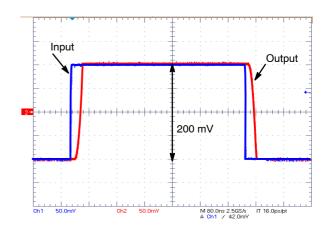

Figure 11. SD Propagation Delay

Figure 12. HD Propagation Delay

Figure 13. SD Small Signal Response

Figure 14. HD Small Signal Response

# **TYPICAL CHARACTERISTICS**

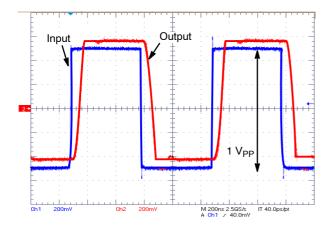

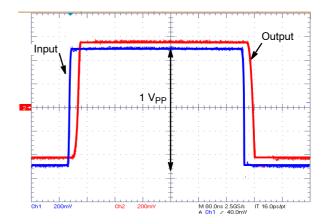

Figure 15. SD Large Signal Response

Figure 16. HD Large Signal Response

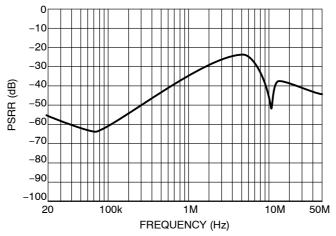

Figure 17. SD and HD  $V_{CC}$  PSRR vs. Frequency

# **TYPICAL CHARACTERISTICS**

Figure 18. SD Frequency Response and Group Delay

Figure 19. HD Frequency Response and Group Delay

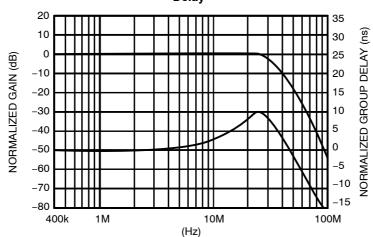

Figure 20. SD Differential Gain

Figure 21. SD Differential Phase

#### **APPLICATIONS INFORMATION**

The NCS2564 quad video driver has been optimized for Standard and High Definition video applications covering the requirements of the standards Composite video (CVBS), S–Video, Component Video (480i/525i, 576i/625i, 720p/1080i) and related (RGB). The three SD/HD channels have selectable filters (8 MHz and 34 MHz) for covering either standard definition–like video applications or High Definition video applications. These frequencies are selectable using the pin  $\overline{\rm SD}/{\rm HD}$ .

In the regular mode of operation each channel provides an internal voltage—to—voltage gain of 2 from input to output. This effectively reduces the number of external components

required as compared to discrete approached implemented with stand alone op amps. An internal level shifter is employed shifting up the output voltage by adding an offset of 200 mV. This prevents sync pulse clipping and allows DC–coupled output to the 150  $\Omega$  video load. In addition, the NCS2564 integrates a  $6^{th}$  order Butterworth filter for each. This allows rejection of the aliases or unwanted over-sampling effects produced by the video DAC. Similarly for the case of DVD recorders which use an ADC, this anti–aliasing filter (reconstruction filter) will avoid picture quality issue and will aide filtration of parasitic signals caused by EMI interference.

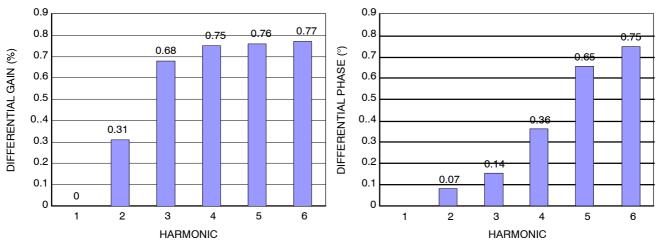

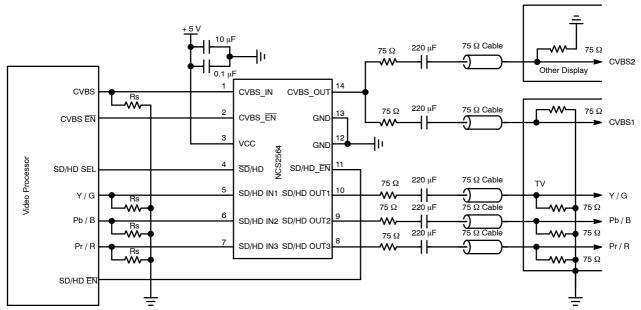

Figure 22. AC-Coupled Configuration at the Input and Output

A built-in diode-like clamp is used into the chip for each channel to support the AC-coupled mode of operation. The clamp is active when the input signal goes below 0 V.

The built–in clamp and level shifter allow the device to operate in different configuration modes depending on the DAC output signal level and the input common mode voltage of the video driver. When the configuration is DC–Coupled at the Inputs and Outputs the 0.1  $\mu F$  and 220  $\mu F$  coupling capacitors are no longer used, and the clamps are in that case inactive; this configuration provides a low cost solution which can be implemented with few external components (Figure 23).

The input is AC-coupled when either the input-signal amplitude goes over the range 0 V to 1.4 V or the video source requires such a coupling. In some circumstances it may be necessary to auto-bias signals with the addition of a pullup and pulldown resistors or only pullup resistor (Typical 7.5 M $\Omega$  combined with the internal 800 k $\Omega$  pulldown) making the clamp inactive.

The output AC-coupling configuration is advantageous for eliminating DC ground loop with the drawback of making the device more sensitive to video line or field tilt issues in the case of a too low output coupling capacitor. In

some cases it may be necessary to increase the nominal  $220 \, \mu F$  capacitor value.

#### **Shutdown Mode**

If the enable pins are left open by default the circuit will be enabled. The Enable pin offers a shutdown function, so the NCS2564 can consequently be disabled when not used. The NCS2564's quiescent current reduces to 42  $\mu$ A typical during shutdown mode.

# DC-Coupled Output

The outputs of the NCS2564 can be DC-coupled to a  $150\,\Omega$  load (Figure 23). This has the advantage of eliminating the AC-coupling capacitors at the output by reducing the number of external components and saving space on the board. This can be a key advantage for some applications with limited space.

The problems of field tilt effects on the video signal are also eliminated providing the best video quality with optimal dynamic or peak-to-peak amplitude of the video signal allowing operating thanks to the built-in level shifter without risk of signal clipping. In this coupling configuration the average output voltage is higher than 0 V and the power consumption can be a little higher than with an AC-coupled configuration.

Figure 23. DC-Coupled Input and Output Configuration

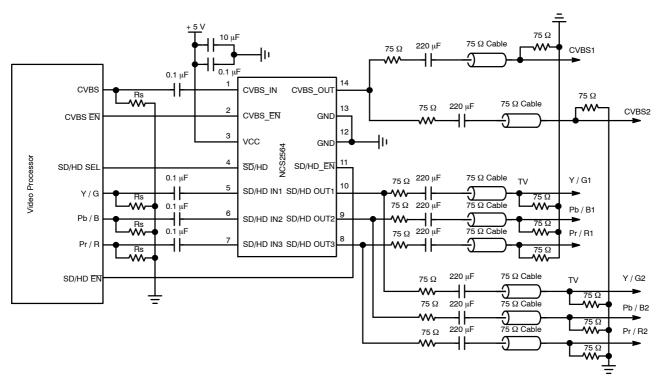

Figure 24. Typical Application

Figure 25. NCS2564 Driving 2 SCARTS Simultaneously

# **Video Driving Capability**

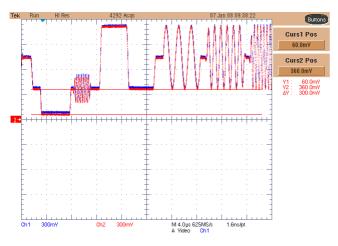

With an output current capability of 40 mA the NCS2564 was designed to be able to drive at least 2 video display loads in parallel. This type of application is illustrated Figure 24. Figure 26 (multiburst) and Figure 27 (linearity) show that the video signal can efficiently drive a 75  $\Omega$  equivalent load and not degrade the video performance.

# **ESD Protection**

All the device pins are protected against electrostatic discharge at a level of 4 kV HBM and 8 kV according to IEC61000–4–2. This feature has been considered with a particular attention with ESD structure able to sustain the typical values requested by the systems like Set Top Boxes or Blue–Ray players. This parameter is particularly important for video driver which usually constitutes the last stage in the video chain before the video output connector. The IEC61000–4–2 standard has been used to test our devices in the real application environment. Test methodology can be provided on request.

Curst Pos

60 0mY

Cursz Pos

1.11V

V1: 60 0mV

22: 11V

4V: 110SV

A 10 Dps 1 25636 800pspkr A

White Orl 1 A video Orl 1 A video

Figure 26. Multiburst Test with Two 150  $\Omega$  Loads

Figure 27. Linearity Test with Two 150  $\Omega$  Loads

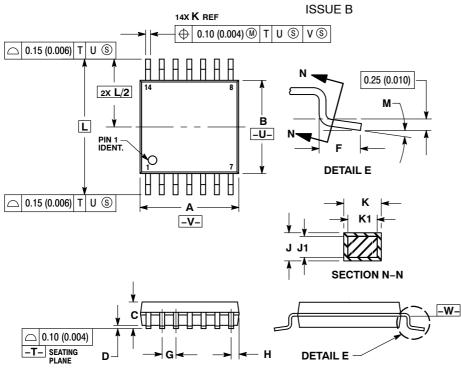

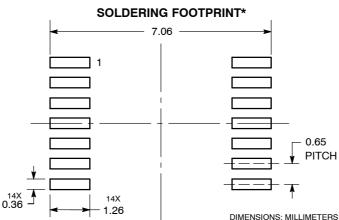

#### PACKAGE DIMENSIONS

#### TSSOP-14 CASE 948G-01

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M. 1982.

- CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

- DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION. TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN | IETERS | INCHES |       |  |

|-----|--------|--------|--------|-------|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |

| Α   | 4.90   | 5.10   | 0.193  | 0.200 |  |

| В   | 4.30   | 4.50   | 0.169  | 0.177 |  |

| С   |        | 1.20   |        | 0.047 |  |

| D   | 0.05   | 0.15   | 0.002  | 0.006 |  |

| F   | 0.50   | 0.75   | 0.020  | 0.030 |  |

| G   | 0.65   | BSC    | 0.026  | BSC   |  |

| Н   | 0.50   | 0.60   | 0.020  | 0.024 |  |

| J   | 0.09   | 0.20   | 0.004  | 0.008 |  |

| J1  | 0.09   | 0.16   | 0.004  | 0.006 |  |

| Κ   | 0.19   | 0.30   | 0.007  | 0.012 |  |

| K1  | 0.19   | 0.25   | 0.007  | 0.010 |  |

| Г   | 6.40   | BSC    | 0.252  | BSC   |  |

| М   | 0 °    | 8 °    | 0 °    | 8 °   |  |

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative