# Low Skew CMOS PLL 68060 Clock Driver

MC88LV926

The MC88LV926 Clock Driver utilizes phase-locked loop technology to lock its low skew outputs' frequency and phase onto an input reference clock. It is designed to provide clock distribution for CISC microprocessor or single processor RISC systems. The RST\_IN/RST\_OUT(LOCK) pins provide a processor reset function designed specifically for the MC68/EC/LC030/040/060 microprocessor family. To support the 68060 processor, the 88LV926 operates from a 3.3 V supply.

The PLL allows the high current, low skew outputs to lock onto a single clock input and distribute it to multiple locations on a board. The PLL also allows the MC88LV926 to multiply a low frequency input clock and distribute it locally at a higher (2X) system frequency.

#### **Features**

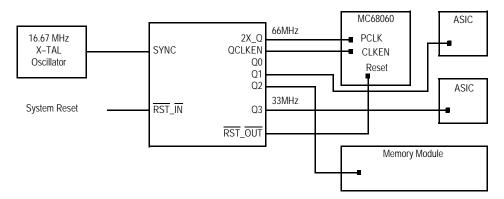

- 2X\_Q Output Meets All Requirements of the 50 and 66 MHz 68060 Microprocessor PCLK Input Specifications

- Low Voltage 3.3 V V<sub>CC</sub>

- Three Outputs (Q0-Q2) with Output-Output Skew <500 ps

- CLKEN Output for Half Speed Bus Applications

- The Phase Variation from Part-to-Part Between SYNC and the 'Q' Outputs Is Less than 600 ps (Derived from the T<sub>PD</sub> Specification, Which Defines the Part-to-Part Skew)

- SYNC Input Frequency Range from 5.0 MHz to 2X\_Q F<sub>Max</sub>/4

- All Outputs Have ± 36 mA Drive (Equal High and Low) CMOS Levels

- Can Drive Either CMOS or TTL Inputs. All Inputs Are TTL-Level Compatible with V<sub>CC</sub> = 3.3 V

- Test Mode Pin (PLL\_EN) Provided for Low Frequency Testing

- 20-Lead SOIC Pb-Free Package Available

LOW SKEW CMOS PLL 68080 CLOCK DRIVER

DW SUFFIX 20-LEAD PLASTIC SOIC PACKAGE CASE 751D-06

EG SUFFIX 20-LEAD PLASTIC SOIC PACKAGE Pb-FREE PACKAGE CASE 751D-06

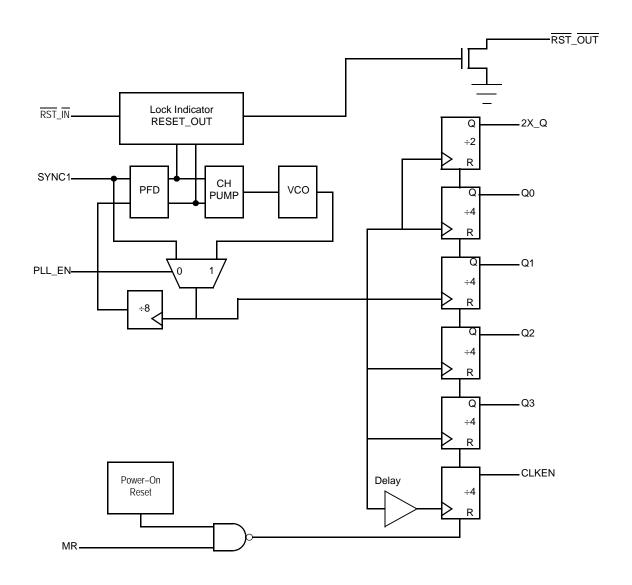

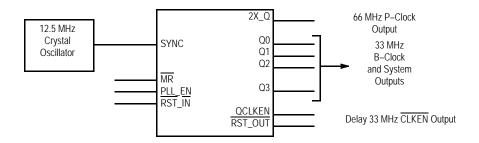

Three 'Q' outputs (Q0-Q2) are provided with less than 500 ps skew between their rising edges. A  $2X_Q$  output runs at twice the 'Q' output frequency. The  $2X_Q$  output is ideal for 68060 systems which require a 2X processor clock input, and it meets the tight duty cycle spec of the 50 and 66 MHz 68060. The QCLKEN output is designed to drive the  $\overline{\text{CLKEN}}$  input of the 68060 when the bus logic runs at half of the microprocessor clock rate. The QCLKEN output is skewed relative to the  $2X_Q$  output to ensure that  $\overline{\text{CLKEN}}$  setup and hold times of the 68060 are satisfied. A Q/2 frequency is fed back internally, providing a fixed 2X multiplication from the 'Q' outputs to the SYNC input. Since the feedback is done internally (no external feedback pin is provided) the input/output frequency relationships are fixed. The  $\overline{Q3}$  output provides an inverted clock output to allow flexibility in the clock tree design.

In normal phase-locked operation the PLL\_EN pin is held high. Pulling the PLL\_EN pin low disables the VCO and puts the 88LV926 in a static 'test mode'. In this mode there is no frequency limitation on the input clock, which is necessary for a low frequency board test environment.

The RST\_OUT(LOCK) pin doubles as a phase-lock indicator. When the RST\_IN pin is held high, the open drain RST\_OUT pin will be pulled actively low until phase-lock is achieved. When phase-lock occurs, the RST\_OUT(LOCK) is released and a pull-up resistor will pull the signal high. To give a processor reset signal, the RST\_IN pin is toggled low, and the RST\_OUT(LOCK) pin will stay low for 1024 cycles of the 'Q' output frequency after the RST\_IN pin is brought back high.

#### Description of the RST\_IN/RST\_OUT(LOCK) Functionality

The RST\_IN and RST\_OUT(LOCK) pins provide a 68030/040/060 processor reset function, with the RST\_OUT pin also acting as a lock indicator. If the RST\_IN pin is held high during system power-up, the RST\_OUT pin will be in the low state until steady state phase/frequency lock to the input reference is achieved. 1024 'Q' output cycles after phase-lock is achieved the RST\_OUT(LOCK) pin will go into a high impedance state, allowing it to be pulled high by an external pull-up resistor (see the AC/DC specs for the characteristics of the RST\_OUT(LOCK) pin). If the RST\_IN pin is held low during power-up, the RST\_OUT(LOCK) pin will remain low.

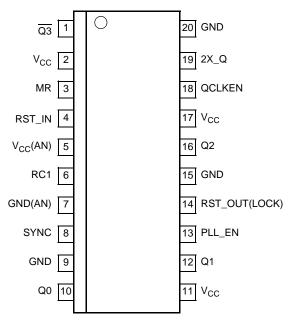

Figure 1. Pinout: 20-Lead Wide SOIC Package (Top View)

### Description of the RST\_IN/RST\_OUT(LOCK) Functionality (continued)

After the system start-up is complete and the 88LV926 is phase-locked to the SYNC input signal (RST\_OUT high), the processor reset functionality can be utilized. When the RST\_IN pin is toggled low (min. pulse width=10 nS), RST\_OUT(LOCK) will go to the low state and remain there for 1024 cycles of the 'Q' output frequency (512 SYNC cycles). During the time in which the RST\_OUT(LOCK) is actively pulled low, all the 88LV926 clock outputs will continue operating correctly and in a locked condition to the SYNC input (clock signals to the 68030/040/060 family of processors must continue while the processor is in reset). A propagation delay after the 1024th cycle RST\_OUT(LOCK) goes back to the high impedance state to be pulled high by the resistor.

Power Supply Ramp Rate Restriction for Correct 030/040 Processor Reset Operation During System Start-up

Because the RST OUT(LOCK) pin is an indicator of phase-lock to the reference source, some constraints must be placed on the power supply ramp rate to make sure the RST\_OUT(LOCK) signal holds the processor in reset during system start-up (power-up). With the recommended loop filter values (see Figure 7) the lock time is approximately 10ms. The phase-lock loop will begin attempting to lock to a reference source (if it is present) when V<sub>CC</sub> reaches 2 V. If the V<sub>CC</sub> ramp rate is significantly slower than 10 ms, then the PLL could lock to the reference source, causing RST\_OUT(LOCK) to go high before the 88LV926 and 030/ 040 processor is fully powered up, violating the processor reset specification. Therefore, if it is necessary for the RST\_IN pin to be held high during power-up, the V<sub>CC</sub> ramp rate must be less than 10 mS for proper 68030/040/060 reset operation.

This ramp rate restriction can be ignored if the RST\_IN pin can be held low during system start-up (which holds RST\_OUT low). The RST\_OUT(LOCK) pin will then be pulled back high 1024 cycles after the RST\_IN pin goes high.

**Table 1. Capacitance and Power Specifications**

| Symbol          | Parameter                                                          | Value Type                                   | Unit | Test Conditions                     |

|-----------------|--------------------------------------------------------------------|----------------------------------------------|------|-------------------------------------|

| C <sub>IN</sub> | Input Capacitance                                                  | 4.5 <sup>(1)</sup>                           | pF   | V <sub>CC</sub> = 3.3 V             |

| $C_{PD}$        | Power Dissipation Capacitance                                      | 40 <sup>(1)</sup>                            | pF   | V <sub>CC</sub> = 3.3 V             |

| PD <sub>1</sub> | Power Dissipation at 33MHz With 50Ω<br>Thevenin Termination        | 15mW/Output <sup>(1)</sup><br>90mW/Device    | mW   | V <sub>CC</sub> = 3.3 V<br>T = 25°C |

| PD <sub>2</sub> | Power Dissipation at 33MHz With 50Ω<br>Parallel Termination to GND | 37.5mW/Output <sup>(1)</sup><br>225mW/Device | mW   | V <sub>CC</sub> = 3.3 V<br>T = 25°C |

<sup>1.</sup> Value at  $V_{CC} = 3.3 \text{ V TBD}$

Table 2. Maximum Ratings<sup>(1)</sup>

| Symbol                             | Parameter                                        | Limits                       | Unit |

|------------------------------------|--------------------------------------------------|------------------------------|------|

| V <sub>CC</sub> , AV <sub>CC</sub> | DC Supply Voltage Referenced to GND              | -0.5 to 7.0                  | V    |

| V <sub>in</sub>                    | DC Input Voltage (Referenced to GND)             | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>out</sub>                   | DC Output Voltage (Referenced to GND)            | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>in</sub>                    | DC Input Current, Per Pin                        | ±20                          | mA   |

| l <sub>out</sub>                   | DC Output Sink/Source Current, Per Pin           | ±50                          | mA   |

| I <sub>CC</sub>                    | DC V <sub>CC</sub> or GND Current Per Output Pin | ±50                          | mA   |

| T <sub>stg</sub>                   | Storage Temperature                              | -65 to +150                  | °C   |

<sup>1.</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

**Table 3. Recommended Operating Conditions**

| Symbol           | Parameter                     | Limits               | Unit |

|------------------|-------------------------------|----------------------|------|

| V <sub>CC</sub>  | Supply Voltage                | 3.3 ±0.3             | V    |

| V <sub>in</sub>  | DC Input Voltage              | 0 to V <sub>CC</sub> | V    |

| V <sub>out</sub> | DC Output Voltage             | 0 to V <sub>CC</sub> | V    |

| T <sub>A</sub>   | Ambient Operating Temperature | 0 to 70              | °C   |

| ESD              | Static Discharge Voltage      | > 1500               | V    |

Table 4. DC Characteristics ( $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ;  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ )<sup>(1)</sup>

| Symbol           | Parameter                                       | V <sub>CC</sub> | Guaranteed Limits  | Unit | Condition                                                                  |

|------------------|-------------------------------------------------|-----------------|--------------------|------|----------------------------------------------------------------------------|

| V <sub>IH</sub>  | Minimum High Level Input Voltage <sup>(1)</sup> | 3.0<br>3.3      | 2.0<br>2.0         | V    | V <sub>OUT</sub> = 0.1V or<br>V <sub>CC</sub> – 0.1V                       |

| V <sub>IL</sub>  | Minimum Low Level Input Voltage                 | 3.0<br>3.3      | 0.8<br>0.8         | V    | V <sub>OUT</sub> = 0.1V or<br>V <sub>CC</sub> - 0.1V                       |

| V <sub>OH</sub>  | Minimum High Level Output Voltage               | 3.0<br>3.3      | 2.2<br>2.5         | V    | $V_{IN} = V_{IH}$ or $V_{IL} = -24$ mA $I_{OH} = -24$ mA                   |

| V <sub>OL</sub>  | Minimum Low Level Output Voltage                | 3.0<br>3.3      | 0.55<br>0.55       | V    | $V_{IN} = V_{IH}$ or $V_{IL} = +24\text{mA}^{(2)}$ $I_{OH} = +24\text{mA}$ |

| I <sub>IN</sub>  | Maximum Input Leakage Current                   | 3.3             | ±1.0               | μА   | $V_I = V_{CC}$ , GND                                                       |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input                  | 3.3             | 2.0 <sup>(3)</sup> | mA   | $V_{I} = V_{CC} - 2.1V$                                                    |

| I <sub>OLD</sub> | Minimum Dynamic <sup>(4)</sup> Output Current   | 3.3             | 50                 | mA   | V <sub>OLD</sub> = 1.25V Max                                               |

| I <sub>OHD</sub> |                                                 | 3.3             | -50                | mA   | V <sub>OHD</sub> = 2.35 Min                                                |

| Icc              | Maximum Quiescent Supply Current                | 3.3             | 750                | μА   | $V_I = V_{CC}$ , GND                                                       |

<sup>1.</sup> The MC88LV926 can also be operated from a 3.3V supply.  $V_{OH}$  output levels will vary 1:1 with  $V_{CC}$ , input levels and current specs will be unchanged, except  $V_{IH}$ ; when  $V_{CC} > 4.0$  volts,  $V_{IH}$  minimum level is 2.7 volts.

<sup>2.</sup>  $I_{OL}$  is +12mA for the  $\overline{RST}$ \_ $\overline{OUT}$  output.

<sup>3.</sup> Maximum test duration 2.0ms, one output loaded at a time.

<sup>4.</sup> The PLL\_EN input pin is not guaranteed to meet this specification.

Figure 2. MC88LV926 Logic Block Diagram

**Table 5. Sync Input Timing Requirements**

| Symbol                               | Parameter                                       | Minimum                   | Maximum            | Unit |

|--------------------------------------|-------------------------------------------------|---------------------------|--------------------|------|

| t <sub>RISE/FALL</sub><br>SYNC Input | Rise/Fall Time, SYNC Input<br>From 0.8V to 2.0V | -                         | 5.0                | ns   |

| t <sub>CYCLE</sub> ,<br>SYNC Input   | Input Clock Period SYNC Input <sup>(1)</sup>    | 1<br>f <sub>2X_Q</sub> /4 | 200 <sup>(1)</sup> | ns   |

| Duty Cycle                           | Duty Cycle, SYNC Input                          | 50% ± 25%                 |                    |      |

<sup>1.</sup> When  $\rm V_{CC}$  > 4.0 volts, Maximum SYNC Input Period is 125 ns.

Table 6. Frequency Specifications (T<sub>A</sub> = 0°C to 70°C; V<sub>CC</sub> = 3.3 V  $\pm$  0.3 V

| Symbol      | Parameter                                     | Guaranteed Minimum | Unit |

|-------------|-----------------------------------------------|--------------------|------|

| Fmax (2X_Q) | Maximum Operating Frequency, 2X_Q Output      | 66                 | MHz  |

| Fmax ('Q')  | Maximum Operating Frequency,<br>Q0–Q3 Outputs | 33                 | MHz  |

NOTE: Maximum Operating Frequency is guaranteed with the 88LV926 in a phase-locked condition.

Table 7. AC Characteristics (T<sub>A</sub> =  $0^{\circ}$ C to  $70^{\circ}$ C;  $V_{CC}$  = 3.3V  $\pm$  0.3V

| Symbol                                                      | Parameter                                                                               | Minimum                                  | Maximum                             | Unit | Condition                                                                         |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------|------|-----------------------------------------------------------------------------------|

| t <sub>RISE/FALL</sub><br>All Outputs                       | Rise/Fall Time, into 50Ω Load                                                           | 0.3                                      | 1.6                                 | ns   | t <sub>RISE</sub> - 0.8 V to 2.0 V<br>t <sub>FALL</sub> - 2.0 V to 0.8 V          |

| t <sub>RISE/FALL</sub><br>2X_Q Output                       | Rise/Fall Time into a 50Ω Load                                                          | 0.5                                      | 1.6                                 | ns   | t <sub>RISE</sub> - 0.8 V to 2.0 V<br>t <sub>FALL</sub> - 2.0 V to 0.8 V          |

| t <sub>pulse width(a)</sub> (1)<br>(Q0, Q1, Q2, Q3)         | Output Pulse Width<br>Q0, Q1, Q2, Q3 at 1.65V                                           | 0.5t <sub>cycle</sub> – 0.5              | 0.5t <sub>cycle</sub> + 0.5         | ns   | $50 \Omega$ Load Terminated to V <sub>CC</sub> / 2 (See Application Note 3)       |

| t <sub>pulse width(b)</sub> <sup>(1)</sup><br>(2X_Q Output) | Output Pulse Width 2X_Q at 1.65V                                                        | 0.5t <sub>cycle</sub> – 0.5              | 0.5t <sub>cycle</sub> + 0.5         | ns   | $50 \Omega$ Load Terminated to V <sub>CC</sub> / 2 (See Application Note 3)       |

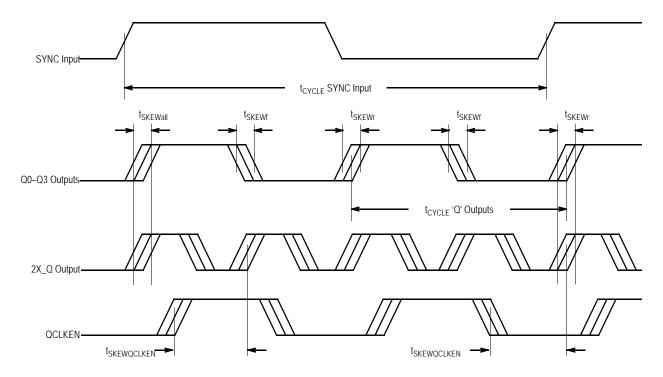

| t <sub>SKEWr</sub> <sup>(2)</sup><br>(Rising)               | Output-to-Output Skew<br>Between Outputs Q0-Q2<br>(Rising Edge Only)                    | -                                        | 500                                 | ps   | Into a $50\Omega$ Load Terminated to $V_{CC}/2$ (See Timing Diagram in Figure 6)  |

| t <sub>SKEWf</sub> <sup>(2)</sup><br>(Falling)              | Output-to-Output Skew<br>Between Outputs Q0-Q2<br>(Falling Edge Only)                   | -                                        | 1.0                                 | ns   | Into a 50 $\Omega$ Load Terminated to $V_{CC}/2$ (See Timing Diagram in Figure 6) |

| t <sub>SKEWall</sub> <sup>(2)</sup>                         | Output-to-Output Skew 2X_Q, Q0-Q2, Q3                                                   | -                                        | 750                                 | ps   | Into a 50 $\Omega$ Load Terminated to $V_{CC}/2$ (See Timing Diagram in Figure 6) |

| t <sub>SKEW</sub> QCLKEN <sup>(1)</sup> (2)                 | Output-to-Output Skew QCLKEN to 2X_Q                                                    | 9.7 <sup>(3)</sup><br>7.0 <sup>(3)</sup> | -                                   | ns   | Into a 50 $\Omega$ Load Terminated to $V_{CC}/2$ (See Timing Diagram in Figure 6) |

| t <sub>LOCK</sub> <sup>(4)</sup>                            | Phase–Lock Acquisition Time,<br>All Outputs to SYNC Input                               | 1                                        | 10                                  | ms   |                                                                                   |

| t <sub>PHL</sub> MR – Q <sup>(1)</sup>                      | Propagation Delay, MR to Any Output (High-Low)                                          | 1.5                                      | 13.5                                | ns   | Into a 50 Ω Load<br>Terminated to V <sub>CC</sub> /2                              |

| t <sub>REC</sub> , MR to<br>SYNC <sup>(1)(5)</sup>          | Reset Recovery Time rising $\overline{\rm MR}$ edge to falling SYNC edge <sup>(6)</sup> | 9                                        | -                                   | ns   |                                                                                   |

| t <sub>W</sub> , MR LOW <sup>(1) (5)</sup>                  | Minimum Pulse Width, MR input Low                                                       | 5                                        | -                                   | ns   |                                                                                   |

| t <sub>W</sub> , RST_IN<br>LOW <sup>(1)</sup>               | Minimum Pulse Width, RST_IN Low                                                         | 10                                       | -                                   | ns   | When in Phase–Lock                                                                |

| t <sub>PZL</sub> <sup>(1)</sup>                             | Output Enable Time<br>RST_IN Low to RST_OUT Low                                         | 1.5                                      | 16.5                                | ns   | See Application Notes, Note 5                                                     |

| t <sub>PLZ</sub> <sup>(1)</sup>                             | Output Enable Time<br>RST_IN High to RST_OUT High Z                                     | 1016 'Q' Cycles<br>(508 Q/2 Cycles)      | 1024 'Q' Cycles<br>(512 Q/2 Cycles) | ns   | See Application Notes, Note 5                                                     |

<sup>1.</sup> These specifications are not tested, they are guaranteed by statistical characterization. See Application Note 1 for a discussion of this methodology.

<sup>2.</sup> Under equally loaded conditions and at a fixed temperature and voltage.

<sup>3.</sup> Guaranteed that QCLKEN will meet the setup and hold time requirement of the 68060.

<sup>4.</sup> With V<sub>CC</sub> fully powered–on:  $t_{CLOCK}$  Max is with C1 = 0.1  $\mu F$ ;  $t_{LOCK}$  Min is with C1 = 0.01  $\mu F$ .

<sup>5.</sup> Specification is valid only when the PLL\_EN pin is low.

<sup>6.</sup> See Application Notes, Note 4 for the distribution in time of each output referenced to SYNC.

#### **APPLICATION NOTES**

- Statistical characterization techniques were used to guarantee those specifications which cannot be measured on the ATE. MC88LV926 units were fabricated with key transistor properties intentionally varied to create a 14 cell designed experimental matrix. IC performance was characterized over a range of transistor properties (represented by the 14 cells) in excess of the expected process variation of the wafer fabrication area. IC performance to each specification and fab variation were used to set performance limits of ATE testable specifications within those which are to be guaranteed by statistical characterization. In this way, all units passing the ATE test will meet or exceed the nontested specifications limits.

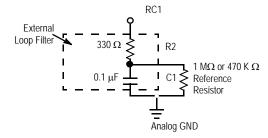

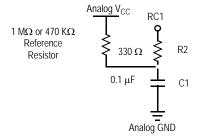

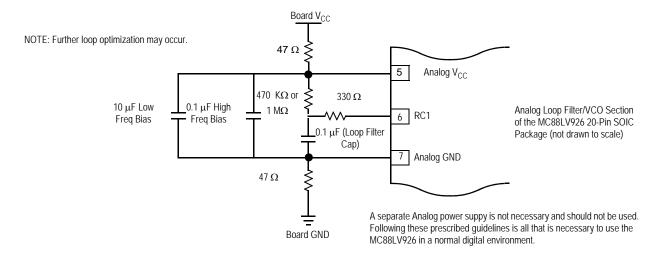

- 2. A 470 K $\Omega$  or 1 M $\Omega$  resistor tied to either Analog V<sub>CC</sub> or Analog GND, as shown in Figure 3, is required to

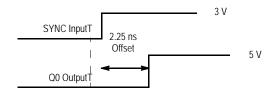

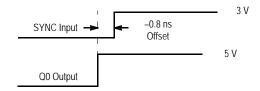

ensure no jitter is present on the MC88LV926 outputs. This technique causes a phase offset between the SYNC input and the Q0 output, measured at the pins. The t<sub>PD</sub> spec describes how this offset varies with process, temperature, and voltage. The specs were arrived at by measuring the phase relationship for the 14 lots described in note 1 while the part was in phase-locked operation. The actual measurements were made with a 10 MHz SYNC input (1.0 ns edge rate from 0.8 V to 2.0 V). The phase measurements were made at 1.5 V. See Figure 3 for a graphical description.

Two specs (t<sub>RISE/FALL</sub> and t<sub>PULSE</sub> Width 2X\_Q output, see AC Specifications) guarantee that the MC88LV926 meets the 33 MHz and 66 MHz 68060 P-Clock input specification.

With the 470 K $\Omega$  resistor tied in this fashion, the  $T_{PD}$  specification measured at the input pins is:

$t_{PD}$  = 2.25 ns  $\pm$  1.0 ns (Typical Values)

With the 470 K $\Omega$  resistor tied in this fashion, the  $T_{PD}$  specification measured at the input pin is:

$t_{PD} = -0.80 \text{ ns} \pm 0.30 \text{ ns}$

Figure 3. Depiction of the Fixed SYNC to Q0 Offset (tpD) Which Is Present When a 470 K $\Omega$  Resistor Is Tied to V<sub>CC</sub> or Ground

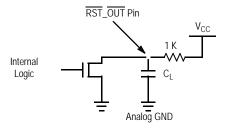

Figure 4. RST\_OUT Test Circuit

Figure 5. Logical Representation of the MC88LV926 With Input/Output Frequency Relationships

#### NOTES:

- The MC88LV926 aligns rising edges of the outputs and the SYNC input, therefore the SYNC input does not require a 50% duty cycle.

- All skew specs are measured between the V<sub>CC</sub>/2 crossing point of the appropriate output edges. All skews are specified

as "windows", not as a ± deviation around a center point.

#### Figure 6. Output/Input Switching Waveforms and Timing Relationships

- 4. The  $t_{PD}$  spec includes the full temperature range from 0°C to 70°C and the full  $V_{CC}$  range from 3.0 V to 3.3 V. If the  $\Delta T$  and  $\Delta V_{CC}$  is a given system are less than the specification limits, the  $t_{PD}$  spec window will be reduced.

- The RST\_OUT pin is an open drain N-Channel output. Therefore an external pull-up resistor must be provide

to pull up the  $\overline{RST}$ \_ $\overline{OUT}$  pin when it goes into the high impedance state (after the MC88LV926 is phase-locked to the reference input with  $\overline{RST}$ \_ $\overline{IN}$  held high or 1024 'Q' cycles after the  $\overline{RST}$ \_ $\overline{IN}$  pin goes high when the part is locked). In the t<sub>PLZ</sub> and t<sub>PZL</sub> specifications, a 1 K $\Omega$  resistor is used as a pull-up as shown in Figure 3.

### NOTES CONCERNING LOOP FILTER AND BOARD LAYOUT ISSUES

- Figure 7 shows a loop filter and analog isolation scheme which will be effective in most applications. The following guidelines should be followed to ensure stable and jitter-free operation:

- 1a. All loop filter and analog isolation components should be tied as close to the package as possible. Stray current passing through the parasitics of long traces can cause undesirable voltage transients at the RC1 pin.

- 1b. The 47  $\Omega$  resistors, the 10  $\mu F$  low frequency bypass capacitor, and the 0.1  $\mu F$  high frequency bypass capacitor form a wide bandwidth filter that will make the 88LV926 PLL insensitive to voltage transients from the system digital  $V_{CC}$  supply and ground planes. This filter will typically ensure that a 100mV step deviation on the digital  $V_{CC}$  supply will cause no more than a 100 ps phase deviation on the 88LV926 outputs. A 250 mV step deviation on  $V_{CC}$  using the recommended filter values will cause no more than a 250 ps phase deviation; if a 25  $\mu F$  bypass capacitor is used (instead of 10  $\mu F$ ) a 250 mV  $V_{CC}$  step will cause no more than a 100 ps phase deviation.

If good bypass techniques are used on a board design near components which may cause digital  $V_{CC}$  and ground noise, the above described  $V_{CC}$  step deviations should not occur at the 88LV926's digital  $V_{CC}$  supply. The purpose of the bypass filtering scheme shown in

- Figure 6 is to give the 88LV926 additional protection from the power supply and ground plane transients that can occur in a high frequency, high speed digital system.

- 1c. There are no special requirements set forth for the loop filter resistors (470 K and 33  $0\Omega$ ). The loop filter capacitor (0.1uF) can be a ceramic chip capacitor, the same as a standard bypass capacitor.

- 1d. The 470 K reference resistor injects current into the internal charge pump of the PLL, causing a fixed offset between the outputs and the SYNC input. This also prevents excessive jitter caused by inherent PLL deadband. If the VCO (2X\_Q output) is running above 40 MHz, the 470 K resistor provides the correct amount of current injection into the charge pump (2–3  $\mu$ A). If the VCO is running below 40 MHz, a 1 M $\Omega$  reference resistor should be used (instead of 470 K).

- 2. In addition to the bypass capacitors used in the analog filter of Figure 7, there should be a 0.1  $\mu F$  bypass capacitor between each of the other (digital) four  $V_{CC}$  pins and the board ground plane. This will reduce output switching noise caused by the 88LV926 outputs, in addition to reducing potential for noise in the 'analog' section of the chip. These bypass capacitors should also be tied as close to the 88LV926 package as possible.

Figure 7. Recommended Loop Filter and Analog Isolation Scheme for the MC88LV926

Figure 8. Typical MC88LV926/MC68060 System Configuration

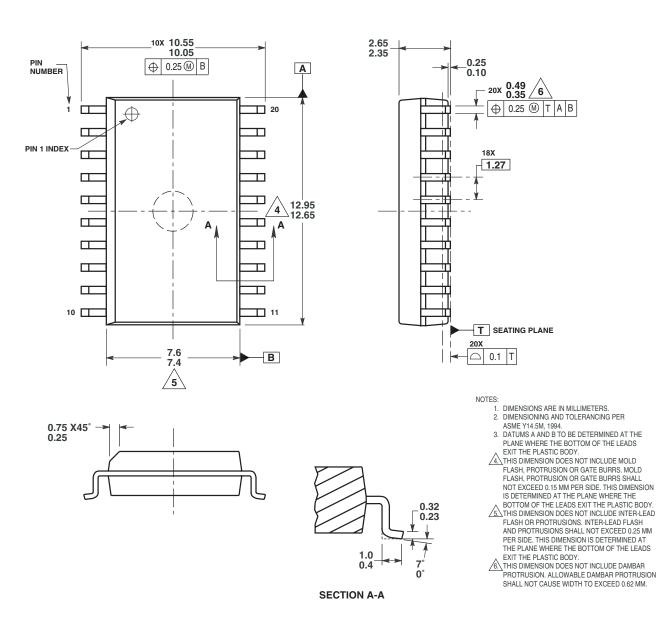

#### **PACKAGE DIMENSIONS**

CASE 751D-06 ISSUE H 20-LEAD SOIC PACKAGE

### Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339