# TWO-CHANNEL, 20-BIT, AC'97 2.3 CODECS WITH HEADPHONE STAC9752/9753 DRIVE, SPDIF OUTPUT MICROPHONE & JACK SENSING

# **Description**

IDT's STAC9752/9753 are general purpose 20-bit, full duplex, audio CODECs conforming to the analog component specification of AC'97 (Audio CODEC 97 Component Specification Rev. 2.3). The STAC9752/9753 incorporate IDT's proprietary  $\Sigma\Delta$  technology to achieve a DAC SNR in excess of 90dB. The DACs, ADCs and mixer are integrated with analog I/Os, which include four analog line-level stereo inputs, two analog line-level mono inputs, two stereo outputs, and one mono output channel. The STAC9752/9753 include digital output capability for support of modern PC systems with an output that supports the SPDIF format. The STAC9752/9753 are standard 2-channel stereo CODECs. With IDT's headphone capability, headphones can be driven without an external amplifier. The STAC9752/9753 may be used as a secondary or tertiary CODECs, with STAC9700/21/44/56/ 08/84/50/66 as the primary, in a multiple CODEC configuration conforming to the AC'97 Rev. 2.3 specification. This configuration can provide the true six-channel, AC-3 playback required for DVD applications. The STAC9752/9753 communicate via the five AC-Link lines to any digital component of AC'97, providing flexibility in the audio system design. Packaged in an AC'97 compliant 48-pin TQFP, the STAC9752/9753 can be placed on the motherboard, daughter boards, PCI, AMR, CNR, MDC or ACR cards.

#### **Features**

- High performance Σ∆ technology

- AC'97 Rev 2.3 compliant

- 20-bit full duplex stereo ADCs, DACs

- Independent sample rates for ADCs & DACs

- 5-wire AC-Link protocol compliance

- 20-bit SPDIF Output

- Internal Jack Sensing on Headphone and Line\_Out

- Internal Microphone Input Sensing

- Digital PC Beep Option

- Extended AC'97 2.3 Paging Registers

- Adjustable VREF amplifier

- Digital-ready status

- General purpose I/Os

- Crystal Elimination Circuit

- Headphone drive capability (50 mW)

- 0dB, 10dB, 20dB, and 30dB microphone boost capability

- +3.3 V (STAC9753) and +5 V (STAC9752) analog power supply options

- Pin compatible with the STAC9700, STAC9721, STAC9756

- 100% pin compatible with STAC9750 and STAC9766

- IDT Surround (SS3D) Stereo Enhancement

- Energy saving dynamic power modes

- Multi-CODEC option (Intel AC'97 rev 2.3)

- Six analog line-level inputs

- 90dB SNR Line to Line

- SNR > 89dB through Mixer and DAC

# **TABLE OF CONTENTS**

| 1. PRODUCT BRIEF                                                       | 7  |

|------------------------------------------------------------------------|----|

| 1.1. Description                                                       |    |

| 1.2. STAC9752/9753 Block Diagram                                       |    |

| 1.3. Key Specifications                                                |    |

| 1.4. Related Materials                                                 |    |

| 1.5. Additional Support                                                |    |

| 2. CHARACTERISTICS AND SPECIFICATIONS                                  |    |

| 2.1. Electrical Specifications                                         |    |

| 2.1.1. Absolute Maximum Ratings                                        |    |

| 2.1.2. Recommended Operation Conditions                                |    |

| 2.1.2. Recommended Operation Conditions  2.1.3. Power Consumption      |    |

| 2.1.4. AC-Link Static Digital Specifications                           |    |

| 2.1.5. STAC9752 5 V Analog Performance Characteristics                 |    |

| 2.1.6. STAC9752 3 V Analog Performance Characteristics                 |    |

| 2.1. AC Timing Characteristics                                         |    |

| 2.2.1. Cold Reset                                                      |    |

| 2.2.2. Warm Reset                                                      |    |

| 2.2.3. Clocks                                                          |    |

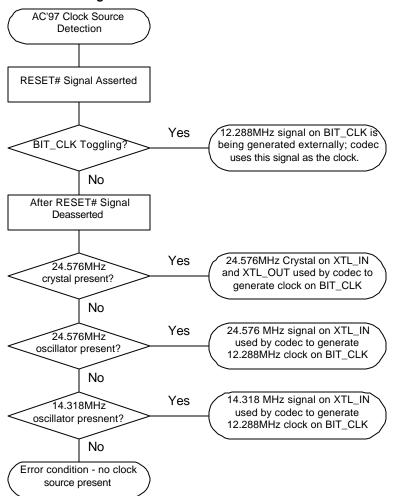

| 2.2.4. STAC9752/9753 Crystal Elimination Circuit and Clock Frequencies |    |

| 2.2.5. Data Setup and Hold                                             |    |

| 2.2.6. Signal Rise and Fall Times                                      |    |

| 2.2.7. AC-Link Low Power Mode Timing                                   |    |

| 2.2.8. ATE Test Mode                                                   |    |

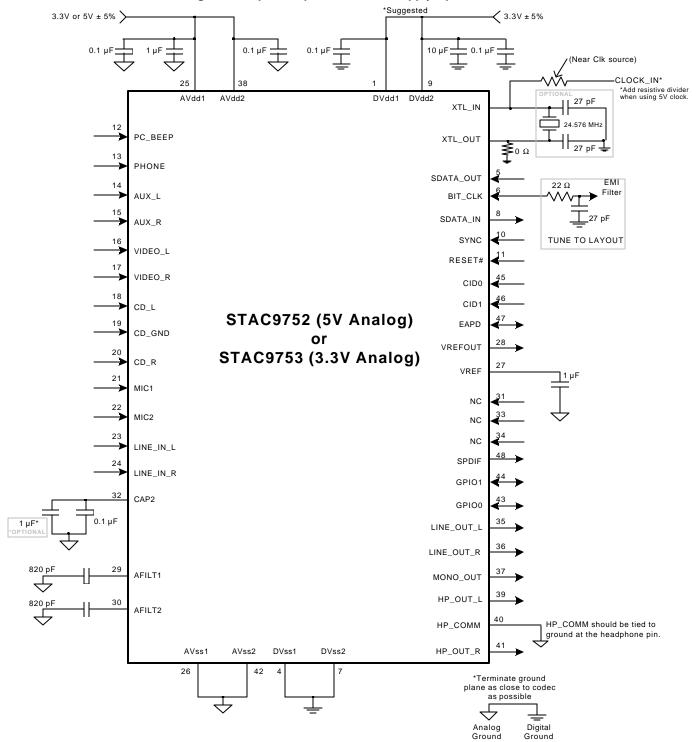

| 3. TYPICAL CONNECTION DIAGRAM                                          |    |

| 3.1. Slit Independent Power Supply Operation                           |    |

| 4. CONTROLLER, CODEC AND AC-LINK                                       |    |

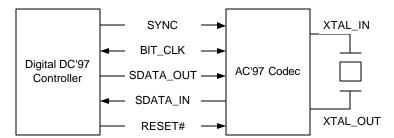

| 4.1. AC-Link Physical Interface                                        |    |

| 4.2. Controller to Single CODEC                                        |    |

| 4.3. Controller to Multiple CODECs                                     |    |

| 4.3.1. Primary CODEC Addressing                                        |    |

| 4.3.2. Secondary CODEC Addressing                                      |    |

| 4.3.3. CODEC ID Strapping                                              |    |

| 4.4. Clocking for Multiple CODEC Implementations                       |    |

| 4.5. STAC9752/9753 as a Primary CODEC                                  |    |

| 4.5.1. STAC9752/9753 as a Secondary CODEC                              |    |

| 4.6. AC-Link Power Management                                          |    |

| 4.6.1. Powering down the AC-Link                                       |    |

| 4.6.2. Waking up the AC-Link                                           |    |

| 4.6.3. CODEC Reset                                                     |    |

| 5. AC-LINK DIGITAL INTERFACE                                           | 29 |

| 5.1. Overview                                                          |    |

| 5.2. AC-Link Serial Interface Protocol                                 | 30 |

| 5.2.1. AC-Link Variable Sample Rate Operation                          | 30 |

| 5.2.2. Variable Sample Rate Signaling Protocol                         |    |

| 5.2.3. Primary and Secondary CODEC Register Addressing                 |    |

| 5.3. AC-Link Output Frame (SDATA_OUT)                                  | 32 |

| 5.3.1. Slot 0: TAG / CODEC ID                                          | 34 |

| 5.3.2. Slot 1: Command Address Port                                    |    |

| 5.3.3. Slot 2: Command Data Port                                       | 35 |

| 5.3.4. Slot 3: PCM Playback Left Channel                               |    |

| 5.3.5. Slot 4: PCM Playback Right Channel                              |    |

| 5.3.6. Slot 5: Modem Line 1 Output Channel                             |    |

| 5.3.7. Slot 6 - 11: DAC                                                | 35 |

2

| 5.3.8. Slot 12: Audio GPIO Control Channel                       | 36 |

|------------------------------------------------------------------|----|

| 5.4. AC-Link Input Frame (SDATA_IN)                              | 36 |

| 5.4.1. Slot 0: TAG                                               | 37 |

| 5.4.2. Slot 1: Status Address Port / SLOTREQ signalling bits     | 37 |

| 5.4.3. Slot 2: Status Data Port                                  | 38 |

| 5.4.4. Slot 3: PCM Record Left Channel                           | 38 |

| 5.4.5. Slot 4: PCM Record Right Channel                          | 38 |

| 5.4.6. Slot 5: Modem Line 1 ADC                                  |    |

| 5.4.7. Slot 6 - 9: ADC                                           |    |

| 5.4.8. Slots 7 & 8: Vendor Reserved                              | 39 |

| 5.4.9. Slot 10 & 11: ADC                                         |    |

| 5.4.10. Slot 12: Reserved                                        |    |

| 5.5. AC-Link Interoperability Requirements and Recommendations   | 40 |

| 5.5.1. "Atomic slot" Treatment of Slot 1 Address and Slot 2 Data |    |

| 5.6. Slot Assignments for Audio                                  |    |

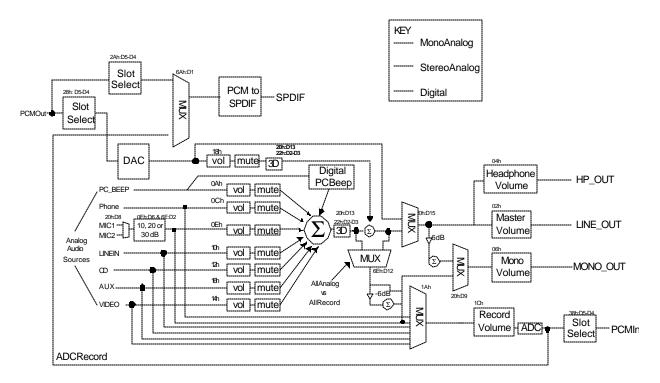

| 6. STAC9752/9753 MIXER                                           | 43 |

| 7. MIXER FUNCTIONAL DIAGRAMS                                     |    |

| 7.1. Analog Mixer Input                                          |    |

| 7.2. Mixer Analog Output                                         |    |

| 7.3. SPDIF Digital Mux                                           |    |

| 7.4. PC Beep Implementation                                      |    |

| 7.4.1. Analog PC Beep                                            |    |

| 7.4.2. Digital PC Beep                                           |    |

| 8. PROGRAMMING REGISTERS                                         |    |

| 8.1. Register Descriptions                                       |    |

| 8.1.1. Reset (00h)                                               |    |

| 8.1.2. Master Volume Registers (02h)                             |    |

| 8.1.3. Headphone Volume Registers (04h)                          |    |

| 8.1.4. Master Volume MONO (06h)                                  |    |

| 8.1.5. PC BEEP Volume (0Ah)                                      |    |

| 8.1.6. Phone Volume (Index 0Ch)                                  |    |

| 8.1.7. Mic Volume (Index 06H)                                    |    |

| 8.1.8. LineIn Volume (Index 10h)                                 |    |

| 8.1.9. CD Volume (Index 12h)                                     |    |

| 8.1.10. Video Volume (Index 14h)                                 |    |

| 8.1.11. Aux Volume (Index 16h)                                   |    |

| 8.1.12. PCMOut Volume (Index 18h)                                |    |

| 8.1.13. Record Select (1Ah)                                      |    |

| 8.1.14. Record Gain (1Ch)                                        |    |

| 8.1.15. General Purpose (20h)                                    |    |

| 8.1.16. 3D Control (22h)                                         |    |

| 8.1.17. Audio Interrupt and Paging (24h)                         |    |

| 8.1.18. Powerdown Ctrl/Stat (26h)                                |    |

| 8.1.19. Extended Audio ID (28h)                                  |    |

| 8.1.20. Extended Audio Control/Status (2Ah)                      |    |

| 8.1.21. PCM DAC Rate Registers (2Ch and 32h)                     |    |

| 8.1.22. PCM DAC Rate (2Ch)                                       |    |

| 8.1.23. PCM LR ADC Rate (32h)                                    |    |

| 8.1.24. SPDIF Control (3Ah)                                      |    |

| 8.2. General Purpose Input & Outputs                             |    |

| 8.2.1. EAPD                                                      |    |

| 8.2.2. GPIO Pin Definitions                                      |    |

| 8.2.3. GPIO Pin Implementation                                   |    |

| 8.2.4. Extended Modem Status and Control Register (3Eh)          |    |

| 8.2.5. GPIO Pin Configuration Register (4Ch)                     |    |

| 5.2.5. 51 15 1 iii 55iiiigulatioii (tegistei (4011)              |    |

3

|     | 8.2.6. GPIO Pin Polarity/Type Register (4Eh)                       |    |

|-----|--------------------------------------------------------------------|----|

|     | 8.2.7. GPIO Pin Sticky Register (50h)                              |    |

|     | 8.2.8. GPIO Pin Mask Register (52h)                                | 67 |

|     | 8.2.9. GPIO Pin Status Register (54h)                              |    |

|     | 8.3. Extended CODEC Registers Page Structure Definition            | 68 |

|     | 8.3.1. Extended Registers Page 00                                  | 68 |

|     | 8.3.2. Extended Registers Page 01                                  | 68 |

|     | 8.3.3. Extended Registers Page 02, 03                              | 68 |

|     | 8.4. STAC9752/9753 Paging Registers                                |    |

|     | 8.4.1. CODEC Class/Rev (60h Page 01h)                              | 69 |

|     | 8.4.2. PCI SVID (62h Page 01h)                                     |    |

|     | 8.4.3. PCI SSID (64h Page 01h)                                     | 70 |

|     | 8.4.4. Function Select (66h Page 01h)                              |    |

|     | 8.4.5. Function Information (68h Page 01h)                         |    |

|     | 8.4.6. Digital Audio Control (6Ah, Page 00h)                       |    |

|     | 8.4.7. Sense Details (6Ah Page 01h)                                |    |

|     | 8.4.8. Revision Code (6Ch)                                         |    |

|     | 8.4.9. Analog Special (6Eh)                                        |    |

|     | 8.4.10. Analog Current Adjust (72h)                                |    |

|     | 8.4.11. EAPD Access Register (74h)                                 |    |

|     | 8.4.12. High Pass Filter Bypass (78h)                              |    |

|     | 8.5. Vendor ID1 and ID2 (Index 7Ch and 7Eh)                        |    |

|     | 8.5.1. Vendor ID1 (7Ch)                                            |    |

|     | 8.5.2. Vendor ID2 (7Eh)                                            |    |

|     | LOW POWER MODES                                                    |    |

| 10. | MULTIPLE CODEC SUPPORT                                             |    |

|     | 10.1. Primary/Secondary CODEC Selection                            |    |

|     | 10.1.1. Primary CODEC Operation                                    |    |

|     | 10.1.2. Secondary CODEC Operation                                  |    |

|     | 10.2. Secondary CODEC Register Access Definitions                  |    |

| 11. | TESTABILITY                                                        |    |

|     | 11.0.1. ATE Test Mode                                              |    |

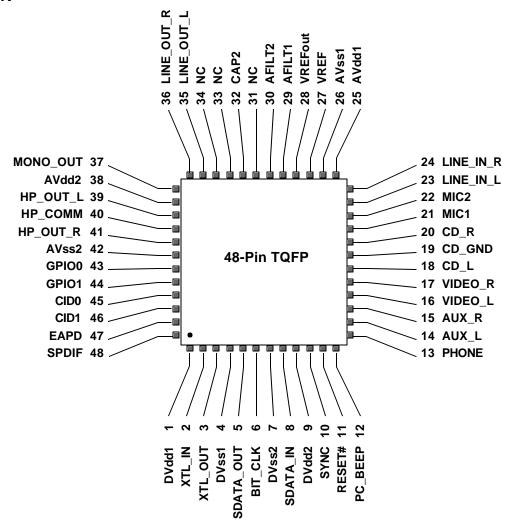

| 12. | PIN DESCRIPTION                                                    | 85 |

|     | 12.1. Digital I/O                                                  | 86 |

|     | 12.2. Analog I/O                                                   | 87 |

|     | 12.3. Filter/References                                            | 88 |

|     | 12.4. Power and Ground Signals                                     | 88 |

| 13. | ORDERING INFORMATION                                               | 89 |

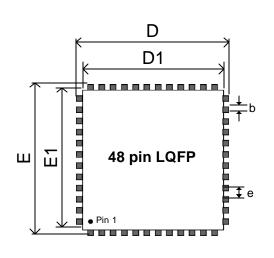

| 14. | PACKAGE DRAWING                                                    | 89 |

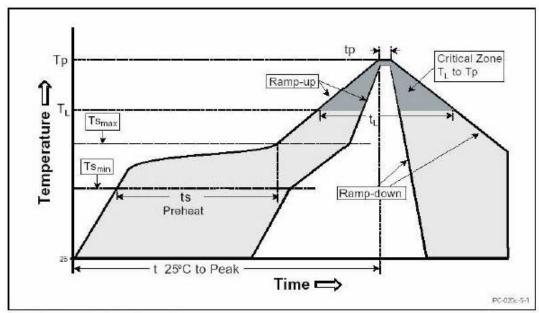

| 15. | 48-PIN LQFP SOLDER REFLOW PROFILE                                  | 90 |

|     | 15.1. Standard Reflow Profile Data                                 |    |

|     | 15.2. Pb Free Process - Package Classification Reflow Temperatures |    |

| 16. | APPENDIX A: PROGRAMMING REGISTERS                                  |    |

|     | REVISION HISTORY                                                   |    |

|     |                                                                    |    |

## STAC9752/9753

# TWO-CHANNEL, 20-BIT, AC'97 2.3 CODECS WITH HEADPHONE DRIVE, SPDIF OUTPUT MICROPHONE & JACK SENSING

# **LIST OF FIGURES**

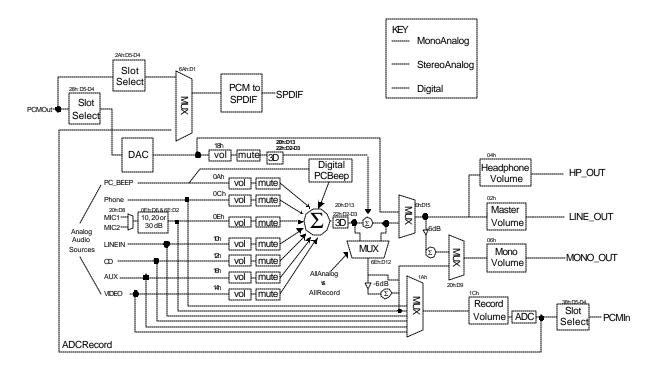

| Figure 1. Block Diagram                                       | 8  |

|---------------------------------------------------------------|----|

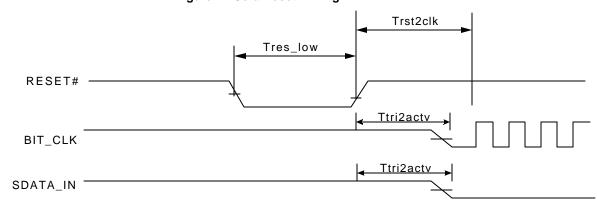

| Figure 2. Cold Reset Timing                                   | 16 |

| Figure 3. Warm Reset Timing                                   |    |

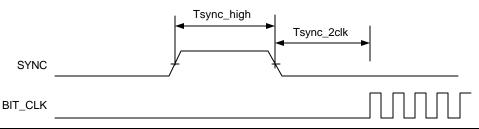

| Figure 4. Clocks Timing                                       | 17 |

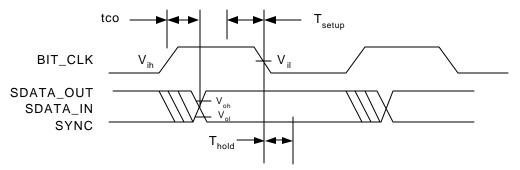

| Figure 5. Data Setup and Hold Timing                          |    |

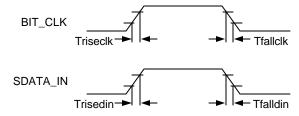

| Figure 6. Signal Rise and Fall Times Timing                   |    |

| Figure 7. AC-Link Low Power Mode Timing                       | 19 |

| Figure 8. ATE Test Mode Timing                                |    |

| Figure 9. Typical Connection Diagram                          |    |

| Figure 10. Split Independent Power Supply Operation           |    |

| Figure 11. AC-Link to its Companion Controller                |    |

| Figure 12. CODEC Clock Source Detection                       |    |

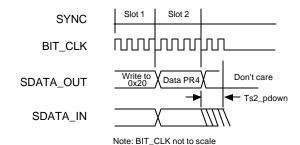

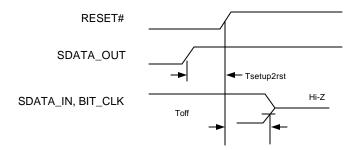

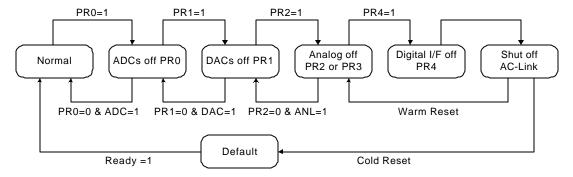

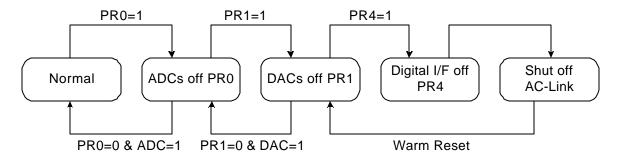

| Figure 13. STAC9752/9753 Powerdown Timing                     |    |

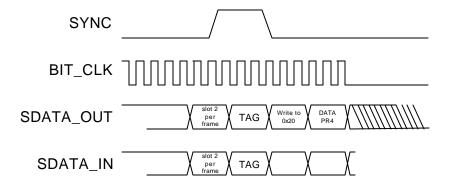

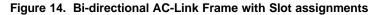

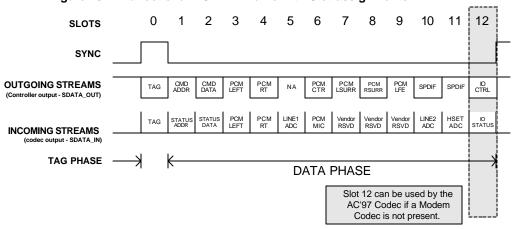

| Figure 14. Bi-directional AC-Link Frame with Slot assignments |    |

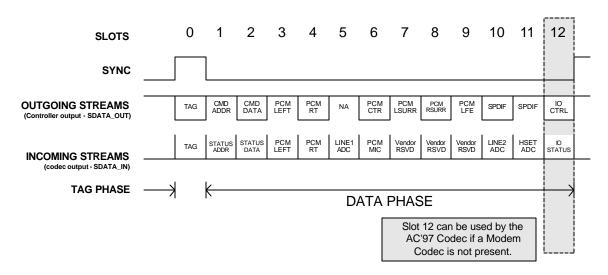

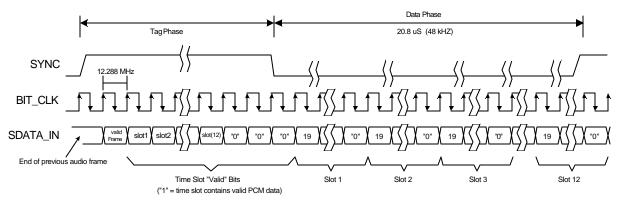

| Figure 15. AC-Link Audio Output Frame                         |    |

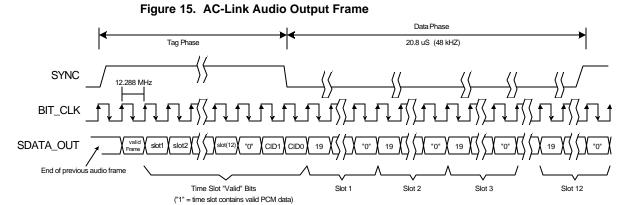

| Figure 16. Start of an Audio Output Frame                     |    |

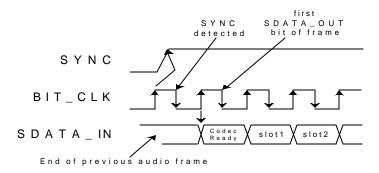

| Figure 17. STAC9752/9753 Audio Input Frame                    | 36 |

| Figure 18. Start of an Audio Input Frame                      |    |

| Figure 19. Bi-directional AC-Link Frame with Slot assignments |    |

| Figure 20. STAC9752 2-Channel Mixer Functional Diagram        | 44 |

| Figure 21. STAC9753 2-Channel Mixer Functional Diagram        |    |

| Figure 22. Example of STAC9752/9753 Powerdown/Powerup flow    |    |

| Figure 23. Powerdown/Powerup flow with analog still alive     |    |

| Figure 24. Pin Description Drawing                            | 85 |

| Figure 25. Reflow Profile                                     | 90 |

## STAC9752/9753

# TWO-CHANNEL, 20-BIT, AC'97 2.3 CODECS WITH HEADPHONE DRIVE, SPDIF OUTPUT MICROPHONE & JACK SENSING

# LIST OF TABLES

| 17 |

|----|

| 18 |

| 26 |

| 29 |

| 30 |

| 31 |

| 34 |

| 35 |

| 37 |

| 38 |

| 40 |

| 40 |

| 41 |

| 41 |

| 42 |

| 46 |

| 47 |

| 60 |

| 63 |

| 63 |

| 71 |

| 73 |

| 73 |

| 73 |

| 75 |

| 75 |

| 80 |

| 82 |

| 83 |

| 84 |

| 84 |

| 86 |

| 87 |

| 88 |

| 88 |

|    |

#### 1. PRODUCT BRIEF

# 1.1. Description

IDT's STAC9752/9753 are general purpose 20-bit, full duplex, audio CODECs conforming to the analog component specification of AC'97 (Audio CODEC 97 Component Specification Rev. 2.3). The STAC9752/9753 incorporate IDT's proprietary  $\Sigma\Delta$  technology to achieve a DAC SNR in excess of 90dB. The DACs, ADCs and mixer are integrated with analog I/Os, which include four analog line-level stereo inputs, two analog line-level mono inputs, two stereo outputs, and one mono output channel. The STAC9752/9753 include digital output capability for support of modern PC systems with an output that supports the SPDIF format. The STAC9752/9753 are standard 2-channel stereo CODECs. With IDT's headphone capability, headphones can be driven without an external amplifier. The STAC9752/9753 may be used as a secondary or tertiary CODECs, with STAC9700/21/44/56/08/84/50/66 as the primary, in a multiple CODEC configuration conforming to the AC'97 Rev. 2.3 specification. This configuration can provide the true six-channel, AC-3 playback required for DVD applications. The STAC9752/9753 communicate via the five AC-Link lines to any digital component of AC'97, providing flexibility in the audio system design. Packaged in an AC'97 compliant 48-pin TQFP, the STAC9752/9753 can be placed on the motherboard, daughter boards, PCI, AMR, CNR, MDC or ACR cards.

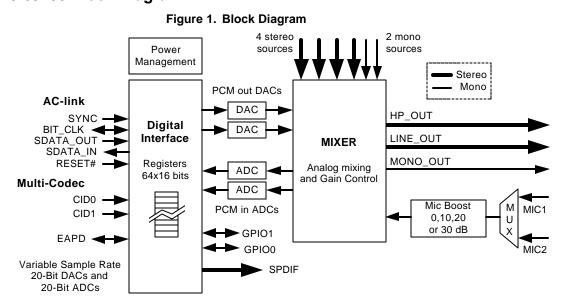

The STAC9752/9753 block diagram is illustrated in Figure 1. The STAC9752/9753 provides variable sample rate Digital-to-Analog (DA) and Analog-to-Digital (AD) conversion, mixing, and analog processing. Supported audio sample rates include 48 KHz, 44.1 KHz, 32 KHz, 22.05 KHz, 16 KHz, 11.025 KHz, and 8 KHz; additional rates are supported in the STAC9752/9753 soft audio drivers. All ADCs and DACs operate at 20-bit resolution.

Two 20-bit DACs convert the digital stereo PCM\_OUT content to audio. The MIXER block combines the PCM\_OUT with any analog sources, to drive the LINE\_OUT and HP\_OUT outputs. The MONO\_OUT delivers either microphone only, or a mono mix of sources from the MIXER. The stereo variable-sample-rate 20-bit ADCs provide record capability for any mix of mono or stereo sources, and deliver a digital stereo PCM-in signal back to the AC-Link. The microphone input and mono mix input can be recorded simultaneously, thus allowing for an all digital output in support of the digital ready initiative. For a digital ready record path, the microphone is connected to the left channel ADC while the mono output of the stereo mixer is connected to right channel ADC.

The STAC9752/9753 include jack sensing on the Headphone and Line\_Out. The STAC9752/9753 jack sense can detect the presence of devices on the Headphone and Line Outputs and on both Microphone inputs. With proprietary IDT current and impedance-sensing techniques, the impedance load on the Headphone and Line Outputs can also be detected. The GPIOs on the STAC9752/9753 remain available for advanced configurations.

The STAC9752/9753 implementation of jack sense uses the Extended Paging Registers defined by the AC'97 2.3 Specification. This allows for additional registry space to hold the identification information about the CODEC, the jack sensing details and results, and the external surroundings of the CODEC. The information within the Extended Paging Registers will allow for the automatic configuration of the audio subsystem without end-user intervention. For example, the BIOS can populate the Extended Paging Registers with valuable information for both the audio driver and the operating system such as gain and attenuation stages, input population and input phase. With this input information, the IDT driver will automatically provide to the Volume Control Panel only the volume sliders that are implemented in the system, thus improving the end-user's experience with the PC.

The information in the Extended Paging Registers will also allow for automatic configuration of microphone inputs, the ability to switch between SPDIF and analog outputs, the routing of the mas-

ter volume slider to the proper physical output, and SoftEQ configurations. The fully parametric IDT SoftEQ can be initiated upon jack insertion and sensed impedance levels.

The STAC9752/9753 also offers 2 styles of PC BEEP; Analog and Digital. The digital PC Beep is a new feature added to the AC'97 Specification Rev 2.3.

The STAC9752/9753 is designed primarily to support stereo (2-speaker) audio. True AC-3 playback can be achieved for 6-speaker applications by taking advantage of the multi-CODEC option available in the STAC9752/9753 to support multiple CODECs in an AC'97 architecture. Additionally, the STAC9752/9753 provides for a stereo enhancement feature, IDT Surround 3D (SS3D). SS3D provides the listener with several options for improved speaker separation beyond the normal two- or four-speaker arrangements.

The STAC9752/9753 can be SoundBlaster<sup>®</sup> and Windows Sound System<sup>®</sup> compatible when used with IDT's WDM driver for Windows 98/2K/ME/XP or with Intel/Microsoft driver included with Windows 2K/ME/XP. SoundBlaster is a registered trademark of Creative Labs. Windows is a registered trademark of Microsoft Corporation.

# 1.2. STAC9752/9753 Block Diagram

# 1.3. Key Specifications

Analog LINE\_OUT SNR: 90 dB

STAC9752 DAC SNR: 89 dB

STAC9753 DAC SNR: 84dB

STAC9752 ADC SNR: 90 dB

STAC9753 ADC SNR: 88 dB

Crosstalk between Input Channels: -70 dB

Spurious Tone Rejection: 100 dB

## 1.4. Related Materials

- Product Brief

- Reference Designs for MB, AMR, CNR, and ACR applications

- Audio Precision Performance Plots

# 1.5. Additional Support

Additional product and company information can be obtained by going to the IDT web site.

#### 2. CHARACTERISTICS AND SPECIFICATIONS

# 2.1. Electrical Specifications

## 2.1.1. Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the STAC9752/9753. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                  | Pin  | Maximum Rating                                                                                                |

|---------------------------------------|------|---------------------------------------------------------------------------------------------------------------|

| Analog maximum supply voltage         | AVdd | 6 Volts                                                                                                       |

| Digital maximum supply voltage        | DVdd | 5.5 Volts                                                                                                     |

| VREFOUT output current                |      | 5 mA                                                                                                          |

| Voltage on any pin relative to ground |      | Vss - 0.3 V to Vdd + 0.3 V                                                                                    |

| Operating temperature                 |      | 0°C to +70°C                                                                                                  |

| Storage temperature                   |      | -55 °C to +125 °C                                                                                             |

| Soldering temperature                 |      | 260 °C for 10 seconds *<br>Soldering temperature information for all available packages<br>begins on page 90. |

## 2.1.2. Recommended Operation Conditions

| Parameter                     |                             | Min.  | Тур. | Max.  | Units |

|-------------------------------|-----------------------------|-------|------|-------|-------|

| Power Supply Voltage          | Digital - 3.3 V             | 3.135 | 3.3  | 3.465 | V     |

|                               | Analog - 5 V                | 4.75  | 5    | 5.25  | V     |

|                               | Analog - 3.3 V              | 3.135 | 3.3  | 3.465 | V     |

| Ambient Operating Temperature |                             | 0     |      | +70   | °C    |

| Case Temperature              | T <sub>case</sub> (48-LQFP) |       |      | +90   | °C    |

*ESD:* The STAC9752/9753 is an ESD (electrostatic discharge) sensitive device. The human body and test equipment can accumulate and discharge electrostatic charges up to 4000 Volts without detection. Even though the STAC9752/9753 implements internal ESD protection circuitry, proper ESD precautions should be followed to avoid damaging the functionality or performance.

# 2.1.3. Power Consumption

| Par                          | ameter                            | Min       | Тур       | Max    | Unit |

|------------------------------|-----------------------------------|-----------|-----------|--------|------|

| Digital Supply Current       |                                   |           |           |        |      |

| + 3.3V Digital               |                                   | -         | 30        | -      | mA   |

| Analog Supply Current (at Re | set state)                        |           |           |        | •    |

| + 5V Analog                  |                                   | -         | 35        | -      | mA   |

| + 3.3V Analog                |                                   | -         | 35        | -      | mA   |

| Power Down Status (individu  | ally asserted) - All PR measureme | nts taken | while unr | nuted. | I    |

|                              | +5V Analog Supply Current         |           | 50        |        |      |

| All paths unmuted            | +3.3V Analog Supply Current       | -         | 44        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 33        |        |      |

|                              | +5V Analog Supply Current         |           | 42        |        |      |

| PR0                          | +3.3V Analog Supply Current       | -         | 39        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 22        |        |      |

|                              | +5V Analog Supply Current         |           | 41        |        |      |

| PR1                          | +3.3V Analog Supply Current       | -         | 38        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 28        |        |      |

|                              | +5V Analog Supply Current         |           | 32        |        |      |

| PR2                          | +3.3V Analog Supply Current       | -         | 29        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

|                              | +5V Analog Supply Current         |           | 23        |        |      |

| PR3                          | +3.3V Analog Supply Current       | -         | 19        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

|                              | +5V Analog Supply Current         |           | 50        |        |      |

| PR4                          | +3.3V Analog Supply Current       | -         | 44        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 0.2       |        |      |

|                              | +5V Analog Supply Current         |           | 50        |        |      |

| PR5                          | +3.3V Analog Supply Current       | -         | 44        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

|                              | +5V Analog Supply Current         |           | 38        |        |      |

| PR6                          | +3.3V Analog Supply Current       | -         | 36        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 33        |        |      |

|                              | +5V Analog Supply Current         |           | 35        |        |      |

| PR0 & PR1                    | +3.3V Analog Supply Current       | -         | 35        | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

|                              | +5V Analog Supply Current         |           | 5         |        |      |

| PR0, PR1, PR2, PR6           | +3.3V Analog Supply Current       | -         | 5         | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

|                              | +5V Analog Supply Current         |           | 0.6       |        |      |

| PR0, PR1, PR2, PR3, PR6      | +3.3V Analog Supply Current       | -         | 0.6       | -      | mA   |

|                              | +3.3V Digital Supply Current      |           | 12        |        |      |

## 2.1.4. AC-Link Static Digital Specifications

$(T_{ambient} = 25 \, {}^{\circ}C, \, DVdd = 3.3V \pm 5\%, \, AVss=DVss=0V)$

| Parameter                                       | Symbol | Min         | Тур | Max         | Unit |

|-------------------------------------------------|--------|-------------|-----|-------------|------|

| Input voltage range                             | Vin    | -0.30       | -   | DVdd + 0.30 | V    |

| Low level input range                           | Vil    | -           | -   | 0.35 x DVdd | V    |

| High level input voltage                        | Vih    | 0.65 x DVdd | -   | -           | V    |

| High level output voltage                       | Voh    | 0.90 x DVdd | -   | -           | V    |

| Low level output voltage                        | Vol    | -           | -   | 0.1 x DVdd  | V    |

| Input leakage current (AC-Link inputs)          | -      | -10         | -   | 10          | μΑ   |

| Output leakage current (Hi-Z AC-Link outputs)   | -      | -10         | -   | 10          | μΑ   |

| BIT_CLK (primary mode) Output leakage current   | -      | -10         | -   | 100         | μΑ   |

| BIT_CLK (secondary mode) Output leakage current | -      | -10         | -   | 10          | μΑ   |

| Output buffer drive current                     | -      | -           | 4   | -           | mA   |

| BIT_CLK/SPDIF Output drive current              | -      | -           | 18  | -           | mA   |

Note: Due to an internal pulldown resistor, the BIT\_CLK pin will exhibit less than 100 mA of leakage current when the CODEC is configured as primary. This pin meets the +/- 10 mA leakage specification when configured as secondary.

# 2.1.5. STAC9752 5 V Analog Performance Characteristics

$(T_{ambient} = 25 \, ^{\circ}\text{C}, \, \text{AVdd} = 5.0 \, \text{V} \pm 5\%, \, \text{DVdd} = 3.3 \, \text{V} \pm 5\%, \, \text{AVss=DVss=0} \, \text{V}; \, 1 \, \text{KHz} \, \text{input sine wave}; \, \text{Sample Frequency} = 48 \, \text{KHz}; \, 0 \, \text{dB} = 1 \, \text{Vrms}, \, \text{with a 10} \, \text{K}\Omega, \, 50 \, \text{pF load}, \, \text{Testbench Characterization} \, \text{BW}: \, 20 \, \text{Hz} \, \text{to 20} \, \text{KHz}, \, 0 \, \text{dB} \, \text{settings on all gain stages})$

| Parameter                                           | Min | Тур  | Max    | Unit |  |  |  |

|-----------------------------------------------------|-----|------|--------|------|--|--|--|

| Full Scale Input Voltage:                           |     |      |        |      |  |  |  |

| All Analog Inputs except Microphone                 | -   | 1.00 | -      | Vrms |  |  |  |

| Microphone Inputs (Note 1)                          | -   | 0.03 | -      | Vrms |  |  |  |

| Full Scale Output:                                  | •   |      |        | ·    |  |  |  |

| Line Output                                         | -   | 1.00 | -      | Vrms |  |  |  |

| PCM (DAC) to LINE_OUT                               | -   | 1.00 | -      | Vrms |  |  |  |

| MONO_OUT                                            | -   | 1.00 | -      | Vrms |  |  |  |

| HEADPHONE_OUT (32 $\Omega$ load) per channel (peak) | -   | 50   | -      | mW   |  |  |  |

| Dynamic Range: -60dB signal level (Note 2)          | -   |      |        |      |  |  |  |

| CD to LINE_OUT                                      | -   | 90   | -      | dB   |  |  |  |

| LINE / AUX / VIDEO to LINE_OUT                      | -   | 90   | -      | dB   |  |  |  |

| PCM (DAC) to LINE_OUT                               | 80  | 87   | -      | dB   |  |  |  |

| PCM (DAC) in BYPASS Mode to LINE_OUT                | -   | 88   | -      | dB   |  |  |  |

| LINE_IN to A/D (1 VRMS Input Referenced)            | 80  | 90   | -      | dB   |  |  |  |

| LINE_IN to HEADPHONE_OUT                            | -   | 90   | -      | dB   |  |  |  |

| Analog Frequency Response (Note 3)                  | 10  | -    | 30,000 | Hz   |  |  |  |

| Total Harmonic Distortion + Noise (-3dB): (Note 4)  |     |      |        |      |  |  |  |

| CD to LINE_OUT                                      | -   | -85  | -      | dB   |  |  |  |

| Other to LINE_OUT                                   | -   | -87  | -      | dB   |  |  |  |

| PCM (DAC) to LINE_OUT (full scale)                  | -   | -83  | -      | dB   |  |  |  |

| PCM (DAC) in BYPASS Mode to LINE_OUT                | -   | -86  | -      | dB   |  |  |  |

| LINE_IN to A/D (-3dBV input Level)                  | -   | -85  | -      | dB   |  |  |  |

| HEADPHONE_OUT (32 Ω load)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Parameter                                             | Min    | Тур        | Max    | Unit        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------|------------|--------|-------------|

| SNR (idle channel) (Note 5)   DAC to LINE_OUT   80   90   -   dB     DAC to LINE_OUT   -   90   -   dB     LINE_/ AUX_/ VIDEO to LINE_OUT   -   90   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   92   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   -   -   -   dB     LINE_IN to A/D with High Pass Filter enabled   -   -   -   -   -   -   -   -   - | HEADPHONE_OUT (32 Ω load)                             | -      | -68        | -      | dB          |

| DAC to LINE_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HEADPHONE_OUT (10 KΩ load)                            | -      | -81        | -      | dB          |

| DAC in BYPASS Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SNR (idle channel) (Note 5)                           |        |            |        |             |

| LINE / AUX / VIDEO to LINE_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DAC to LINE_OUT                                       | 80     | 90         | -      | dB          |

| LINE_IN to A/D with High Pass Filter enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DAC in BYPASS Mode                                    | -      | 92         | -      | dB          |

| A/D & D/A Digital Filter Pass Band (Note 6)         20         -         19,200         Hz           A/D & D/A Digital Filter Transition Band         19,200         -         28,800         Hz           A/D & D/A Digital Filter Stop Band Rejection (Note 7)         -100         -         -         HZ           A/D & D/A Digital Filter Stop Band Rejection (Note 7)         -100         -         -         dB           DAC Out-of-Band Rejection (Note 8)         -55         -         -         dB           Group Delay (48 KHz sample rate)         -         -         1         ms           Power Supply Rejection Ratio (20 KHz)         -         -         -         dB           Fower Supply Rejection Ratio (20 KHz)         -         -         -         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(10 KHz Signal Frequency)         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                | LINE / AUX / VIDEO to LINE_OUT                        | -      | 90         | -      | dB          |

| A/D & D/A Digital Filter Transition Band         19,200         -         28,800         Hz           A/D & D/A Digital Filter Stop Band         28,800         -         -         HZ           A/D & D/A Digital Filter Stop Band Rejection (Note 7)         -100         -         -         dB           DAC Out-of-Band Rejection (Note 8)         -55         -         -         dB           Group Delay (48 KHz sample rate)         -         -         1         ms           Power Supply Rejection Ratio (1 KHz)         -         -70         -         dB           Power Supply Rejection Ratio (20 KHz)         -         -40         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         -         -100         -         dB           Input Capacitance         -         -         50         -         KΩ           Input Capacitance         -         -         -         -         -                                                                                                                                                                                                                                                               | LINE_IN to A/D with High Pass Filter enabled          | -      | 92         | -      | dB          |

| A/D & D/A Digital Filter Stop Band         28,800         -         -         Hz           A/D & D/A Digital Filter Stop Band Rejection (Note 7)         -100         -         -         dB           DAC Out-of-Band Rejection (Note 8)         -55         -         -         dB           Group Delay (48 KHz sample rate)         -         -         1         ms           Power Supply Rejection Ratio (16 KHz)         -         -70         -         dB           Power Supply Rejection Ratio (20 KHz)         -         -40         -         dB           Any Analog Input to LINE_OUT Crosstalk (10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk (1 KHz Signal Frequency)         -         -100         -         dB           Any Analog Input to LINE_OUT Crosstalk (1 KHz Signal Frequency)         -         -100         -         dB           Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         -1.5         -         dB           Input Capacitance         -         -         50         -         KΩ           Input Capacitance         -         -         50         -         KΩ                                                                                                                                                                                                                                                            | A/D & D/A Digital Filter Pass Band (Note 6)           | 20     | -          | 19,200 | Hz          |

| A/D & D/A Digital Filter Stop Band Rejection (Note 7)         -100         -         -         dB           DAC Out-of-Band Rejection (Note 8)         -55         -         -         dB           Group Delay (48 KHz sample rate)         -         -         1         ms           Power Supply Rejection Ratio (20 KHz)         -         -70         -         dB           Power Supply Rejection Ratio (20 KHz)         -         -40         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           MI Human Cross and Signal Frequency)         -         -100         -         dB           Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         1.5         -         dB           Input Lagratian Cross and Size         -         -         1.5                                                                                                                                                                                                                  | A/D & D/A Digital Filter Transition Band              | 19,200 | -          | 28,800 | Hz          |

| DAC Out-of-Band Rejection (Note 8)         -55         -         -         dB           Group Delay (48 KHz sample rate)         -         -         -         1         ms           Power Supply Rejection Ratio (1 KHz)         -         -70         -         dB           Power Supply Rejection Ratio (20 KHz)         -         -40         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           Attenuation, Gain Step Size         -         -100         -         dB           Attenuation, Gain Step Size         -         -         1.5         -         dB           Input Impedance         -         50         -         KΩ           Input Capacitance         -         15         -         pF           VREFout         -         0.5 X AVdd         -         V           VREFout         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5<                                                                                                                                                                                                                                                                                                   | A/D & D/A Digital Filter Stop Band                    | 28,800 | -          | -      | Hz          |

| Group Delay (48 KHz sample rate)   -   -   -   1   ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A/D & D/A Digital Filter Stop Band Rejection (Note 7) | -100   | -          | -      | dB          |

| Power Supply Rejection Ratio (1 KHz)         -         -70         -         dB           Power Supply Rejection Ratio (20 KHz)         -         -40         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk<br>(1 KHz Signal Frequency)         -         -100         -         dB           Applications of the Signal Frequency         -         -100         -         dB           Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         1.5         -         dB           Input Impedance         -         50         -         KΩ           Input Capacitance         -         15         -         pF           VREFout         -         0.5 X AVdd         -         V           VREFOut         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         100         -         ppm                                                                                                                                                                                                                                                                                                   | DAC Out-of-Band Rejection (Note 8)                    | -55    | -          | -      | dB          |

| Power Supply Rejection Ratio (20 KHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Group Delay (48 KHz sample rate)                      | -      | -          | 1      | ms          |

| Any Analog Input to LINE_OUT Crosstalk (10 KHz Signal Frequency)         -         -80         -         dB           Any Analog Input to LINE_OUT Crosstalk (1 KHz Signal Frequency)         -         -100         -         dB           Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         1.5         -         dB           Input Impedance         -         50         -         KΩ           Input Capacitance         -         15         -         pF           VREFout         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT /                                                                                                                                                                                                                                                                                                                           | Power Supply Rejection Ratio (1 KHz)                  | -      | -70        | -      | dB          |

| 10 KHz Signal Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power Supply Rejection Ratio (20 KHz)                 | -      | -40        | -      | dB          |

| Any Analog Input to LINE_OUT Crosstalk (1 KHz Signal Frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Any Analog Input to LINE_OUT Crosstalk                | _      | -80        | _      | 4B          |

| 1 KHz Signal Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1:                                                    | _      | -00        | _      | ав          |

| Spurious Tone Rejection         -         -100         -         dB           Attenuation, Gain Step Size         -         1.5         -         dB           Input Impedance         -         50         -         KΩ           Input Capacitance         -         15         -         pF           VREFout         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Capacitance         -         -         100         pF           Mute Attenuation         90         96 <td< td=""><td></td><td>-</td><td>-100</td><td>-</td><td>dB</td></td<>                                                                                                                                                                                                                                                                                      |                                                       | -      | -100       | -      | dB          |

| Attenuation, Gain Step Size         -         1.5         -         dB           Input Impedance         -         50         -         KΩ           Input Capacitance         -         15         -         pF           VREFout         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         -         ppm/°C           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Resistance         -         -         -         100         pF           Mute Attenuation         90         96         -         dB           PLL lock time         -         -                                                                                                                                                                                                                                                                                                                                                              | 1                                                     | -      | -100       | -      | dB          |

| Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       | -      | 1.5        | -      | dB          |

| VREFout         -         0.5 X AVdd         -         V           VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Resistance         -         32         -         Ω           HEADPHONE_OUT Load Capacitance         -         -         100         pF           Mute Attenuation         90         96         -         dB           PLL lock time         -         100         200         µsec           PLL 24.576 MHz clock jitter         -         -         -         750         psec           PLL frequency multiplication tolerance                                                                                                                                                                                                                                                                                                                                           | Input Impedance                                       | -      | 50         | -      | ΚΩ          |

| VREF         -         0.45X AVdd         -         V           Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Resistance         -         32         -         Ω           HEADPHONE_OUT Load Capacitance         -         -         100         pF           Mute Attenuation         90         96         -         dB           PLL lock time         -         100         200         µsec           PLL 24.576 MHz clock jitter         -         -         -         750         psec           PLL frequency multiplication tolerance         -         -         12.5         ppm                                                                                                                                                                                                                                                                                                                                                                 | Input Capacitance                                     | -      | 15         | -      | pF          |

| Interchannel Gain Mismatch ADC         -         -         0.5         dB           Interchannel Gain Mismatch DAC         -         -         0.5         dB           Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Resistance         -         32         -         Ω           HEADPHONE_OUT Load Capacitance         -         -         100         pF           Mute Attenuation         90         96         -         dB           PLL lock time         -         100         200         μsec           PLL 24.576 MHz clock jitter         -         -         750         psec           PLL frequency multiplication tolerance         -         -         12.5         ppm                                                                                                                                                                                                                                                                                                                                                                                                                                           | VREFout                                               | -      | 0.5 X AVdd | -      | V           |

| Interchannel Gain Mismatch DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VREF                                                  | -      | 0.45X AVdd | -      | V           |

| Gain Drift         -         100         -         ppm/°C           DAC Offset Voltage         -         10         20         mV           Deviation from Linear Phase         -         -         1         degrees           LINE_OUT / MONO_OUT Load Resistance         10         -         -         KΩ           LINE_OUT / MONO_OUT Load Capacitance         -         -         50         pF           HEADPHONE_OUT Load Resistance         -         32         -         Ω           HEADPHONE_OUT Load Capacitance         -         -         100         pF           Mute Attenuation         90         96         -         dB           PLL lock time         -         100         200         μsec           PLL 24.576 MHz clock jitter         -         -         750         psec           PLL frequency multiplication tolerance         -         -         12.5         ppm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Interchannel Gain Mismatch ADC                        | -      | -          | 0.5    | dB          |