# 1200V Cascoded N-Channel MOSFET

#### **Features**

- 1200V breakdown voltage

- ► Low threshold, 1.6V max.

- ▶ High input impedance

- Low input capacitance

- Integrated high voltage resistor divider

- Integrated 1000:1 resistor divider

- Compact 3x3 LFGA package

### **Applications**

- High voltage shunt regulator

- High voltage linear amplifier

- High voltage digital pulsers

- High voltage sensing circuit

## **Ordering Information**

| Part Number | Package Option | Packing   |  |

|-------------|----------------|-----------|--|

| LN100LA-G   | 6-Lead LFGA    | 3000/Reel |  |

# **Absolute Maximum Ratings**

| Parameter                                            | Value              |

|------------------------------------------------------|--------------------|

| Drain-to-Source voltage                              | 1200V              |

| V <sub>1</sub> - V <sub>2</sub> differential voltage | 1200V              |

| V <sub>2</sub> - V <sub>3</sub> differential voltage | 5.0V               |

| Operating temperature range                          | -25°C to +125°C    |

| Power dissipation, T <sub>A</sub> = 25°C             | 350mW <sup>1</sup> |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### Note:

1. Device mounted on a 25mm x 25mm x 1.57mm board.

### **Typical Thermal Resistance**

| <b>J</b> .  |                                       |

|-------------|---------------------------------------|

| Package     | $oldsymbol{	heta}_{j_{oldsymbol{a}}}$ |

| 6-Lead LFGA | 186°C/W                               |

### **General Description**

The LN100 is a 1200V cascoded N-channel MOSFET with an integrated high value high voltage resistor divider. Multiple devices can be used in series for voltages greater than 1200V. A resistor divider ratio of 1000:1 is provided. High value resistors are used to minimize power consumption.

The maximum Gate-to-Source threshold voltage is 1.6V. This allows the Gate to be controlled by low voltage circuitry. The LN100 can be used as a high voltage low power pulser. It can also be used in a high voltage low current amplifier application where it is used to charge and discharge a small capacitive load.

### **Product Summary**

| BV <sub>DSS</sub><br>min (V) | $R_{	extsf{DS(ON)}}$ max (kΩ) | l <sub>D(ON)</sub><br>min (mA) |  |  |

|------------------------------|-------------------------------|--------------------------------|--|--|

| 1200                         | 3.0                           | 3.0                            |  |  |

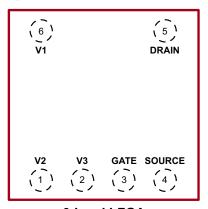

### **Pin Configuration**

6-Lead LFGA (top view) Pads are at bottom of package.

# **Product Marking**

Y = Last Digit of Year Sealed W = Code for Week Sealed L = Lot Number \_\_\_\_ = "Green" Packaging

Package may or may not include the following marks: Si or

### **Electrical Characteristics**

(T<sub>i</sub> = 25°C unless otherwise specified)

| Symbol                              | Parameter                                                     |                               | Min Typ Max Uni |                                 | Unit | t Conditions                                                      |  |  |

|-------------------------------------|---------------------------------------------------------------|-------------------------------|-----------------|---------------------------------|------|-------------------------------------------------------------------|--|--|

| MOSFET M1 and M2                    |                                                               |                               |                 |                                 |      |                                                                   |  |  |

| BV <sub>DSS1</sub>                  | Drain-to-Source breakdown voltage of M1                       | 600                           | -               | -                               | V    | $V_{GS} = 0V, I_{D} = 1.0 \mu A$                                  |  |  |

| BV <sub>DSS2</sub>                  | Drain-to-Source breakdown voltage of M2                       | 600                           | -               | -                               | V    | $V_{GS} = 0V, I_{D} = 1.0 \mu A$                                  |  |  |

| V <sub>GS(th)</sub>                 | Gate-to-Source threshold voltage                              | 0.5                           | -               | 1.6                             | V    | $V_{GS} = V_{DS}$ , $I_{D} = 10\mu A$<br>See test circuit         |  |  |

| R <sub>DS(ON)</sub>                 | Static Drain-to-Source On-State resistance                    | -                             | -               | 3.0                             | kΩ   | $V_{GS}$ = 2.8V, $I_{D}$ = 2.0mA<br>See test circuit              |  |  |

| I <sub>D(ON)</sub>                  | On-State Drain current                                        | 3.0                           |                 |                                 | mA   | V <sub>GS</sub> = 2.8V, V <sub>DS</sub> = 25V<br>See test circuit |  |  |

| C <sub>ISS</sub>                    | Input capacitance                                             | -                             | -               | 50                              | pF   | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 25V                       |  |  |

| Zener Diode                         |                                                               |                               |                 |                                 |      |                                                                   |  |  |

| V <sub>z</sub>                      | M2 Gate-to-Source Zener diode clamp                           | 6.5                           | -               | 12                              | V    | I <sub>GS</sub> = 1.0mA, V <sub>S</sub> = 0V                      |  |  |

| I <sub>GS</sub>                     | Gate-to-Source Zener diode leakage                            | -                             | -               | 100                             | nA   | V <sub>GS</sub> = 4.5V                                            |  |  |

| l <sub>z</sub>                      | Maximum Zener current                                         | -                             | 10              | -                               | mA   |                                                                   |  |  |

| Resistors $R_1$ , $R_2$ , and $R_3$ |                                                               |                               |                 |                                 |      |                                                                   |  |  |

| R <sub>1</sub> + R <sub>2</sub>     | Resistor divider R <sub>1</sub> + R <sub>2</sub>              | $54$ - $M\Omega$ $V_1 = 0$ to |                 | $V_1 = 0$ to 1000V, $V_2 = 0$ V |      |                                                                   |  |  |

| R <sub>1</sub>                      | Resistor R <sub>1</sub>                                       | 27                            | -               | -                               | ΜΩ   | V <sub>R1</sub> = 0 to 500V                                       |  |  |

| R <sub>2</sub>                      | Resistor R <sub>2</sub>                                       | 27                            | -               | -                               | ΜΩ   | V <sub>R2</sub> = 0 to 500V                                       |  |  |

| $R_3$                               | Resistor R <sub>3</sub>                                       | 54                            | -               | -                               | kΩ   | V <sub>R3</sub> = 0 to 5.0V                                       |  |  |

| ΔR                                  | R <sub>1</sub> , R <sub>2</sub> , and R <sub>3</sub> matching | -                             | -               | ±18                             | %    |                                                                   |  |  |

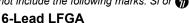

# **Block Diagram**

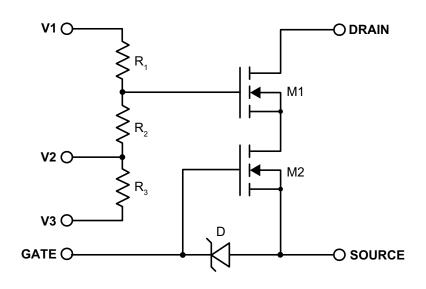

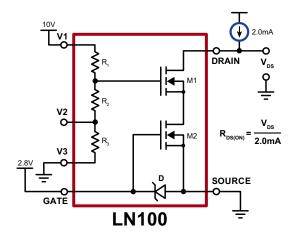

### **Test Circuits**

**Gate-to-Source Threshold Voltage**

**Drain-to-Source On-Resistance**

**On-State Drain Current**

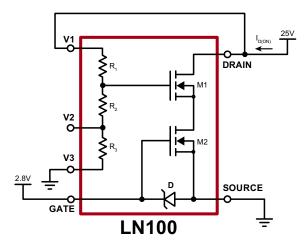

### **Typical Application Circuits**

### **High Voltage, Low Current Shunt Regulator**

The LN100 can be used as a high voltage, low current shunt regulator as shown in Figure 1. Resistor divider  $R_1$ ,  $R_2$ , and

$R_3$  divides the output voltage by approximately 1000. V2 is the feedback voltage for the op-amp. If the reference voltage,  $V_{\text{REF}}$ , is 1.0V, the output voltage will be shunted to 1000V.

Figure 1: High Voltage, Low Current, Shunt Regulator

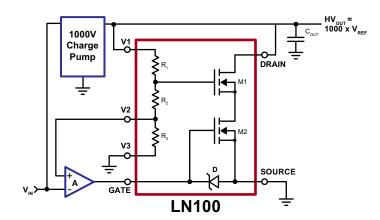

### **High Voltage, Low Current Linear Amplifier**

In Figure 2, the two LN100's are used as the main output stage for a 1000V low frequency amplifier to drive capacitive loads. The top LN100 is used to actively charge the load up to the desired voltage. The bottom LN100 is used to actively discharge the load to the desired voltage.

The Gate is driven with a low voltage op-amp.  $V_2$  is the feedback voltage for the op-amp setting it to a gain of 60dB. A 0 to 1.0V sinusoidal waveform on  $V_{\rm IN}$  will create a 0 to 1000V sinusoidal waveform on  $HV_{\rm OUT}$ . Output frequency only needs to go up to 300Hz.

Figure 2: High Voltage Low Current Linear Amplifier

### **Typical Application Circuits (cont.)**

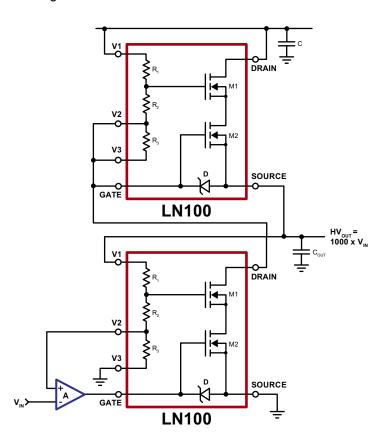

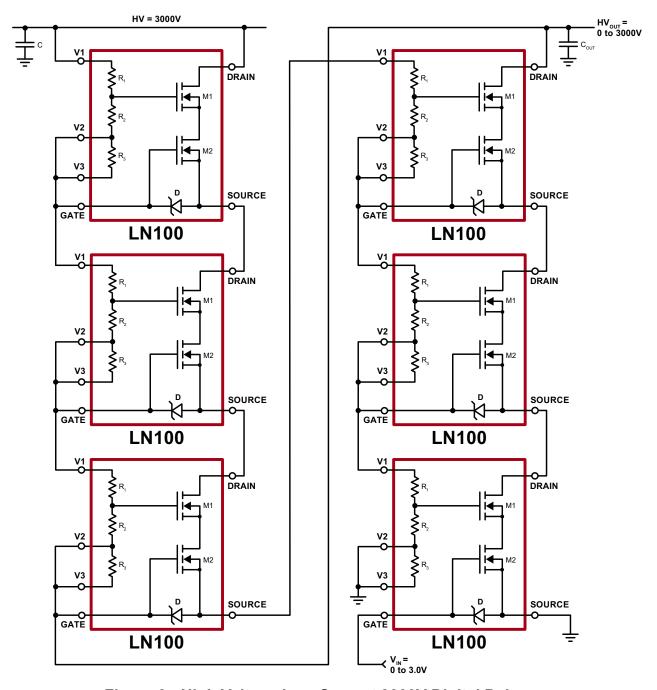

### High Voltage, Low Current Digital Pulser

In Figure 3, the six LN100's are used as the main output stage for a 3000V low frequency digital pulser. The first three LN100s are used to charge the load up to 3000V. The next

three LN100s are used to discharge the load back to ground. The integrated resistors in each of the LN100 allows the 3000V to be divided into thirds. Each LN100 will only need to hold off 1000V.

Figure 3: High Voltage Low Current 3000V Digital Pulser

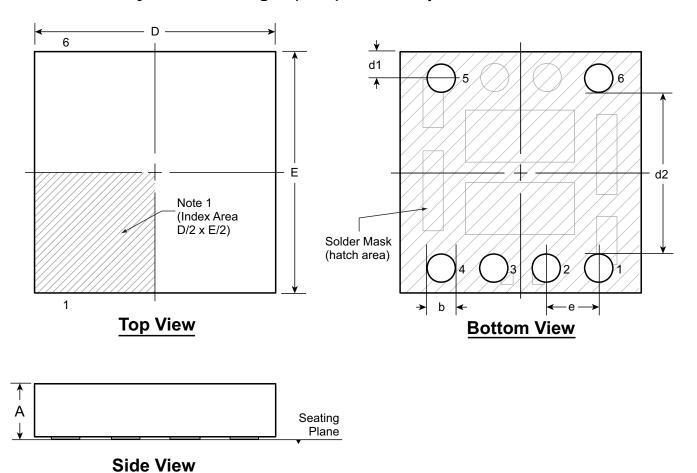

# 6-Lead LFGA Package Outline (LA)

# 3.00x3.00mm body, 0.85mm height (max), 0.65mm pitch

#### Notes:

A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symb           | ool | Α    | b    | D     | E     | d1    | d2          | е           |

|----------------|-----|------|------|-------|-------|-------|-------------|-------------|

| Dimension (mm) | MIN | 0.75 | 0.30 | 2.925 | 2.925 | 0.225 | 2.00<br>BSC | 0.65<br>BSC |

|                | NOM | 0.80 | 0.35 | 3.000 | 3.000 | 0.325 |             |             |

|                | MAX | 0.85 | 0.40 | 3.075 | 3.075 | 0.425 |             |             |

Drawings not to scale

Supertex Doc. #: DSPD-6LFGALA3X3P065, Version A110811

(The package drawings in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.