## High Voltage Power Operational Amplifier

#### **FEATURES**

- RoHS Compliant

- Monolithic MOS Technology

- Low Cost

- High Voltage Operation: 350V

- Low Quiescent Current: TYP = 2.2mA

- No Second Breakdown

- High Output Current: 120mA Peak

- Piezo Electric Positioning

- Electrostatic Transducer and Deflection

- Deformable Mirror Focusing

- Biochemistry Stimulators

- Computer to Vacuum Tube Interface

### **DESCRIPTION**

The PA441 is a high voltage monolithic MOSFET operational amplifier with improved noise and bandwidth performance compared to similar previous products.

Features previously found only in hybrid designs are offered in this monolithic package, with improved reliability. Inputs are protected from excessive common mode and differential mode voltages. The safe operating area (SOA) has no second breakdown limitation and can be observed with all type loads by choosing an appropriate current limiting resistor. External compensation provides the user flexibility in choosing optimum gain and bandwidth for the application.

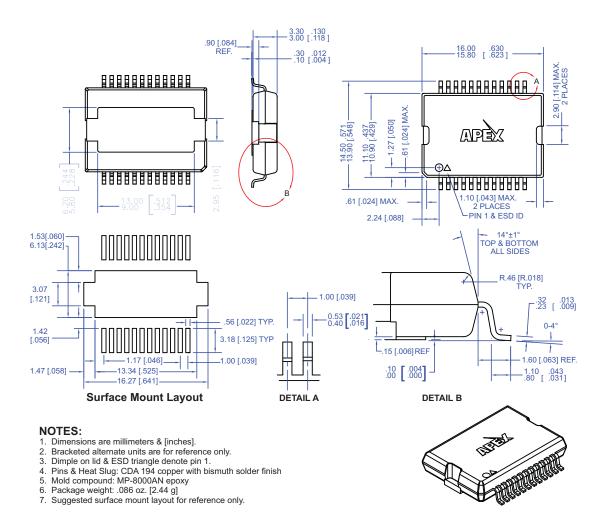

- The PA441DF is packaged in a 24-pin PSOP (JEDEC MO-166) package. The metal heat slug of the PA441DF is isolated in excess of full supply voltage.

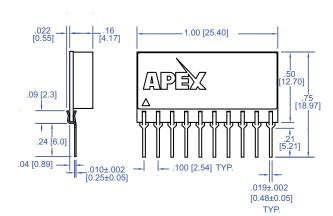

- The PA441DW is packaged in Apex Microtechnology's hermetic ceramic PIP. The alumina ceramic isolates the die in excess of full supply voltage.

- The PA443DF has two PA441 dies packaged in a 24 pin PSOP (JEDEC MO-166) package. The heatslug of the PA443DF package is isolated in excess of full supply voltage

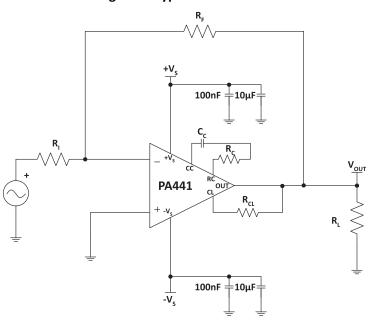

## **TYPICAL CONNECTION**

**Figure 1: Typical Connection**

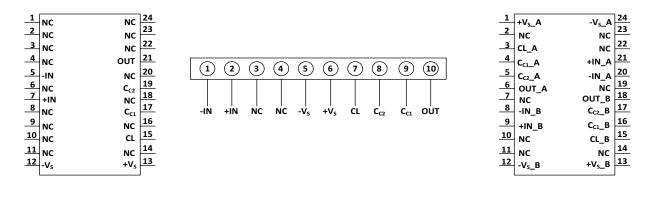

## **PINOUT AND DESCRIPTION TABLE**

**Figure 2: External Connections**

PA441DF PA441DW PA443DF

**Notes:** a) For C<sub>C</sub> values, see graph on page 9.

**b)** C<sub>C</sub> must be rated for full supply voltage.

## PA441DF

| Pin Number | Name | Description                                                                                                                                                                                 |

|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | -IN  | The inverting input.                                                                                                                                                                        |

| 7          | +IN  | The non-inverting input.                                                                                                                                                                    |

| 12         | -Vs  | The negative supply rail.                                                                                                                                                                   |

| 13         | +Vs  | The positive supply rail.                                                                                                                                                                   |

| 15         | CL   | Connect to the current limit resistor. Output current flows into/out of this pin through $R_{\text{CL}}$ . The output pin and the load are connected to the other side of $R_{\text{CL}}$ . |

| 17, 19     | СС   | Compensation capacitor connection. Select value based on Phase Compensation.  See applicable section.                                                                                       |

| 21         | OUT  | The output. Connect this pin to load and to the feedback resistors.                                                                                                                         |

| All Others | NC   | No connection.                                                                                                                                                                              |

## PA441DW

| Pin Number | Name | Description                                                                                                                                                                   |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | -IN  | The inverting input.                                                                                                                                                          |

| 2          | +IN  | The non-inverting input.                                                                                                                                                      |

| 3, 4       | NC   | No connection.                                                                                                                                                                |

| 5          | -Vs  | The negative supply rail.                                                                                                                                                     |

| 6          | +Vs  | The positive supply rail.                                                                                                                                                     |

| 7          | CL   | Connect to the current limit resistor. Output current flows into/out of this pin through $R_{CL}$ . The output pin and the load are connected to the other side of $R_{CL}$ . |

| 8, 9       | СС   | Compensation capacitor connection. Select value based on Phase Compensation.  See applicable section.                                                                         |

| 10         | OUT  | The output. Connect this pin to load and to the feedback resistors.                                                                                                           |

## PA443DF

| Pin Number | Name  | Description                                                                                                                                                                   |

|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | +Vs_A | The positive supply rail for channel A.                                                                                                                                       |

| 3          | CL_A  | Connect to the current limit resistor. Output current flows into/out of this pin through $R_{CL}$ . The output pin and the load are connected to the other side of $R_{CL}$ . |

| 4, 5       | CC_A  | Compensation capacitor connection for channel A. Select value based on Phase Compensation. See applicable section.                                                            |

| 6          | OUT_A | The output for channel A. Connect this pin to load and to the feedback resistors.                                                                                             |

| 8          | -IN_B | The inverting input for channel B.                                                                                                                                            |

| 9          | +IN_B | The non-inverting input for channel B.                                                                                                                                        |

| 12         | -Vs_B | The negative supply rail for channel B.                                                                                                                                       |

| 13         | +Vs_B | The positive supply rail for channel B.                                                                                                                                       |

| 15         | CL_B  | Connect to the current limit resistor. Output current flows into/out of this pin through $R_{CL}$ . The output pin and the load are connected to the other side of $R_{CL}$ . |

| 16, 17     | CC_B  | Compensation capacitor connection for channel B. Select value based on Phase Compensation. See applicable section.                                                            |

| 18         | OUT_B | The output for channel B. Connect this pin to load and to the feedback resistors.                                                                                             |

| 20         | -IN_A | The inverting input for channel A.                                                                                                                                            |

| 21         | +IN_A | The non-inverting input for channel A.                                                                                                                                        |

| 24         | -Vs_A | The negative supply rail for channel A.                                                                                                                                       |

| All Others | NC    | No connection.                                                                                                                                                                |

#### **SPECIFICATIONS**

Unless otherwise noted  $T_C$  = 25°C,  $C_C$  = 6.8pF. DC input specifications are  $\pm$  value given. Power supply voltage is typical rating. Specifications separated by / indicate values for the PA441DF, PA441DW and PA443DF respectively. (ex. PA441DF/PA441DW/PA443DF)

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                          | Symbol                             | PA441DF         |                 | PA441DW |     | PA443DF |     | Units  |

|----------------------------------------------------|------------------------------------|-----------------|-----------------|---------|-----|---------|-----|--------|

| raidilletei                                        | Зуппоот                            | Min             | Max             | Min     | Max | Min     | Max | Oilles |

| Supply Voltage, total                              | +V <sub>s</sub> to -V <sub>s</sub> |                 | 350             |         | *   |         | *   | V      |

| Output Current, continuous within SOA              | I <sub>O</sub>                     |                 | 60              |         | *   |         | *   | mA     |

| Output Current, peak                               | I <sub>O</sub>                     |                 | 120             |         | *   |         | *   | mA     |

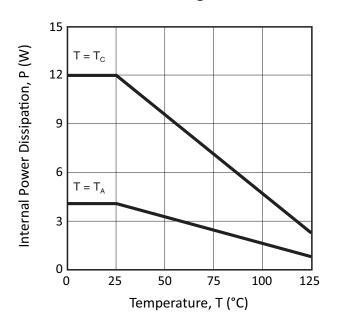

| Power Dissipation, continuous @ $T_c = 25$ °C $^1$ | $P_{D}$                            |                 | 12              |         | 9   |         | 12  | W      |

| Input Voltage, differential                        | V <sub>IN (Diff)</sub>             | -16             | +16             | *       | *   | *       | *   | V      |

| Input Voltage, common mode                         | V <sub>cm</sub>                    | -V <sub>S</sub> | +V <sub>S</sub> | *       | *   | *       | *   | V      |

| Temperature, pin solder, 10 sec                    |                                    |                 | 220             |         | 260 |         | 220 | °C     |

| Temperature, junction <sup>2</sup>                 | T <sub>J</sub>                     |                 | 150             |         | *   |         | *   | °C     |

| Temperature, storage                               |                                    | -65             | 150             | *       | *   | *       | *   | °C     |

| Temperature Range, powered (case)                  | T <sub>C</sub>                     | -40             | 125             | *       | *   | *       | *   | °C     |

- 1. Specifications are for individual amplifiers in PA443DF, unless otherwise noted.

- 2. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF. For guidance, refer to heatsink data sheet.

The PA441 and PA443 are constructed from MOSFET transistors. ESD handling procedures must be observed.

## **INPUT**

| Parameter                                   | Test Conditions                | Min                  | Тур              | Max             | Units  |

|---------------------------------------------|--------------------------------|----------------------|------------------|-----------------|--------|

| Offset Voltage, initial                     |                                |                      | 5                | 20              | mV     |

| Offset Voltage vs. Temperature <sup>1</sup> | 25° to 85°C                    |                      | 17               | 250             | μV/°C  |

| Offset Voltage vs. Temperature <sup>1</sup> | -25° to 25°C                   |                      | 18               | 500             | μV/°C  |

| Offset Voltage vs. Supply                   |                                |                      | 3                |                 | μV/V   |

| Offset Voltage vs. Time                     |                                |                      | 80               |                 | μV/kh  |

| Bias Current, initial <sup>2</sup>          |                                |                      | 50/100/50        | 200/200/<br>200 | рА     |

| Bias Current vs. Supply                     |                                |                      | 2                |                 | pA/V   |

| Offset Current, initial <sup>2</sup>        |                                |                      | 50/100/50        | 200/200/<br>200 | рА     |

| Input Impedance, DC                         |                                |                      | 10 <sup>11</sup> |                 | Ω      |

| Input Capacitance                           |                                |                      | 3                |                 | pF     |

| Common Mode Voltage Range                   |                                | +V <sub>S</sub> - 12 |                  |                 | V      |

| Common Mode Voltage Range                   |                                | -V <sub>S</sub> + 12 |                  |                 | V      |

| Common Mode Rejection, DC                   | V <sub>CM</sub> = ± 90V DC     | 84                   | 115              |                 | dB     |

| Noise, input referred                       | 20 kHz BW, Gain = 2, Cc = 68pF |                      | 12               |                 | μV RMS |

- 1. Sample tested by wafer to 95%

- 2. Rating applies with solder connection of heatslug to a minimum 1 square inch foil area of the printed circuit board.

## **GAIN**

| Parameter                         | Test Conditions   | Min | Тур | Max | Units |

|-----------------------------------|-------------------|-----|-----|-----|-------|

| Open Loop at 15 Hz                | $R_L = 5 k\Omega$ | 90  | 103 |     | dB    |

| Bandwidth, gain bandwidth product | @ 1 MHz           |     | 10  |     | MHz   |

| Power Bandwidth                   | 280V p-p          |     | 35  |     | kHz   |

## **OUTPUT**

| Parameter                      | Test Conditions                | Min                  | Тур                  | Max | Units |

|--------------------------------|--------------------------------|----------------------|----------------------|-----|-------|

| Voltage Swing                  | I <sub>O</sub> = 40mA          | ±V <sub>S</sub> ∓ 12 | ±V <sub>S</sub> ∓ 10 |     | V     |

| Current, peak <sup>1</sup>     |                                | 120                  |                      |     | mA    |

| Current, continuous            |                                | 60                   |                      |     | mA    |

| Settling Time to 0.1%          | 10V step, A <sub>V</sub> = -10 |                      | 2                    |     | μs    |

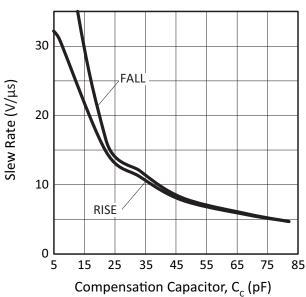

| Slew Rate                      | Cc = 4.7pF                     |                      | 32                   |     | V/µs  |

| Resistance, 10 mA <sup>2</sup> | R <sub>CL</sub> = 0 Ω          |                      | 91                   |     | Ω     |

| Resistance, 40 mA <sup>2</sup> | $R_{CL} = 0 \Omega$            |                      | 65                   |     | Ω     |

- 1. Guaranteed but not tested.

- 2. The selected value of  $\rm R_{\rm CL}$  must be added to the values given for total output resistance.

## **POWER SUPPLY**

| Parameter                       | Test Conditions | Min   | Тур    | Max    | Units |

|---------------------------------|-----------------|-------|--------|--------|-------|

| Voltage                         |                 | +/-10 | +/-150 | +/-175 | V     |

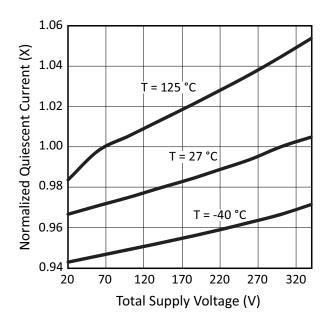

| Current, quiescent <sup>1</sup> |                 |       | 2.2    | 2.5    | mA    |

1. Specifications are for individual amplifiers in PA443DF, unless otherwise noted.

## **THERMAL**

| Parameter                                                             | Test Conditions        | Min | Тур | Max | Units |

|-----------------------------------------------------------------------|------------------------|-----|-----|-----|-------|

| PA441DF Resistance, AC junction to case                               | F > 60 Hz              |     | 6   | 7   | °C/W  |

| PA441DF Resistance, DC junction to case                               | F < 60 Hz              |     | 9   | 11  | °C/W  |

| PA441DF Resistance, junction to air <sup>1</sup>                      | Full temp range        |     | 25  |     | °C/W  |

| PA441DW Resistance, AC junction to case                               | F > 60 Hz              |     | 7   | 10  | °C/W  |

| PA441DW Resistance, DC junction to case                               | F < 60 Hz              |     | 12  | 14  | °C/W  |

| PA441DW Resistance, junction to air                                   | Full temp range        |     | 30  |     | °C/W  |

| PA443DF Resistance, AC junction to case, single amplifier             | F > 60 Hz              |     | 6   | 7   | °C/W  |

| PA443DF Resistance, DC junction to case, single amplifier             | F < 60 Hz              |     | 9   | 11  | °C/W  |

| PA443DF Resistance, AC junction to case, both amplifier <sup>2</sup>  | F > 60 Hz              |     | 3.3 | 4   | °C/W  |

| PA443DF Resistance, DC junction to case, both amplifiers <sup>3</sup> | F < 60 Hz              |     | 5   | 6   | °C/W  |

| PA443DF Resistance, junction to air <sup>1</sup>                      | Full temp range        |     | 25  |     | °C/W  |

| Temperature Range, case                                               | Meets full range specs | -25 |     | +85 | °C    |

- 1. Rating applies with solder connection of heatslug to a minimum 1 square inch foil area of the printed circuit board.

- $\label{eq:continuous} \textbf{2.} \ \ \textbf{Rating applies when power dissipation is equal in the two amplifiers.}$

- 3. Rating applies when power dissipation is equal in the two amplifiers.

## **TYPICAL PERFORMANCE GRAPHS**

Figure 3: Power Derating DF Package

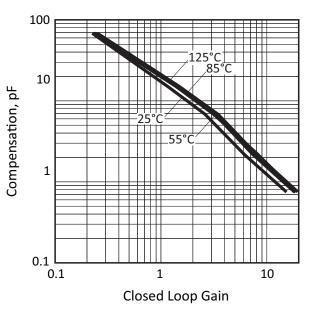

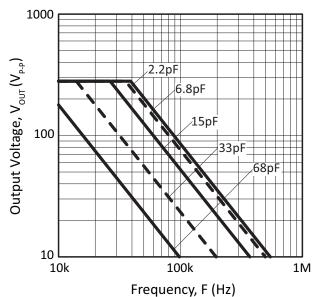

Figure 4: Gain and Compensation

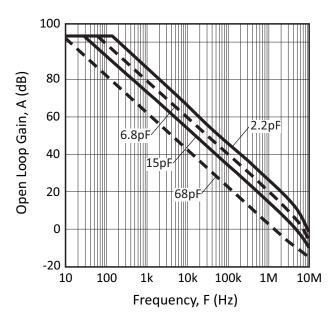

Figure 5: Small Signal Response

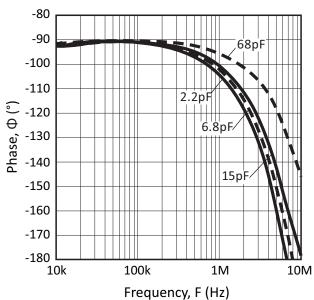

Figure 6: Phase Response

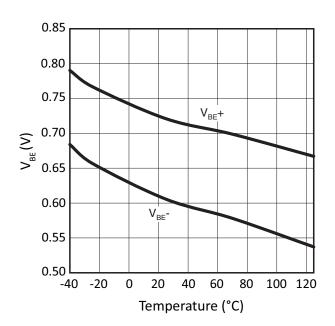

Figure 7: V<sub>BE</sub> for I<sub>LIMIT</sub>

Figure 8: Power Response

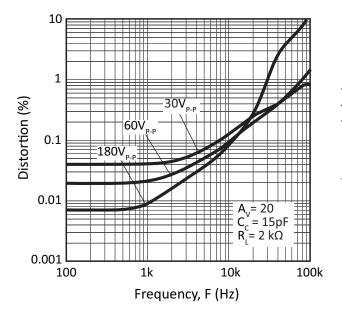

**Figure 9: Harmonic Distortion**

Figure 10: Slew Rate

Figure 11: Quiescent Current

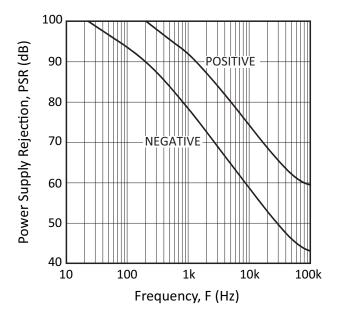

**Figure 13: Power Supply Rejection**

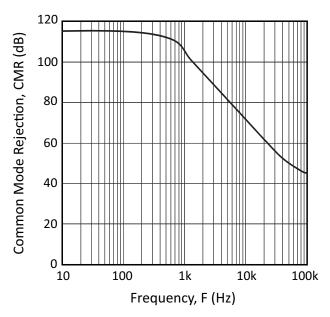

**Figure 12: Common Mode Rejection**

Figure 14: Output Voltage Swing

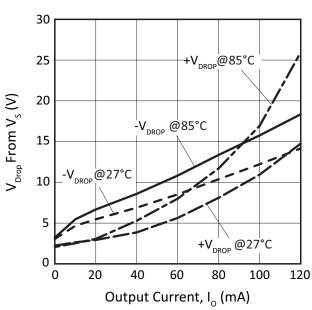

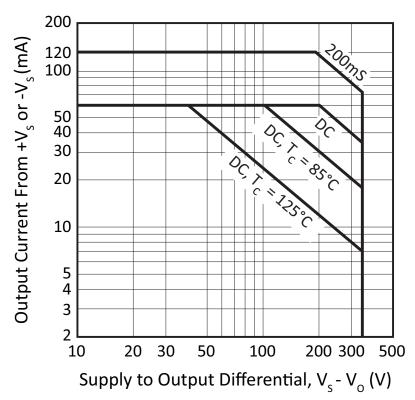

## **SAFE OPERATING AREA (SOA)**

The MOSFET output stage of the PA441 is not limited by second breakdown considerations as in bipolar output stages. However there are still three distinct limitations:

- 1. Voltage rating of the transistors.

- 2. Current handling capability of the die metallization.

- 3. Temperature of the output MOSFETs.

These limitations can be seen in the SOA (see Safe Operating Area graphs). Note that each pulse capability line shows a constant power level (unlike second breakdown limitations where power varies with voltage stress). These lines are shown for a case temperature of 25°C and correspond to thermal resistances (See Specification table, Thermal, Max, for thermal resistance of specific package types). Pulse stress levels for other case temperatures can be calculated in the same manner as DC power levels at different temperatures. The output stage is protected against transient flyback by the parasitic diodes of the output stage MOSFET structure. However for protection against sustained high energy flyback, external fast-recovery diodes must be used.

#### **GENERAL**

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexanalog.com for Apex Microtechnology's complete Application Notes library, Technical Seminar Workbook, and Evaluation Kits.

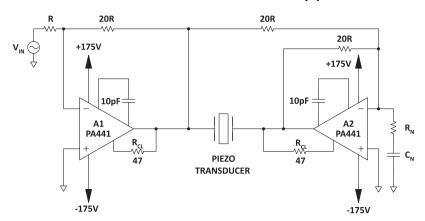

#### TYPICAL APPLICATION

Two PA441 amplifiers operated as a bridge driver for a piezo transducer provides a low cost 660 volt total drive capability. The  $R_N$   $C_N$  network serves to raise the apparent gain of A2 at high frequencies. If  $R_N$  is set equal to R the amplifiers can be compensated identically and will have matching bandwidths. For further information, read Application Note 20: "Bridge Mode Operation of Power Amplifiers"

Figure 16: Typical Applications (Low Cost 660V<sub>P-P</sub> Piezo Driver)

#### PHASE COMPENSATION

Open loop gain and phase shift both increase with increasing temperature. The GAIN AND COMPENSA-TION typical graph shows closed loop gain and phase compensation capacitor value relationships for four case temperatures. The curves are based on achieving a phase margin of 50°. Calculate the highest case temperature for the application (maximum ambient temperature and highest internal power dissipation) before choosing the compensation. Keep in mind that when working with small values of compensation, parasitics may play a large role in performance of the finished circuit. The compensation capacitor must be rated for at least the total voltage applied to the amplifier and should be a temperature stable type such as NPO or COG. The compensation capacitor value should be as large as possible to avoid possible overshoot issue if there are no input signal clipping circuits.

#### OTHER STABILITY CONCERNS

Compensation analysis is supported by 3 plots in the data sheet. These are the "SMALL SIGNAL RESPONSE", "PHASE COMPENSATION", and "GAIN AND COMPENSATION" plots. In the "SMALL SIGNAL RESPONSE" plot, the amplifier's open loop gain is shown for 4 different compensation capacitors. As an example, consider the open loop gain curve for Cc=68 pF. If your application needs a closed loop gain of 10 (20 dB), find the intersection of the horizontal line at 20 dB with the Cc = 68 pF curve. This intersection point, which occurs at about 100 kHz, defines the 3 dB BW (bandwidth) of the amplifier circuit. If you need more BW, the curve with Cc = 15 pF will give you a 3 dB BW of about 500 kHz. Next, go to the PHASE RESPONSE

plot. This plot shows that at 500 kHz the phase for Cc = 15 pF is about -95°. So the phase margin is about 85°. Now consider the GAIN and COMPENSATION plot. At a gain of 10 this plot shows that you could get by with a Cc as small as 2 pF. Returning to the SMALL SIGNAL RESPONSE plot, this figure shows that with Cc = 2 pF, the 20 dB closed loop gain now intersects the open loop gain curve at about 2 MHz. The price to pay for this increase in BW is a loss of phase margin, from 85° to 50°, because all of the data in the GAIN AND COMPENSATION plot is for a phase margin of 50°.

In most cases the amplifier output will drive some capacitive load. When this occurs, the open loop curves in the SMALL SIGNAL RESPONSE plot are modified by the appearance of a 2nd pole. In other words, the single pole roll-off which has a -1 slope, will break at some point into a -2 slope roll-off. When this happens, the choice of the 2 pF capacitor will not work and the circuit will oscillate. Stability analysis shows that in a stable circuit, the difference in slope at the intersection point between the open loop gain curve and the closed loop gain curve cannot be -2. So if, at the intersection point, the open loop gain has a -2 slope and the closed loop gain has a slope of 0, the circuit will oscillate. To prevent this, reduce the BW of your circuit by increasing the value of Cc. Larger values of Cc will allow the closed loop gain to intersect the open loop gain before the open loop gain curve breaks into its -2 slope. Use the largest value of Cc that you can, while still maintaining sufficient BW for your application. More advanced techniques of compensation are discussed in AN19 and AN47. For example, these notes discuss "feedback zero" compensation which shows how to stabilize an application circuit whose open loop gain curve has a -2 slope. Please contact Apex Application engineers for more information and support.

#### **CURRENT LIMIT**

For proper operation, the current limiting resistor, R<sub>CL</sub>, must be connected as shown in Figure 3, "External Connections". The current limit can be predicted as follows:

$$I_{LIMIT} = \frac{V_{BE}}{R_{CL}}$$

The " $V_{BE}$  for  $I_{LIMIT}$ " performance graph is used to find  $V_{BE}$ . On this graph, the  $V_{BE}$ + and  $V_{BE}$ - curves show the voltages across the current limiting resistor at which current limiting is turned on. The  $V_{BE}$ + curve shows these turn-on voltages when the amplifier is sourcing current, and the  $V_{BE}$ - curve shows these voltages when the amplifier is sinking current.

The current limit can be thought of as a ceiling or limit for safe operation. For continuous operation it is any value between the desired load current and 60 mA (as long as the curves on the SOA graph are not exceeded, please refer to section 3.4 for information on the SOA graph). As an example, suppose the desired load current for the application is 20 mA. In this case we may set a current limit of 30 mA. Starting with the smaller  $V_{BE}^-$  of 0.6 we have:

$$R_{CL} = \frac{0.6V}{0.03A} = 20\Omega$$

For the larger  $V_{BE}^{\phantom{BE}}$  this  $R_{CL}$  resistor will allow for a maximum current of:

$$I_{LIMIT} = \frac{0.7V}{20\Omega} = 35mA$$

This value is still acceptable because it is less than 60 mA. For the case of continuous load currents, check that the current limit does not exceed 60 mA.

The  $V_{BE}$  values used above are approximate and can vary with process. To allow for this possibility the user can reduce the  $V_{BE}$  = 0.6 value by 20%. This results in a  $R_{CL}$  value of 16  $\Omega$ . Using this same  $R_{CL}$  value and allowing for a 20% increase in the other  $V_{BE}$ , the current limit maximum is 52 mA.

The absolute minimum value of the current limiting resistor is bounded by the largest current and the largest  $V_{BE}$  in the application. The largest  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is determined by the coldest temperature in the application. In general the largest  $V_{BE}$  is determined by the coldest temperature in the application  $V_{BE}$  is determined by the coldest temperature in the application  $V_{BE}$  is determined by the coldest temperature in the applicatio

#### **HEATSINKING**

The PA441DF and PA443DF packages have a large exposed integrated copper heatslug to which the monolithic amplifier is directly attached. The solder connection of the heatslug to a minimum of 1 square inch foil area on the printed circuit board will result in thermal performance of 25°C/W junction to air rating of the PA441DF. Solder connection to an area of 1 to 2 square inches is recommended. This may be adequate heatsinking but the large number of variables involved suggest temperature measurements be made on the top of the package. Do not allow the temperature to exceed 85°C.

## **OVERVOLTAGE PROTECTION**

Although the PA441 can withstand differential input voltages up to 16V, in some applications additional external protection may be needed. Differential inputs exceeding 16V will be clipped by the protection circuitry. However, if more than a few milliamps of current is available from the overload source, the protection circuitry could be destroyed. For differential sources above 16V, adding series resistance limiting input current to 1mA will prevent damage. Alternatively, 1N4148 signal diodes connected anti-parallel across the input pins is usually sufficient. In more demanding applications where bias current is important, diode connected JFETs such as 2N4416 will be required. See Q1 and Q2 in Figure 17. In either case the differential input voltage will be clamped to 0.7V. This is sufficient overdrive to produce the maximum power bandwidth.

In the case of inverting circuits where the +IN pin is grounded, the diodes mentioned above will also afford protection from excessive common mode voltage. In the case of non-inverting circuits, clamp diodes from each input to each supply will provide protection. Note that these diodes will have substantial reverse bias voltage under normal operation and diode leakage will produce errors.

Some applications will also need over-voltage protection devices connected to the power supply rails. Unidirectional zener diode transient suppressors are recommended. The zeners clamp transients to voltages within the power supply rating and also clamp power supply reversals to ground. Whether the zeners are used or not the system power supply should be evaluated for transient performance including power-on overshoot and power-off polarity reversals as well as line regulation. See Z<sub>1</sub> and Z<sub>2</sub> in Figure 17.

+V<sub>s</sub> Z1

-IN

Q1

+V<sub>s</sub>

OUT

Z2

**Figure 17: Overvoltage Protection**

#### **PACKAGE OPTIONS**

| Part Number | Apex Package Style | Description                |

|-------------|--------------------|----------------------------|

| PA441DF     | DF                 | 24-pin MO-166              |

| PA441DW     | DW                 | 10-pin SIP                 |

| PA443DF     | DF                 | 24-pin MO-166 (dual OpAmp) |

#### PACKAGE STYLE DF

#### **PACKAGE STYLE DW**

#### NOTES:

- 1. Dimensions are inches & [mm].

- 2. Triangle printed on lid denotes pin 1.

- 3. Pins: Alloy 510 phosphor bronze plated with matte tin tin (150 300μ") over nickel (50 μ" max.) underplate.

- 4. Package Material: Alumina with hermetic glass seal.

#### **NEED TECHNICAL HELP? CONTACT APEX SUPPORT!**

For all Apex Microtechnology product questions and inquiries, call toll free 800-546-2739 in North America. For inquiries via email, please contact apex.support@apexanalog.com. International customers can also request support by contacting their local Apex Microtechnology Sales Representative. To find the one nearest to you, go to www.apexanalog.com

#### IMPORTANT NOTICE

Apex Microtechnology, Inc. has made every effort to insure the accuracy of the content contained in this document. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (expressed or implied). Apex Microtechnology reserves the right to make changes without further notice to any specifications or products mentioned herein to improve reliability. This document is the property of Apex Microtechnology and by furnishing this information, Apex Microtechnology grants no license, expressed or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Apex Microtechnology owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Apex Microtechnology integrated circuits or other products of Apex Microtechnology. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

APEX MICROTECHNOLOGY PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN PRODUCTS USED FOR LIFE SUPPORT, AUTOMOTIVE SAFETY, SECURITY DEVICES, OR OTHER CRITICAL APPLICATIONS. PRODUCTS IN SUCH APPLICATIONS ARE UNDERSTOOD TO BE FULLY AT THE CUSTOMER OR THE CUSTOMER'S RISK.

Apex Microtechnology, Apex and Apex Precision Power are trademarks of Apex Microtechnology, Inc. All other corporate names noted herein may be trademarks of their respective holders.