# INTEGRATED CIRCUITS

Product data Supersedes data of 1990 Mar 01

2003 Feb 05

Philips Semiconductors

## 74F299

#### **FEATURES**

- Common parallel I/O for reduced pin count

- Additional serial inputs and outputs for expansion

- Four operating modes: Shift left, shift right, load and store

- 3-State outputs for bus-oriented applications

## DESCRIPTION

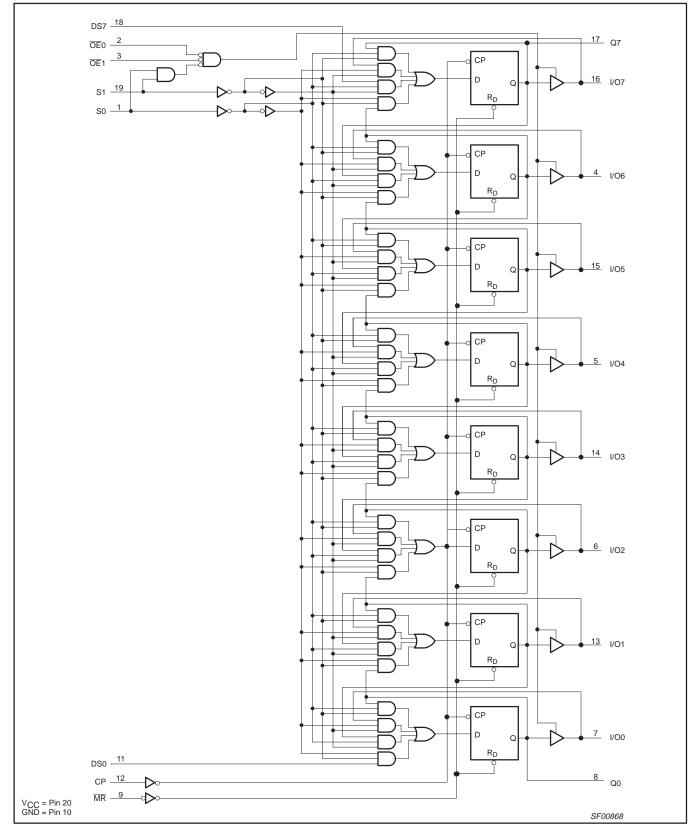

The 74F299 is an 8-bit universal shift/storage register with 3-State outputs. Four modes of operation are possible: Hold (store), shift left, shift right and parallel load. The parallel load inputs and flip-flop outputs are multiplexed to reduce the total number of package pins. Additional outputs are provided for flip-flops Q0 and Q7 to allow easy serial cascading. A separate active-LOW Master Reset is used to reset the register.

The 74F299 contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous shift left, shift right, parallel load and hold operations. The type of operation is determined by S0 and S1, as shown in the Function Table. All flip-flop outputs are brought out through 3-State buffers to separate I/O pins that also serve as data inputs in the parallel load mode. Q0 and Q7 are also brought out on other pins for expansion in serial shifting of longer words.

A LOW signal on  $\overline{\text{MR}}$  overrides the Select and CP inputs and resets the flip-flops. All other state changes are initiated by the rising edge of the clock. Inputs can change when the clock is in either state provided only that the recommended set-up and hold times, relative to the rising edge of clock are observed.

A HIGH signal on either  $\overline{OE0}$  or  $\overline{OE1}$  disables the 3-State buffers and puts the I/O pins in the high impedance state. In this condition the shift, hold, load and reset operations can still occur. The 3-State buffers are also disabled by High signals on both S0 and S1 in preparation for a parallel load operation.

## INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

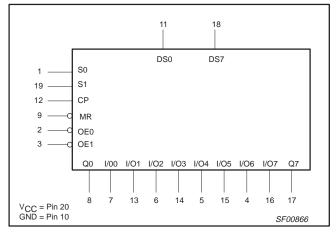

| S0 1          | 20 V <sub>CC</sub> |

|---------------|--------------------|

| <u>OE</u> 0 2 | 19 S1              |

| OE1 3         | 18 DS7             |

| I/O6 4        | 17 Q7              |

| I/O4 5        | 16 I/O7            |

| I/O2 6        | 15 I/O5            |

| I/O0 7        | 14 I/O3            |

| Q0 8          | 13 I/O1            |

| MR 9          | 12 CP              |

| GND 10        | 11 DS0             |

| TYPE   | TYPICAL f <sub>MAX</sub> | TYPICAL<br>SUPPLY CURRENT<br>(TOTAL) |  |  |

|--------|--------------------------|--------------------------------------|--|--|

| 74F299 | 115 MHz                  | 58 mA                                |  |  |

SF00865

## **ORDERING INFORMATION**

**PIN CONFIGURATION**

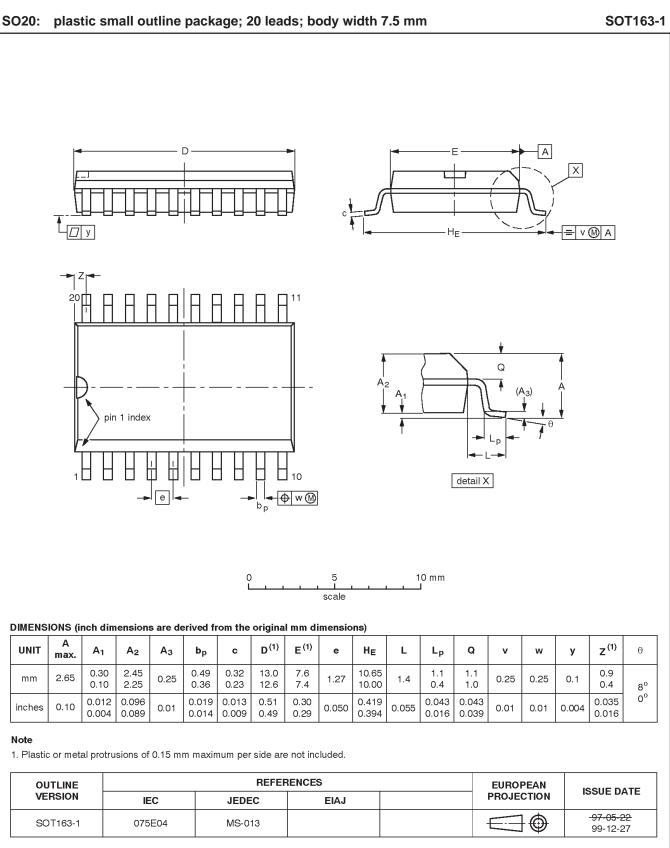

|                    | ORDER CODE                                                                              |           |  |

|--------------------|-----------------------------------------------------------------------------------------|-----------|--|

| DESCRIPTION        | COMMERCIAL<br>RANGE<br>V <sub>CC</sub> = 5 V ±10%,<br>T <sub>amb</sub> = 0 °C to +70 °C | PKG DWG # |  |

| 20-pin plastic DIP | N74F299N                                                                                | SOT146-1  |  |

| 20-pin plastic SOL | N74F299D                                                                                | SOT163-1  |  |

| PINS     | DESCRIPTION                                  | 74F(U.L.)<br>HIGH / LOW | LOAD VALUE<br>HIGH / LOW |

|----------|----------------------------------------------|-------------------------|--------------------------|

| DS0      | Serial data input for right shift            | 1.0 / 1.0               | 20 µA / 0.6 mA           |

| DS7      | Serial data input for left shift             | 1.0 / 1.0               | 20 µA / 0.6 mA           |

| S0, S1   | Mode select inputs                           | 1.0 / 2.0               | 20 μA / 1.2 mA           |

| СР       | Clock pulse input (Active rising edge)       | 1.0 / 1.0               | 20 µA / 0.6 mA           |

| MR       | Asynchronous Master Reset input (Active LOW) | 1.0 / 1.0               | 20 µA / 0.6 mA           |

| OE0, OE1 | Output Enable input (Active LOW)             | 1.0 / 1.0               | 20 µA / 0.6 mA           |

| Q0, Q7   | Serial outputs                               | 50 / 33                 | 1.0 mA / 20 mA           |

| I/On     | Multiplexed parallel data inputs             | 3.5 / 1.0               | 70 μA / 0.6 mA           |

| 1/011    | 3-State parallel outputs                     | 150 / 40                | 3.0 mA / 24 mA           |

NOTE: One (1.0) FAST Unit Load (U.L.) is defined as: 20  $\mu$ A in the HIGH State and 0.6 mA in the LOW state.

# 74F299

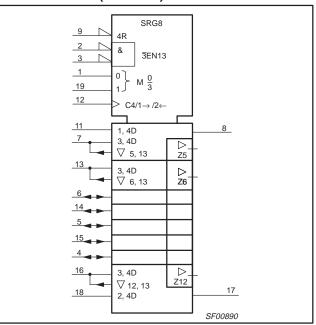

LOGIC SYMBOL

## LOGIC SYMBOL (IEEE/IEC)

### **FUNCTION TABLE**

| INPUTS |    | INP | UTS |    |                                                              |

|--------|----|-----|-----|----|--------------------------------------------------------------|

| OEn    | MR | S1  | S0  | СР | OPERATING MODE                                               |

| L      | L  | Х   | Х   | Х  | Asynchronous Reset; Q0 – Q7 = LOW                            |

| L      | Н  | Н   | Н   | ↑  | Parallel load; I/On $\rightarrow$ Qn (I/On outputs disabled) |

| L      | Н  | L   | Н   | ↑  | Shift right; DS0 $\rightarrow$ Q0, Q0 $\rightarrow$ Q1, etc. |

| L      | Н  | Н   | L   | ↑  | Shift left; DS7 $\rightarrow$ Q7, Q7 $\rightarrow$ Q6, etc.  |

| L      | Н  | L   | L   | Х  | Hold                                                         |

| Н      | Х  | X   | Х   | Х  | Outputs in High-Z                                            |

H = HIGH voltage level

L = LOW voltage level

X = Don't care  $\uparrow = LOW-to-HIGH clock transition$

## LOGIC DIAGRAM

74F299

### **ABSOLUTE MAXIMUM RATINGS**

(Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free-air temperature range.)

| SYMBOL           | PARAMETER                                      |        | RATING UN                |    |  |  |

|------------------|------------------------------------------------|--------|--------------------------|----|--|--|

| V <sub>CC</sub>  | Supply voltage                                 |        | -0.5 to +7.0 V           |    |  |  |

| V <sub>IN</sub>  | Input voltage                                  |        | -0.5 to +7.0             | V  |  |  |

| I <sub>IN</sub>  | Input current                                  |        | -30 to +5                | mA |  |  |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state |        | -0.5 to +V <sub>CC</sub> | V  |  |  |

|                  | Current emplied to cutout in LOW output state  | Q0, Q7 | 40                       | mA |  |  |

| IOUT             | Current applied to output in LOW output state  | 48     | mA                       |    |  |  |

| T <sub>amb</sub> | Operating free-air temperature range           |        | 0 to +70                 | °C |  |  |

| T <sub>stg</sub> | Storage temperature                            |        | -65 to +150              | °C |  |  |

## **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                            |        |     | UNIT |     |    |

|------------------|--------------------------------------|--------|-----|------|-----|----|

|                  |                                      |        | MIN | NOM  | MAX |    |

| V <sub>CC</sub>  | Supply voltage                       | 4.5    | 5.0 | 5.5  | V   |    |

| VIH              | HIGH-level input voltage             | 2.0    |     |      | V   |    |

| V <sub>IL</sub>  | LOW-level input voltage              |        |     | 0.8  | V   |    |

| I <sub>IK</sub>  | Input clamp current                  |        |     | -18  | mA  |    |

|                  |                                      | Q0, Q7 |     |      | -1  | mA |

| юн               | HIGH-level output current            | l/On   |     |      | -3  | mA |

|                  |                                      | Q0, Q7 |     |      | 20  | mA |

| IOL              | LOW-level output current             | l/On   |     |      | 24  | mA |

| T <sub>amb</sub> | Operating free-air temperature range |        | 0   |      | 70  | °C |

## **DC ELECTRICAL CHARACTERISTICS**

Over recommended operating free-air temperature range unless otherwise noted.

| CVMDO:                             | DADAMETER                                               |                  |                                                 |                                               |                       |      |        |      |    |

|------------------------------------|---------------------------------------------------------|------------------|-------------------------------------------------|-----------------------------------------------|-----------------------|------|--------|------|----|

| SYMBOL                             | PARAMETER                                               |                  | TE                                              | MIN                                           | TYP <sup>2</sup>      | MAX  | X UNIT |      |    |

|                                    |                                                         | 00.07            |                                                 | 1 1                                           | ±10%V <sub>CC</sub>   | 2.5  |        |      | V  |

| M                                  |                                                         | Q0, Q7           | $V_{CC} = MIN,$                                 | I <sub>OH</sub> = -1 mA                       | ±5%V <sub>CC</sub>    | 2.7  | 3.4    |      | V  |

| V <sub>OH</sub>                    | HIGH-level output voltage                               | 1/0.1            | V <sub>IL</sub> = MAX,<br>V <sub>IH</sub> = MIN |                                               | ±10%V <sub>CC</sub>   | 2.4  |        |      | V  |

|                                    |                                                         | I/On             |                                                 | I <sub>OH</sub> = -3 mA                       | ±5%V <sub>CC</sub>    | 2.7  | 3.3    |      | V  |

| M                                  |                                                         |                  | $V_{CC} = MIN,$                                 |                                               | ±10%V <sub>CC</sub>   |      | 0.35   | 0.50 | V  |

| V <sub>OL</sub>                    | LOW-level output voltage                                |                  | V <sub>IL</sub> = MAX,<br>V <sub>IH</sub> = MIN | I <sub>OL</sub> = MAX                         | ±5%V <sub>CC</sub>    |      | 0.35   | 0.50 | V  |

| V <sub>IK</sub>                    | Input clamp voltage                                     |                  | V                                               |                                               | -0.73                 | -1.2 | V      |      |    |

| l <sub>l</sub>                     | Input current at maximum                                | others           | others $V_{CC} = MAX, V_I = 7.0 V$              |                                               |                       |      |        | 100  | μA |

|                                    | input voltage                                           |                  | $V_{CC} = 5.5V, V_1 = 5.5 V$                    |                                               |                       |      |        | 1    | mA |

| IIH                                | HIGH-level input current                                | except<br>I/On   | V <sub>CC</sub>                                 | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.7 V |                       |      |        | 20   | μA |

| 1                                  |                                                         | S0, S1           | N/                                              |                                               |                       |      |        | -1.2 | mA |

| IIL                                | LOW-level input current                                 | others           | VCC                                             | $_{\rm C}$ = MAX, $V_{\rm I}$ = 0.9           | o v                   |      |        | -0.6 | mA |

| I <sub>IH +</sub> I <sub>OZH</sub> | Off-state output current,<br>HIGH-level voltage applied | l/On             | V <sub>CC</sub>                                 | = MAX, V <sub>O</sub> = 2.                    | 7 V                   |      |        | 70   | μA |

| I <sub>IL +</sub> I <sub>OZL</sub> | Off-state output current<br>LOW-level voltage applied   | only             | V <sub>CC</sub>                                 | $V_{CC}$ = MAX, $V_{O}$ = 0.5 V               |                       |      |        | -0.6 | mA |

| I <sub>OS</sub>                    | Short-circuit output current <sup>3</sup>               |                  |                                                 | V <sub>CC</sub> = MAX                         |                       | -60  |        | -150 | mA |

|                                    |                                                         | I <sub>CCH</sub> |                                                 |                                               |                       |      | 55     | 60   | mA |

| I <sub>CC</sub>                    | Supply current (total)                                  | ICCL             |                                                 | $V_{CC} = MAX$                                | V <sub>CC</sub> = MAX |      |        | 90   | mA |

|                                    |                                                         | I <sub>CCZ</sub> | 1                                               |                                               |                       |      | 65     | 95   | mA |

#### NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$ . 3. Not more than one output should be shorted at a time. For testing  $I_{OS}$ , the use of high-speed test apparatus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a HIGH output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, I<sub>OS</sub> tests should be performed last.

## AC ELECTRICAL CHARACTERISTICS

| SYMBOL                                   | PARAMETER                             | TEST CONDITIONS | v                        | <sub>mb</sub> = +25<br>cc = +5.0<br>0 pF, R <sub>L</sub> = | v          | T <sub>amb</sub> = 0 °C<br>V <sub>CC</sub> = +5.0<br>C <sub>L</sub> = 50 pF, | UNIT       |              |          |

|------------------------------------------|---------------------------------------|-----------------|--------------------------|------------------------------------------------------------|------------|------------------------------------------------------------------------------|------------|--------------|----------|

|                                          |                                       |                 |                          | MIN                                                        | TYP        | MAX                                                                          | MIN        | MAX          |          |

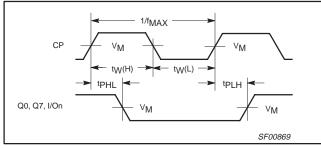

| f <sub>MAX</sub> Maximum clock frequency |                                       | I/O             | Waveform 1               | 70                                                         | 100        |                                                                              | 70         |              | MHz      |

| 'MAX                                     | Maximum clock frequency               | Qn              | vvaveioiiii i            | 85                                                         | 115        |                                                                              | 85         |              | MHz      |

| t <sub>PLH</sub><br>t <sub>PHL</sub>     | Propagation delay<br>CP to Q0 or Q7   |                 | Waveform 1               | 4.0<br>4.5                                                 | 5.0<br>6.0 | 7.5<br>8.0                                                                   | 3.5<br>4.5 | 8.5<br>8.5   | ns<br>ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub>     | Propagation delay<br>CP to I/On       |                 | Waveform 1               | 4.0<br>4.0                                                 | 6.0<br>6.5 | 9.0<br>9.0                                                                   | 4.0<br>4.0 | 10.0<br>10.0 | ns<br>ns |

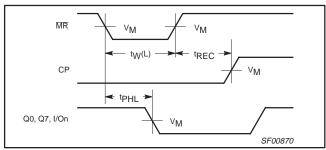

| t <sub>PHL</sub>                         | Propagation delay<br>MR to Q0 or Q7   |                 | Waveform 2               | 5.5                                                        | 7.5        | 9.5                                                                          | 5.5        | 10.5         | ns       |

| t <sub>PHL</sub>                         | Propagation delay<br>MR to I/On       |                 | Waveform 2               | 5.5                                                        | 7.5        | 10.0                                                                         | 5.5        | 10.5         | ns       |

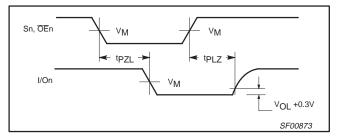

| t <sub>PZH</sub><br>t <sub>PZL</sub>     | Output Enable time<br>Sn, OE to I/On  |                 |                          | 3.5<br>4.0                                                 | 6.0<br>7.5 | 8.0<br>10.0                                                                  | 3.5<br>4.0 | 9.0<br>11.0  | ns<br>ns |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub>     | Output Disable time<br>Sn, OE to I/On |                 | Waveform 4<br>Waveform 5 | 2.5<br>1.5                                                 | 4.5<br>2.5 | 7.0<br>5.5                                                                   | 2.5<br>1.5 | 8.0<br>6.5   | ns<br>ns |

## AC SET-UP REQUIREMENTS

|                                          |                                                                            | TEST CONDITIONS |            |                                                                         |     |                                                                              |      |          |

|------------------------------------------|----------------------------------------------------------------------------|-----------------|------------|-------------------------------------------------------------------------|-----|------------------------------------------------------------------------------|------|----------|

| SYMBOL                                   | PARAMETER                                                                  |                 | v          | <sub>mb</sub> = +25 °<br><sub>CC</sub> = +5.0<br>0 pF, R <sub>L</sub> = | v   | T <sub>amb</sub> = 0 °C<br>V <sub>CC</sub> = +5.0<br>C <sub>L</sub> = 50 pF, | UNIT |          |

|                                          |                                                                            |                 | MIN        | TYP                                                                     | MAX | MIN                                                                          | MAX  |          |

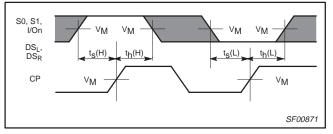

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Set-up time, HIGH or LOW<br>S0 or S1 to CP                                 | Waveform 3      | 6.5<br>6.5 |                                                                         |     | 7.5<br>7.5                                                                   |      | ns<br>ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, HIGH or LOW<br>S0 or S1 to CP                                   | Waveform 3      | 0<br>0     |                                                                         |     | 0<br>0                                                                       |      | ns<br>ns |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Set-up time, HIGH or LOW<br>I/On, DS <sub>L</sub> or DS <sub>R</sub> to CP | Waveform 3      | 3.5<br>3.5 |                                                                         |     | 4.0<br>4.0                                                                   |      | ns<br>ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, HIGH or LOW<br>I/On, DS <sub>L</sub> or DS <sub>R</sub> to CP   | Waveform 3      | 0<br>0     |                                                                         |     | 0<br>0                                                                       |      | ns<br>ns |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse width, HIGH or LOW                                                | Waveform 1      | 5.0<br>4.5 |                                                                         |     | 5.0<br>4.5                                                                   |      | ns       |

| t <sub>w</sub> (L)                       | MR Pulse width, LOW                                                        | Waveform 2      | 4.5        |                                                                         |     | 4.5                                                                          |      | ns       |

| t <sub>rec</sub>                         | Recovery time, MR to CP                                                    | Waveform 2      | 4.0        |                                                                         |     | 4.0                                                                          |      | ns       |

# 74F299

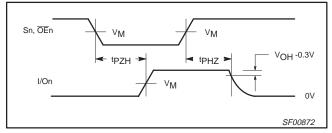

## AC WAVEFORMS

For all waveforms,  $V_M = 1.5 V$

The shaded areas indicate when the input is permitted to change for predictable output performance.

Waveform 1. Propagation delay, clock input to output, clock width, and maximum clock frequency

Waveform 3. Set-up and hold times

Waveform 5. 3-State Output Enable time to LOW level and Output Disable time from LOW level

Waveform 2. Master Reset pulse width, Master Reset to output delay, and Master Reset to clock recovery time

Waveform 4. 3-State Output Enable time to HIGH level and Output Disable time from HIGH level

## 74F299

Product data

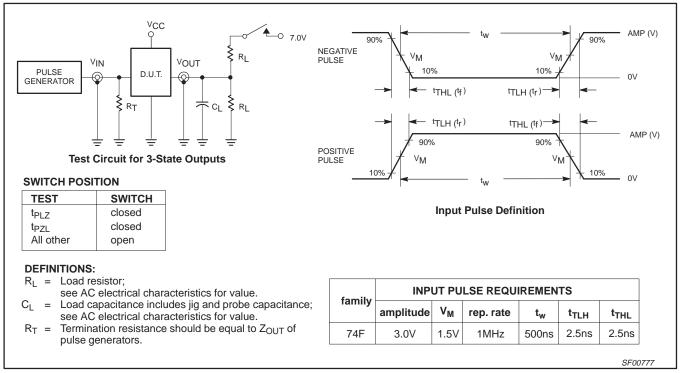

#### **TEST CIRCUIT AND WAVEFORM**

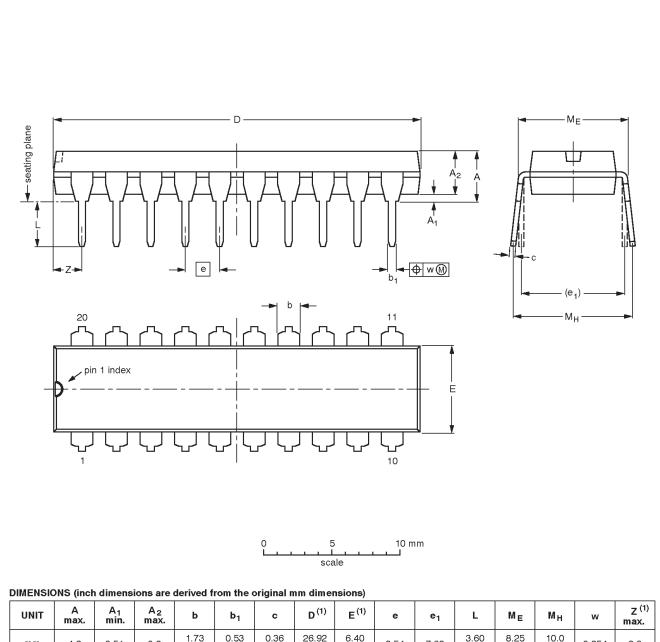

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | с              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | Μ <sub>E</sub> | М <sub>Н</sub> | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.30   | 0.53<br>0.38   | 0.36<br>0.23   | 26.92<br>26.54   | 6.40<br>6.22     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80   | 10.0<br>8.3    | 0.254 | 2.0                      |

| inches | 0.17      | 0.020                  | 0.13                   | 0.068<br>0.051 | 0.021<br>0.015 | 0.014<br>0.009 | 1.060<br>1.045   | 0.25<br>0.24     | 0.10 | 0.30           | 0.14<br>0.12 | 0.32<br>0.31   | 0.39<br>0.33   | 0.01  | 0.078                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | RENCES | EUROPEAN   | ISSUE DATE                       |

|----------|-----|--------|--------|------------|----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ   | PROJECTION | ISSUE DATE                       |

| SOT146-1 |     | MS-001 | SC-603 |            | <del>-95-05-24</del><br>99-12-27 |

# DIP20: plastic dual in-line package; 20 leads (300 mil)

8-bit universal shift/storage register (3-State)

SOT146-1

#### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                                   |  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| _3  | 20030205 | Product data (9397 750 11037); ECN 853-0365 29307 of 17 December 2002.<br>Supersedes Product specification (9397 750 05117) of 01 March 1990. |  |

|     |          | Modifications:                                                                                                                                |  |

|     |          | <ul> <li>Delete all references to DB package. Package option was discontinued.</li> </ul>                                                     |  |

| _2  | 19900301 | Product specification (9397 750 05117); ECN 853-0365 29307 of 01 March 1990.                                                                  |  |

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax:

sales.addresses@www.semiconductors.philips.com

For sales offices addresses send e-mail to:

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2003 All rights reserved. Printed in U.S.A.

Date of release: 02-03

9397 750 11037

Let's make things better.

Document order number:

PHILIPS