# Product Preview

# Single-Phase Voltage Regulator with SVID Interface for Computing Applications

# High Switching Frequency, High Efficiency, Integrated Power MOSFETs

The NCP81109F, a single-phase synchronous buck regulator, integrates power MOSFETs to provide a high-efficiency and compact-footprint power management solution for new generation computing CPUs. The device is able to deliver up to 14 A TDC output current on an adjustable output with SVID interface. Operating in high switching frequency up to 1.2 MHz allows employing small size inductors and capacitors while maintaining high efficiency due to integrated solution with high performance power MOSFETs. Current-mode RPM control with feedforward from both input power supply and output voltage ensures stable operation over wide operation condition. The NCP81109F is in a QFN48 6 x 6 mm package.

### Features

- Meets Intel® Server Specifications

- 5 V to 20 V Input Voltage Range

- 1.0 V/1.5 V Fixed Boot Voltage

- Adjustable Output Voltage with SVID Interface

- Integrated Gate Driver and Power MOSFETs

- Up to 14 A TDC Output Current

- 500 kHz ~ 1.2 MHz Switching Frequency

- Current-Mode RPM Control

- Programmable SVID Address and ICCMax

- Programmable DVID Feed-Forward to Support Fast DVID

- Feedforward Operation for Input Supply Voltage and Output Voltage

- Output Over-Voltage and Under-Voltage Protections

- External Current Limitation Programming with Inductor Current Sense

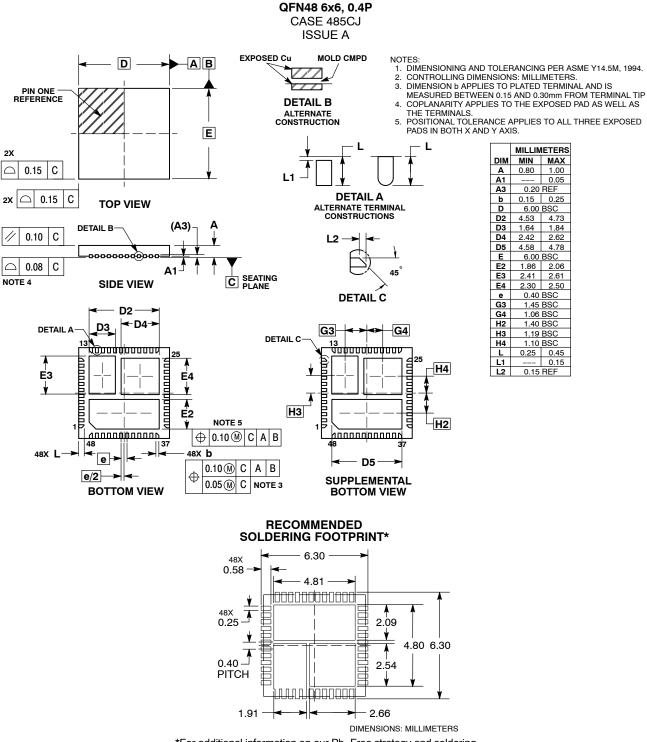

- QFN48, 6 x 6 mm, 0.4 mm Pitch Package

- This is a Pb–Free Device

### **Typical Applications**

• Server Applications

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

## **ON Semiconductor®**

http://onsemi.com

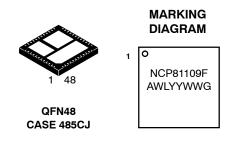

| NCP81109 | 9F = Specific Device Code |

|----------|---------------------------|

| А        | = Assembly Location       |

| WL       | = Wafer Lot               |

| YY       | = Year                    |

| WW       | = Work Week               |

| G        | = Pb-Free Package         |

|          |                           |

### **ORDERING INFORMATION**

| Device         | Package            | Shipping <sup>†</sup> |

|----------------|--------------------|-----------------------|

| NCP81109FMNTXG | QFN48<br>(Pb–Free) | 2500 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

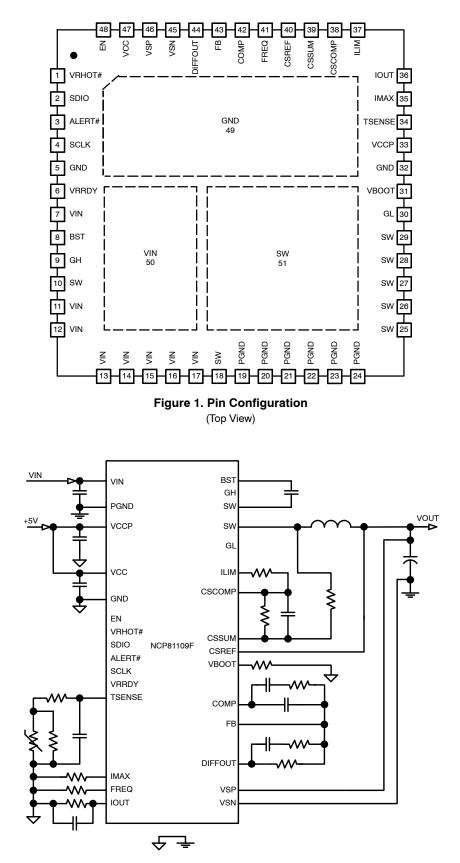

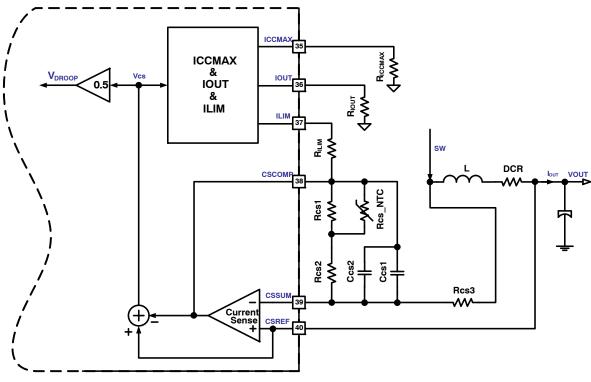

Figure 2. Typical Application Circuit

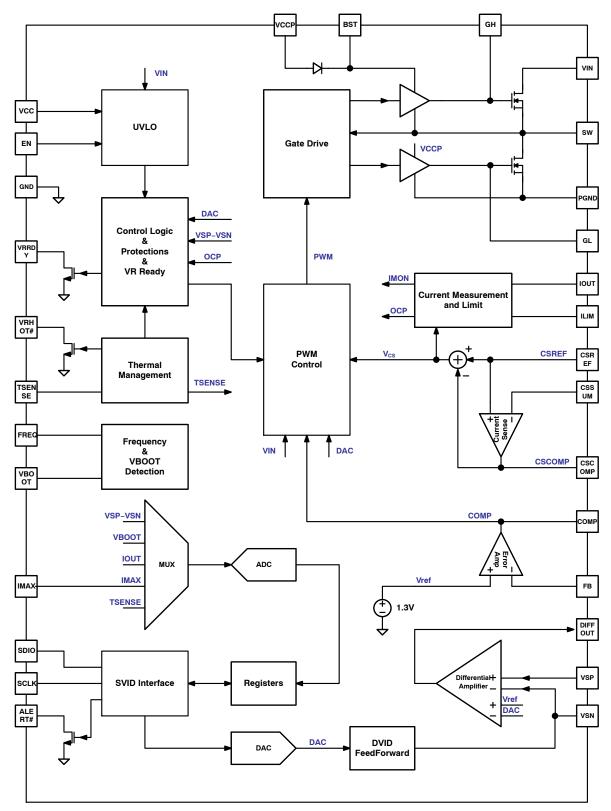

Figure 3. Functional Block Diagram

### **PIN DESCRIPTION**

| Pin                 | Name    | Туре                   | Description                                                                                                                                                                                                                                                                                             |

|---------------------|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | VRHOT#  | Logic Output           | VR HOT. Logic low output represents over temperature.                                                                                                                                                                                                                                                   |

| 2                   | SDIO    | Logic Bidirectional    | Serial Data IO Port. Data port of SVID interface.                                                                                                                                                                                                                                                       |

| 3                   | ALERT#  | Logic Output           | ALERT. Open-drain output. Provides a logic low valid alert signal of SVID interface.                                                                                                                                                                                                                    |

| 4                   | SCLK    | Logic Input            | Serial Clock. Clock input of SVID interface.                                                                                                                                                                                                                                                            |

| 5, 32,<br>49        | GND     | Analog Ground          | Analog Ground. Ground of internal control circuits. Must be connected to the system ground.                                                                                                                                                                                                             |

| 6                   | VRRDY   | Logic Output           | Voltage Regulator Ready. Open-drain output. Provides a logic high valid power good output signal, indicating the regulator's output is in regulation window.                                                                                                                                            |

| 7,<br>11–17,<br>50  | VIN     | Power Input            | <b>Power Supply Input.</b> These pins are the power supply input pins of the device, which are connected to drain of internal high-side power MOSFET. 22 $\mu$ F or more ceramic capacitors must bypass this input to power ground. The capacitors should be placed as close as possible to these pins. |

| 8                   | BST     | Power<br>Bidirectional | <b>Bootstrap.</b> Provides bootstrap voltage for the high–side gate driver. A 0.1 $\mu$ F ~ 1 $\mu$ F ceramic capacitor is required from this pin to SW (pin 10). A 1 – 2 $\Omega$ resistor may be employed in series with the BST cap to reduce switching noise and ringing when needed.               |

| 9                   | GH      | Analog Output          | Gate of High-Side MOSFET. Directly connected with the gate of the high-side power MOSFET.                                                                                                                                                                                                               |

| 10                  | SW      | Power Return           | Switching Node. Provides a return path for integrated high-side gate driver. It is internally connected to source of high-side MOSFET.                                                                                                                                                                  |

| 18,<br>25–29,<br>51 | SW      | Power Output           | Switch Node. Pins to be connected to an external inductor. These pins are interconnection between internal high-side MOSFET and low-side MOSFET.                                                                                                                                                        |

| 19–24               | PGND    | Power Ground           | <b>Power Ground.</b> These pins are the power supply ground pins of the device, which are connected to source of internal low-side power MOSFET. Must be connected to the system ground.                                                                                                                |

| 30                  | GL      | Analog Output          | Gate of Low-Side MOSFET. Directly connected with the gate of the low-side power MOSFET.                                                                                                                                                                                                                 |

| 31                  | VBOOT   | Analog Input           | Boot-Up Voltage. A resistor from this pin to ground programs SVID address.                                                                                                                                                                                                                              |

| 33                  | VCCP    | Analog Power           | <b>Voltage Supply of Gate Driver.</b> Power supply input pin of internal gate driver. A 4.7 $\mu$ F or larger ceramic capacitor bypasses this input to ground. This capacitor should be placed as close as possible to this pin.                                                                        |

| 34                  | TSENSE  | Analog                 | Temperature Sense. An external temperature sense network is connected to this pin.                                                                                                                                                                                                                      |

| 35                  | IMAX    | Analog Input           | Current Maximum. A resistor from this pin to ground programs IMAX.                                                                                                                                                                                                                                      |

| 36                  | IOUT    | Analog Output          | <b>OUT Current Monitor.</b> Provides output signal representing output current by connecting a resistor from this pin to ground. Shorting this pin to ground disables IMON function.                                                                                                                    |

| 37                  | ILIM    | Analog Output          | <b>Limit of Current.</b> A resistor from this pin to CSCOMP programs over-current threshold with inductor current sense.                                                                                                                                                                                |

| 38                  | CSCOMP  | Analog Output          | Current Sense COMP. Output pin of current sense amplifier.                                                                                                                                                                                                                                              |

| 39                  | CSSUM   | Analog Input           | Current Sense SUM. Inverting input of current sense amplifier.                                                                                                                                                                                                                                          |

| 40                  | CSREF   | Analog Input           | Current Sense Reference. Non-Inverting input of current sense amplifier.                                                                                                                                                                                                                                |

| 41                  | FREQ    | Analog Input           | Frequency. A resistor from this pin to ground programs switching frequency.                                                                                                                                                                                                                             |

| 42                  | COMP    | Analog                 | Compensation. Output pin of error amplifier.                                                                                                                                                                                                                                                            |

| 43                  | FB      | Analog Input           | Feedback. Inverting input to error amplifier.                                                                                                                                                                                                                                                           |

| 44                  | DIFFOUT | Analog Output          | Differential Amplifier Output. Output pin of differential voltage sense amplifier.                                                                                                                                                                                                                      |

| 45                  | VSN     | Analog Input           | Voltage Sense Negative Input. Inverting input of differential voltage sense amplifier. It is also used for DVID feed forward function with an external resistor.                                                                                                                                        |

|                     | 1       | 1                      |                                                                                                                                                                                                                                                                                                         |

#### PIN DESCRIPTION

| Pin | Name | Туре         | Description                                                                                                                                                                                                               |

|-----|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47  | VCC  | Analog Power | <b>Voltage Supply of Controller.</b> Power supply input pin of control circuits. A 1 $\mu F$ or larger ceramic capacitor bypasses this input to ground. This capacitor should be placed as close as possible to this pin. |

| 48  | EN   | Logic Input  | Enable. Logic high enables the device and logic low makes the device in standby mode.                                                                                                                                     |

#### MAXIMUM RATINGS

|                                                                             |                                   | Va                   |                   |      |

|-----------------------------------------------------------------------------|-----------------------------------|----------------------|-------------------|------|

| Rating                                                                      | Symbol                            | Min                  | Max               | Unit |

| Power Supply Voltage to PGND                                                | V <sub>VIN</sub>                  |                      | 30                | V    |

| Switch Node to PGND                                                         | V <sub>SW</sub>                   |                      | 30                | V    |

| Analog Supply Voltage to GND                                                | V <sub>CC,</sub> V <sub>CCP</sub> | -0.3                 | 6.5               | V    |

| BST to PGND                                                                 | BST_PGND                          | -0.3                 | 33<br>38 (<50 ns) | V    |

| BST to SW                                                                   | BST_SW                            | -0.3                 | 6.5               | V    |

| GH to SW                                                                    | GH                                | -0.3<br>-2 (<200 ns) | BST+0.3           | V    |

| GL to GND                                                                   | GL                                | -0.3<br>-2 (<200 ns) | VCCP+0.3          | V    |

| VSN to GND                                                                  | VSN                               | -0.3                 | 0.3               | V    |

| IOUT                                                                        | IOUT                              | -0.3                 | 2.5               | V    |

| PGND to GND                                                                 | PGND                              | -0.3                 | 0.3               | V    |

| Other Pins                                                                  |                                   | -0.3                 | VCC+0.3           | V    |

| Latch up Current: (Note 1)<br>All pins, except digital pins<br>Digital pins | ILU                               | -100<br>-10          | 100<br>10         | mA   |

| Operating Junction Temperature Range                                        | TJ                                | -10                  | 125               | °C   |

| Operating Ambient Temperature Range                                         | T <sub>A</sub>                    | -10                  | 100               | °C   |

| Storage Temperature Range                                                   | T <sub>STG</sub>                  | -40                  | 150               | °C   |

| Thermal Resistance Junction to Board (Note 2)                               | R <sub>θJB</sub>                  | 8.2                  |                   | °C/W |

| Thermal Resistance Junction to Ambient (Note 2)                             | R <sub>θJA</sub>                  | 21.8                 |                   | °C/W |

| Power Dissipation at $T_A = 25^{\circ}C$ (Note 3)                           | PD                                | 4.59                 |                   | W    |

| Moisture Sensitivity Level (Note 4)                                         | MSL                               | (                    | -                 |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Latch up Current per JEDEC standard: JESD78 class II.

2. The thermal resistance values are dependent of the internal losses split between devices and the PCB heat dissipation. This data is based on a typical operation condition with a 4-layer FR-4 PCB board, which has two, 1-ounce copper internal power and ground planes and 2-ounce copper traces on top and bottom layers with approximately 80% copper coverage. No airflow and no heat sink applied (reference EIA/JEDEC 51.7). It also does not account for other heat sources that may be present on the PCB next to the device in question (such as inductors, resistors etc.)

The maximum power dissipation (PD) is dependent on input voltage, output voltage, output current, external components selected, and PCB layout. The reference data is obtained based on T<sub>JMAX</sub> = 125°C and R<sub>0JA</sub> = 21.8°C/W.

4. Moisture Sensitivity Level (MSL): 3 per IPC/JEDEC standard: J-STD-020D.1.

| ELECTRICAL CHARACTERISTICS (VIN = 12 V, V <sub>CC</sub> = V <sub>CCP</sub> = 5 V, V <sub>OUT</sub> = 1.0 V, typical values are referenced to T <sub>J</sub> = 25°C, Min |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| and Max values are referenced to $T_J$ from $-10^{\circ}$ C to 100°C. unless otherwise noted.)                                                                          |  |

| Characteristics                                             | Test Conditions                                                                             | Symbol             | Min         | Тур                                                   | Max               | Unit           |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|-------------|-------------------------------------------------------|-------------------|----------------|

| SUPPLY VOLTAGE                                              |                                                                                             |                    |             |                                                       | -                 |                |

| Supply Voltage V <sub>IN</sub> Range                        | (Note 5)                                                                                    | V <sub>IN</sub>    |             | 12                                                    |                   | V              |

| Supply Voltage V <sub>CC</sub> Range                        | (Note 5)                                                                                    | V <sub>CC</sub>    | 4.75        | 5                                                     | 5.25              | V              |

| Supply Voltage V <sub>CCP</sub> Range                       | (Note 5)                                                                                    | V <sub>CCP</sub>   | 4.75        | 5                                                     | 5.25              | V              |

| SUPPLY VOLTAGE MONITOR                                      |                                                                                             |                    | -           |                                                       | -                 |                |

| V <sub>IN</sub> UVLO                                        | Falling Threshold                                                                           | V <sub>INUV-</sub> | 3.0         | 3.25                                                  | 3.5               | V              |

|                                                             | Hysteresis                                                                                  | V <sub>INHYS</sub> |             | 650                                                   | -                 | mV             |

| V <sub>CC</sub> UVLO                                        | Falling Threshold                                                                           | V <sub>CCUV-</sub> | 3.8         | 4.08                                                  | -                 | V              |

|                                                             | Rising Threshold                                                                            | V <sub>CCUV+</sub> | -           | 4.34                                                  | 4.5               | V              |

|                                                             | Hysteresis                                                                                  | V <sub>CCHYS</sub> | -           | 260                                                   | -                 | mV             |

| SUPPLY CURRENT                                              | •                                                                                           |                    |             |                                                       |                   |                |

| V <sub>IN</sub> Quiescent Supply Current<br>(Power MOSFETs) | EN high, no load, PS0,1,2 Modes<br>EN high, no load, PS3 Mode<br>EN high, PS4 Mode (Note 6) | Ι <sub>Q</sub>     | -<br>-<br>- | 1.5<br>1.5<br>-                                       | 3<br>3<br>1       | mA<br>mA<br>μA |

| V <sub>IN</sub> Shutdown Current                            | EN low (Note 6)                                                                             | I <sub>SD</sub>    | -           | -                                                     | 1                 | μΑ             |

| V <sub>CC</sub> Quiescent Supply Current (Controller)       | EN high, no load, PS0,1,2 Modes<br>EN high, no load, PS3 Mode<br>EN high, PS4 Mode (Note 6) | IQCC               | -<br>-<br>- | 8.0<br>7.5<br>170                                     | 12<br>12<br>194   | mA<br>mA<br>μA |

| V <sub>CC</sub> Shutdown Current                            | EN low (Note 6)                                                                             | I <sub>SDCC</sub>  | -           | -                                                     | 90                | μΑ             |

| V <sub>CCP</sub> Quiescent Supply Current<br>(Gate Driver)  | EN high, no load, PS0,1,2 Modes<br>EN high, no load, PS3 Mode<br>EN high, PS4 Mode          | IQCCP              | -<br>-<br>- | 0.7<br>0.7<br>-                                       | 1.25<br>1.25<br>2 | mA<br>mA<br>μA |

| V <sub>CCP</sub> Shutdown Current                           | EN low                                                                                      | I <sub>SDCCP</sub> | -           | -                                                     | 2                 | μΑ             |

| OUTPUT VOLTAGE                                              |                                                                                             |                    |             |                                                       |                   |                |

| Output Voltage Range                                        | (Note 5)                                                                                    | V <sub>OUT</sub>   | 0           | -                                                     | 2.3               | V              |

| REGULATION ACCURACY                                         |                                                                                             |                    |             |                                                       |                   |                |

| System Voltage Accuracy                                     | 0.5 V < DAC < 1.52 V<br>0.25 V < DAC < 0.495 V                                              |                    | -8<br>-10   |                                                       | 8<br>10           | mV<br>mV       |

| DVID                                                        |                                                                                             |                    |             |                                                       |                   |                |

| Fast Slew Rate                                              | Default                                                                                     | FSR                |             | 14                                                    |                   | mV/μs          |

| Soft Start Slew Rate                                        |                                                                                             | SSSR               |             | FSR/4                                                 |                   | mV/μs          |

| Slow Slew Rate                                              |                                                                                             | SSR                |             | FSR/2<br><u>FSR/4</u><br>(default)<br>FSR/8<br>FSR/16 |                   | mV/μs          |

| DIFFERENTIAL VOLTAGE-SENSE                                  | AMPLIFIER                                                                                   | -                  | -           | •                                                     | •                 |                |

| DC Gain                                                     | VSP-VSN = 0.5 V to 2.3 V                                                                    | GAIN_DVA           |             | 1.0                                                   |                   | V/V            |

| –3 dB Gain Bandwidth                                        | CL = 20 pF to GND, RL = 10 k $\Omega$ to GND (Note 5)                                       | BW_DVA             |             | 10                                                    |                   | MHz            |

| VSP Input Voltage Range                                     | (Note 5)                                                                                    | VSP                | -0.3        | -                                                     | 3.0               | V              |

| VSN Input Voltage Range                                     | (Note 5)                                                                                    | VSN                | -0.3        | -                                                     | 0.3               | V              |

|                                                             |                                                                                             | +                  | 1           | 1                                                     |                   | 1              |

5. Guaranteed by design, not tested in production. 6.  $T_J = 25^{\circ}C$ .

Input Bias Current

VSP,CSREF = 1.3 V

-15 -100

I<sub>VSP</sub> I<sub>VSN</sub> 15 100

μA nA

| ELECTRICAL CHARACTERISTICS (V <sub>IN</sub> = 12 V, V <sub>CC</sub> = V <sub>CCP</sub> = 5 V, V <sub>OUT</sub> = 1.0 V, typical values are referenced to T <sub>J</sub> = 25°C, Min |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| and Max values are referenced to $T_J$ from $-10^{\circ}$ C to $100^{\circ}$ C. unless otherwise noted.)                                                                            |  |

| Characteristics                                                         | Test Conditions                                                                       | Symbol                                   | Min         | Тур  | Max       | Unit     |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------|-------------|------|-----------|----------|

| DIFFERENTIAL CURRENT-SENSE A                                            | MPLIFIER                                                                              |                                          |             |      |           |          |

| DC Gain                                                                 | (Note 5)                                                                              | GAIN_DCA                                 |             | 80   |           | dB       |

| –3dB Gain Bandwidth                                                     | CL = 20 pF to GND, RL = 10 k $\Omega$ to GND (Note 5)                                 | BW_DCA                                   |             | 10   |           | MHz      |

| Input Offset Voltage                                                    |                                                                                       | V <sub>OS_CS</sub>                       | -300        | -    | 300       | μV       |

| Input Bias Current                                                      | CSSUM = CSREF = 1.2 V                                                                 | I <sub>CSSUM</sub><br>I <sub>CSREF</sub> | -7.5<br>-10 |      | 7.5<br>10 | nA<br>μA |

| ERROR AMPLIFIER                                                         | •                                                                                     | •                                        | •           |      |           |          |

| DC Gain                                                                 | CL = 20 pF to GND, RL = 10 k $\Omega$ to GND (Note 5)                                 | GAIN_EA                                  |             | 80   |           | dB       |

| Unity Gain Bandwidth                                                    | CL = 20 pF to GND, RL = 10 k $\Omega$ to GND (Note 5)                                 | BW_EA                                    |             | 20   |           | MHz      |

| Slew Rate                                                               |                                                                                       | SR_EA                                    |             | 25   |           | V/µs     |

| Output Voltage Swing                                                    | Isource_EA = 2 mA                                                                     | Vmax_EA                                  | 3.5         | -    | -         | V        |

|                                                                         | Isink_EA = 2 mA                                                                       | Vmin_EA                                  | -           | -    | 1         |          |

| FB Voltage                                                              |                                                                                       | V <sub>FB</sub>                          |             | 1.3  |           | V        |

| Input Bias Current                                                      | VFB = 1.3 V                                                                           | I <sub>FB</sub>                          | -1.5        |      | 1.5       | μA       |

| SWITCHING FREQUENCY                                                     |                                                                                       |                                          |             |      |           |          |

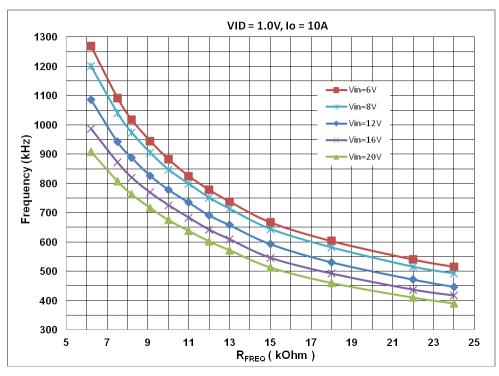

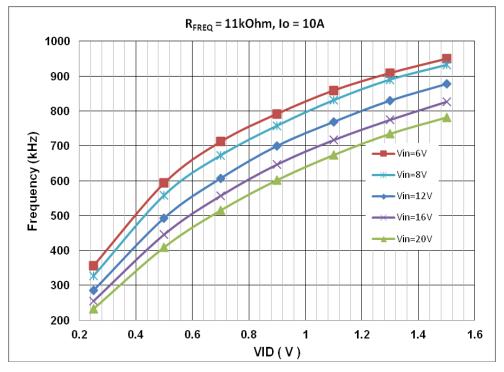

| Normal Operation Frequency<br>(Programmed by a resistor at FREQ<br>pin) | (Note 5)                                                                              | FSW                                      | 500         |      | 1200      | kHz      |

| FREQ Output Voltage                                                     |                                                                                       | VFREQ                                    | 1.95        | 2.0  | 2.05      | V        |

| CONTROL LOGIC                                                           | ·                                                                                     | •                                        |             |      |           |          |

| ENABLE Input High Voltage                                               |                                                                                       | VEN_H                                    | 0.8         | -    | -         | V        |

| ENABLE Input Low Voltage                                                |                                                                                       | VEN_L                                    | -           | -    | 0.3       | V        |

| ENABLE Input Hysteresis                                                 |                                                                                       | VEN_HYS                                  | -           | 300  | -         | mV       |

| ENABLE Input Bias Current                                               |                                                                                       | IEN_BIAS                                 | -           |      | 1.0       | μΑ       |

| SCLK, SDIO                                                              |                                                                                       |                                          |             |      |           |          |

| Input High Voltage                                                      |                                                                                       | V <sub>IH</sub>                          | 0.65        |      |           | V        |

| Input Low Voltage                                                       |                                                                                       | V <sub>IL</sub>                          |             |      | 0.45      | V        |

| Input Threshold Hysteresis                                              |                                                                                       | V <sub>HYS</sub>                         |             | 50   |           | mV       |

| Output High Voltage                                                     | (Note 5)                                                                              | V <sub>OH</sub>                          |             | 1.05 |           | V        |

| Output Low Voltage                                                      | SDIO                                                                                  | V <sub>OL</sub>                          |             |      | 0.3       | V        |

| Buffer On Resistance (data line, ALERT#, and VR_HOT#)                   |                                                                                       | R <sub>ON</sub>                          | 3.0         |      | 13        | Ω        |

| Input Leakage Current                                                   | Pin voltage between 0 and 1.05 V                                                      |                                          | -100        |      | 100       | μΑ       |

| Input Capacitance                                                       | Die capacitance only (Note 5)                                                         |                                          |             |      | 4.0       | pF       |

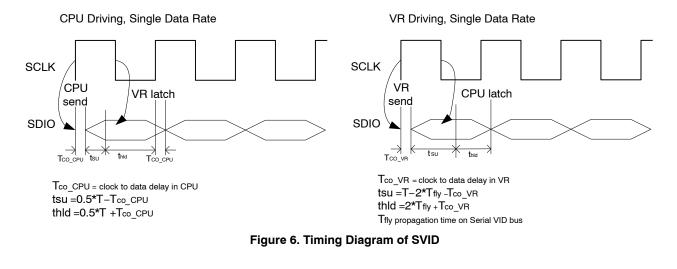

| VR Clock to Data Delay                                                  | Time between SCLK rising edge and valid SDIO level (Note 5)                           | Тсо                                      | 4           |      | 8.3       | ns       |

| Setup Time                                                              | Time before SCLK falling (sampling)<br>edge that SDIO level must be valid<br>(Note 5) | Tsu                                      | 7           |      |           | ns       |

5. Guaranteed by design, not tested in production. 6.  $T_J = 25^{\circ}C$ .

| ELECTRICAL CHARACTERISTICS (VIN = 12 V, VCC = VCCP = 5 V, VOUT = 1.0 V, typical values are referenced to TJ = 25°C, Min |

|-------------------------------------------------------------------------------------------------------------------------|

| and Max values are referenced to $T_J$ from $-10^{\circ}$ C to $100^{\circ}$ C. unless otherwise noted.)                |

| Characteristics                                      | Test Conditions                                                                   | Symbol | Min  | Тур     | Мах | Unit |

|------------------------------------------------------|-----------------------------------------------------------------------------------|--------|------|---------|-----|------|

| SCLK, SDIO                                           | I                                                                                 |        | -    | -       | -   |      |

| Hold Time                                            | Time after SCLK falling edge that the SDIO level remains valid (Note 5)           | Thld   | 14   |         |     | ns   |

| ALERT#                                               |                                                                                   |        |      |         |     | -    |

| Output Low Voltage                                   | I_ ALERT # = -4 mA                                                                |        | -    | -       | 0.3 | V    |

| Output Leakage Current                               | High Impedance State, ALERT # = 3.3 V                                             |        | -1.0 | -       | 1.0 | μΑ   |

| VR_HOT#                                              | · · ·                                                                             |        |      |         |     |      |

| Output Low Voltage                                   | I_VRHOT# = -4 mA                                                                  |        | -    | -       | 0.3 | V    |

| Output Leakage Current                               | High Impedance State, VRHOT# = 3.3 V                                              |        | -1.0 | -       | 1.0 | μA   |

| TSENSE                                               |                                                                                   |        |      |         |     |      |

| Alert# Assert Threshold                              |                                                                                   |        |      | 491     |     | mV   |

| Alert# De-assert Threshold                           |                                                                                   |        |      | 513     |     | mV   |

| VR_HOT# Assert Threshold                             |                                                                                   |        |      | 472     | 1   | mV   |

| VR_HOT# De-assert Threshold                          |                                                                                   |        |      | 494     | 1   | mV   |

| TSENSE Bias Current                                  | V <sub>TSENSE</sub> = 0.4 V                                                       |        | 115  | 120     | 125 | μA   |

| VBOOT                                                |                                                                                   |        |      |         |     | -    |

| Sensing Current                                      | V <sub>VBOOT</sub> = GND                                                          |        |      | 10      |     | μA   |

| IMAX                                                 |                                                                                   |        | •    |         |     |      |

| Sensing Current                                      | V <sub>IMAX</sub> = GND                                                           |        |      | 10      |     | μA   |

| ADC                                                  | · · ·                                                                             |        |      |         |     |      |

| Voltage Range                                        |                                                                                   |        | 0    |         | 2.0 | V    |

| Total Unadjusted Error (TUE)                         |                                                                                   |        | -1   |         | 1   | %    |

| Differential Nonlinearity (DNL)                      | 8-bit                                                                             |        |      |         | 1   | LSB  |

| Power Supply Sensitivity                             |                                                                                   |        |      | ±1      |     | %    |

| Conversion Time                                      |                                                                                   |        |      | 30      |     | μs   |

| Round Robin                                          |                                                                                   |        |      | 90      |     | μs   |

| VR_READY (VRRDY Output)                              |                                                                                   |        |      | <b></b> | 1   |      |

| Rise Time                                            | External 1 k $\Omega$ pull–up to 3.3 V,<br>CTOT = 45 pF, $\Delta$ Vo = 10% to 90% |        |      | 100     |     | ns   |

| Fall Time                                            | External 1 k $\Omega$ pull–up to 3.3 V,<br>CTOT = 45 pF, $\Delta$ Vo = 90% to 10% |        |      | 10      |     | ns   |

| Output Voltage at Power–Up                           | Pulled up to 5 V via 2 k $\Omega$                                                 |        | -    | -       | 1.0 | V    |

| VR_READY Delay (Rising)                              | DAC = Target to VR_READY                                                          |        |      | 50      |     | μs   |

| VR_READY Delay (Falling)                             | From OCP or OVP                                                                   |        |      | 5       |     | μs   |

| VRRDY Pin Low Voltage                                | Voltage at VRRDY pin with 4 mA sink current                                       | VPG_L  | -    | -       | 0.3 | V    |

| VRRDY Pin Leakage Current                            | VRRDY = 5 V                                                                       | PG_LK  | -1.0 | -       | 1.0 | μA   |

| OVER VOLTAGE PROTECTION                              | · · ·                                                                             |        | •    |         |     |      |

| Absolute Over Voltage Threshold<br>During Soft-Start |                                                                                   |        | 2.8  | 2.9     | 3.0 | V    |

|                                                      |                                                                                   |        |      |         |     |      |

5. Guaranteed by design, not tested in production. 6.  $T_J = 25^{\circ}C$ .

| ELECTRICAL CHARACTERISTICS (V <sub>IN</sub> = 12 V, V <sub>CC</sub> = V <sub>CCP</sub> = 5 V, V <sub>OUT</sub> = 1.0 V, typical values are referenced to T <sub>J</sub> = 25°C, Min |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and Max values are referenced to $T_J$ from $-10^{\circ}$ C to $100^{\circ}$ C. unless otherwise noted.)                                                                            |

| Characteristics                                            | Test Conditions                                                                                                   | Symbol                  | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------|------|------|------|------|

| OVER VOLTAGE PROTECTION                                    | -                                                                                                                 |                         |      |      |      |      |

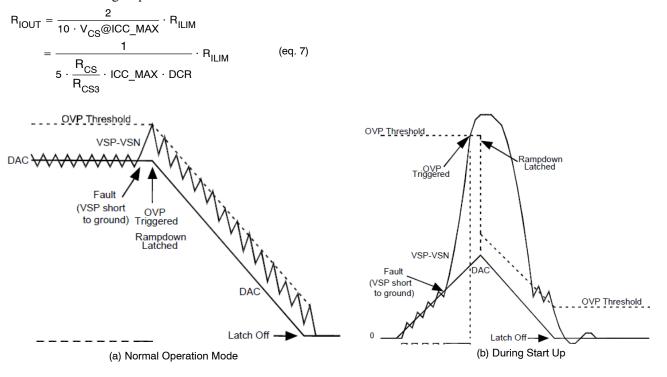

| Over Voltage Threshold Above DAC                           | VSP rising                                                                                                        |                         | 350  | 400  | 425  | mV   |

| Over Voltage Delay                                         | VSP rising to GH low                                                                                              |                         |      | 50   |      | ns   |

| UNDER VOLTAGE PROTECTION                                   |                                                                                                                   |                         |      |      |      |      |

| Under Voltage Threshold Below DAC                          | VSP falling                                                                                                       |                         | 250  | 300  | 350  | mV   |

| Under-voltage Delay                                        |                                                                                                                   |                         |      | 5    |      | μs   |

| OVER CURRENT PROTECTION                                    |                                                                                                                   |                         |      |      |      |      |

| ILIM Threshold Current<br>(OCP shutdown after 50 μs delay) |                                                                                                                   | ILIMTH_SLOW             | 9.0  | 10.0 | 11.0 | μA   |

| ILIM Threshold Current<br>(immediate OCP shutdown)         |                                                                                                                   | I <sub>LIMTH_FAST</sub> | 13.5 | 15.0 | 16.5 | μA   |

| ΙΟυΤ ΟυΤΡυΤ                                                |                                                                                                                   |                         |      |      |      |      |

| Current Gain                                               | (IOUTCURRENT) / (ILIMCURRENT);<br>RILIM = 20 k $\Omega$ ; RIOUT = 5.0 k $\Omega$ ;<br>DAC = 0.8 V, 1.25 V, 1.52 V |                         | 9.5  | 10   | 10.5 | A/A  |

| Input Referred Offset Voltage                              | ILIM – CSREF                                                                                                      |                         | -2.0 | -    | 2.0  | mV   |

| Output Source Current                                      | ILIM sink current = 80 μA                                                                                         |                         |      | 800  |      | μA   |

| HIGH-SIDE MOSFET                                           |                                                                                                                   |                         |      |      |      |      |

| Drain-to-Source ON Resistance                              | VGS = 4.5 V, ID = 10 A                                                                                            | R <sub>ON_H</sub>       | -    | 8.0  | -    | mΩ   |

| LOW-SIDE MOSFET                                            |                                                                                                                   |                         |      |      |      |      |

| Drain-to-Source ON Resistance                              | VGS = 4.5 V, ID = 10 A                                                                                            | R <sub>ON_L</sub>       | -    | 4.0  | -    | mΩ   |

| HIGH-SIDE GATE DRIVE                                       |                                                                                                                   |                         |      |      |      |      |

| Pull-High Drive ON Resistance                              | $V_{BST} - V_{SW} = 5 V$                                                                                          | R <sub>DRV_HH</sub>     | -    | 1.2  | 2.8  | Ω    |

| Pull-Low Drive ON Resistance                               | $V_{BST} - V_{SW} = 5 V$                                                                                          | R <sub>DRV_HL</sub>     | -    | 0.8  | 2.0  | Ω    |

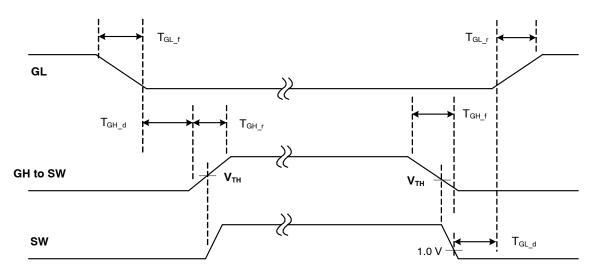

| GH Propagation Delay Time                                  | From GL falling to GH rising                                                                                      | $T_{GH_{d}}$            |      | 15   |      | ns   |

| LOW-SIDE GATE DRIVE                                        |                                                                                                                   |                         |      |      |      |      |

| Pull-High Drive ON Resistance                              | $V_{CCP} - V_{PGND} = 5 V$                                                                                        | R <sub>DRV_LH</sub>     | -    | 0.9  | 2.8  | Ω    |

| Pull-Low Drive ON Resistance                               | V <sub>CCP</sub> – V <sub>PGND</sub> = 5 V                                                                        | R <sub>DRV_LL</sub>     | -    | 0.4  | 1.25 | Ω    |

| GL Propagation Delay Time                                  | From GH falling to GL rising                                                                                      | T <sub>GL_d</sub>       |      | 10   |      | ns   |

| SW to PGND RESISTANCE                                      |                                                                                                                   |                         |      |      |      |      |

| SW to PGND Pull-Down Resistance                            | (Note 5)                                                                                                          | R <sub>SW</sub>         | -    | 1.88 | -    | kΩ   |

| BOOTSTRAP RECTIFIER SWITCH                                 |                                                                                                                   |                         |      |      |      |      |

| On Resistance                                              | EN = L  or  EN = H  and  DRVL = H                                                                                 | R <sub>on_BST</sub>     | 5    | 13   | 20   | Ω    |

5. Guaranteed by design, not tested in production. 6.  $T_J = 25^{\circ}C$ .

NOTE: Timing is referenced to the 90% and 10% points, unless otherwise noted.

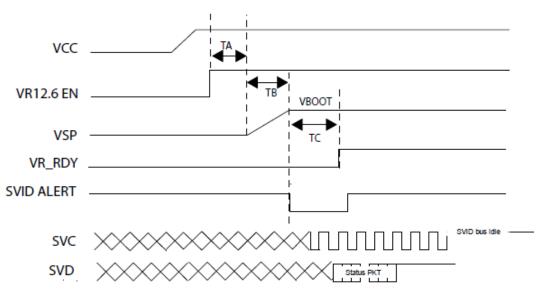

Figure 5. Timing Diagram of Start Up

### Table 1. START-UP AND ENABLE TIMINGS

|        |                                                                                                      |                      | Values |        |                                                                                                                                                 |

|--------|------------------------------------------------------------------------------------------------------|----------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | Description                                                                                          | Min                  | Тур    | Max    | Note                                                                                                                                            |

| ТА     | Non-zero Vboot Case: start of Vboot ramp<br>Zero Vboot Case: Controller ready accept<br>SVID command |                      |        | 2.5 ms | Complete all internal analog and digital<br>configurations and reset protocols dur-<br>ing TA. May be disclosed to CPU<br>through register 2Dh. |

| ТВ     | Vboot ramp time                                                                                      | Depends on Slew rate |        | w rate | When Vboot > 0 V, the VR is to slew at the default Slow rate of FAST/4                                                                          |

| тс     | Completion of Vboot ramp or initial SetVID<br>ramp to assertion of associated VR_READY               | 0 µs                 |        | 6 μs   |                                                                                                                                                 |

#### Table 2. STATE TRUTH TABLE

| STATE                                                              | VR_RDY Pin                                          | Error AMP Comp Pin | OVP & UVP         | Method of Reset |

|--------------------------------------------------------------------|-----------------------------------------------------|--------------------|-------------------|-----------------|

| <b>POR</b><br>0 < VCC < UVLO                                       | N/A                                                 | N/A                | N/A               |                 |

| <b>Disabled</b><br>EN < threshold<br>UVLO > threshold              | Low                                                 | Low                | Disabled          |                 |

| Start up Delay & Calibration<br>EN > threshold<br>UVLO > threshold | Low                                                 | Low                | Disabled          |                 |

| <b>Soft Start</b><br>EN > threshold<br>UVLO > threshold            | Low                                                 | Operational        | Active / No latch |                 |

| Normal Operation<br>EN > threshold<br>UVLO > threshold             | High                                                | Operational        | Active / Latching | N/A             |

| Over Voltage                                                       | Low                                                 | N/A                | DAC + 400 mV      |                 |

| Over Current                                                       | Low                                                 | Operational        | Last DAC Code     |                 |

| VID Code = 00h                                                     | Low: if Reg34h:bit0 = 0;<br>High:if Reg34h:bit0 = 1 | Clamped at 0.9 V   | Disabled          |                 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX      |

|------|------|------|------|------|------|------|------|-------------|----------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | OFF         | 00       |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.25000     | 01       |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.25500     | 02       |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.26000     | 03       |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.26500     | 04       |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.27000     | 05       |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.27500     | 06       |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.28000     | 07       |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.28500     | 08       |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.29000     | 09       |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.29500     | 0A       |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.30000     | 0B       |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.30500     | 0C       |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.31000     | 0D       |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.31500     | 0E       |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.32000     | 0F       |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.32500     | 10       |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.33000     | 11       |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.33500     | 12       |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.34000     | 13       |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.34500     | 14       |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.35000     | 15       |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.35500     | 16       |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.36000     | 17       |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.36500     | 18       |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.37000     | 19       |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.37500     | 1A       |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.38000     | 1B       |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.38500     | 1C       |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.39000     | 1D       |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.39500     | 1E       |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.40000     | 1F       |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.40500     | 20       |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.41000     | 21       |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.41500     | 22       |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.42000     | 23       |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.42500     | 24       |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.43000     | 25       |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.43500     | 26       |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.44000     | 27       |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.44500     | 28       |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.45000     | 29       |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.45500     | 28<br>2A |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.46000     | 2B       |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.46500     | 2D<br>2C |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.47000     | 20<br>2D |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.47500     | 25<br>2E |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.48000     | 2E<br>2F |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX      |

|------|------|------|------|------|------|------|------|-------------|----------|

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.48500     | 30       |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.49000     | 31       |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.49500     | 32       |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0.50000     | 33       |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0.50500     | 34       |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0.51000     | 35       |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0.51500     | 36       |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0.52000     | 37       |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0.52500     | 38       |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0.53000     | 39       |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0.53500     | ЗA       |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0.54000     | 3B       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0.54500     | 3C       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0.55000     | 3D       |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0.55500     | 3E       |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0.56000     | 3F       |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0.56500     | 40       |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0.57000     | 41       |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0.57500     | 42       |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0.58000     | 43       |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0.58500     | 44       |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0.59000     | 45       |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0.59500     | 46       |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0.60000     | 47       |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0.60500     | 48       |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0.61000     | 49       |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0.61500     | 4A       |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0.62000     | 4B       |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0.62500     | 4D<br>4C |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0.63000     | 40<br>4D |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0.63500     | 4D<br>4E |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0.64000     | 4∟<br>4F |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0.64500     | 50       |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0.65000     | 50       |

|      |      |      |      |      |      |      |      |             |          |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0.65500     | 52       |

|      |      |      | 1    |      |      |      |      | 0.66000     | 53       |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0.66500     | 54       |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0.67000     | 55       |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0.67500     | 56       |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0.68000     | 57       |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0.68500     | 58       |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0.69000     | 59       |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0.69500     | 5A       |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0.70000     | 5B       |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0.70500     | 5C       |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0.71000     | 5D       |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0.71500     | 5E       |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0.72000     | 5F       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX      |

|------|------|------|------|------|------|------|------|-------------|----------|

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0.72500     | 60       |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0.73000     | 61       |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0.73500     | 62       |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.74000     | 63       |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.74500     | 64       |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.75000     | 65       |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.75500     | 66       |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.76000     | 67       |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.76500     | 68       |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.77000     | 69       |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.77500     | 6A       |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.78000     | 6B       |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.78500     | 6C       |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.79000     | 6D       |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.79500     | 6E       |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.80000     | 6F       |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.80500     | 70       |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.81000     | 71       |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.81500     | 72       |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.82000     | 73       |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.82500     | 74       |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.83000     | 75       |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.83500     | 76       |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.84000     | 77       |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.84500     | 78       |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85000     | 79       |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.85500     | 7A       |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.86000     | 7B       |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.86500     | 7C       |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.87000     | 7D       |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.87500     | 7E       |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.88000     | 7F       |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.88500     | 80       |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.89000     | 81       |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.89500     | 82       |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.90000     | 83       |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.90500     | 84       |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.91000     | 85       |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.91500     | 86       |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.92000     | 87       |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.92500     | 88       |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.93000     | 89       |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.93500     | 8A       |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.93500     | 8B       |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.94000     | 80<br>80 |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.94500     | 80<br>8D |

|      | 0    | 0    | 0    |      |      | 1    | 0    | 0.95500     | 8D<br>8E |

| 1    | U    | U    | U    | 1    | 1    | I    | U    | 0.9000      | δĖ       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX      |

|------|------|------|------|------|------|------|------|-------------|----------|

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.96500     | 90       |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.97000     | 91       |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.97500     | 92       |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.98000     | 93       |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.98500     | 94       |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.99000     | 95       |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.99500     | 96       |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1.00000     | 97       |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.00500     | 98       |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.01000     | 99       |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.01500     | 9A       |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.02000     | 9B       |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.02500     | 9C       |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.03000     | 9D       |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.03500     | 9E       |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.04000     | 9F       |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.04500     | A0       |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.05000     | A1       |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.05500     | A2       |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.06000     | A3       |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.06500     | A4       |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.07000     | A5       |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.07500     | A6       |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.08000     | A7       |

|      | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.08500     | A7<br>A8 |

| 1    | 0    | 1    | 0    |      | 0    | 0    |      |             |          |

| 1    |      |      |      | 1    |      |      | 1    | 1.09000     | A9       |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.09500     | AA       |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.10000     | AB       |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.10500     | AC       |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.11000     | AD       |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.11500     | AE       |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.12000     | AF       |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.12500     | B0       |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.13000     | B1       |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.13500     | B2       |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.14000     | B3       |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.14500     | B4       |

| 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.15000     | B5       |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.15500     | B6       |

| 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.16000     | B7       |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.16500     | B8       |

| 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.17000     | B9       |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.17500     | BA       |

| 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.18000     | BB       |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.18500     | BC       |

| 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.19000     | BD       |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1.19500     | BE       |

| 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1.20000     | BF       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage (V) | HEX |

|------|------|------|------|------|------|------|------|-------------|-----|

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1.20500     | C0  |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1.21000     | C1  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1.21500     | C2  |

| 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1.22000     | C3  |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1.22500     | C4  |

| 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1.23000     | C5  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1.23500     | C6  |

| 1    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1.24000     | C7  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1.24500     | C8  |

| 1    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1.25000     | C9  |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1.25500     | CA  |

| 1    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1.26000     | СВ  |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1.26500     | СС  |

| 1    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1.27000     | CD  |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1.27500     | CE  |

| 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1.28000     | CF  |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1.28500     | D0  |

| 1    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1.29000     | D1  |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1.29500     | D2  |

| 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1.30000     | D3  |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1.30500     | D4  |

| 1    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1.31000     | D5  |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1.31500     | D6  |

| 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1.32000     | D7  |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1.32500     | D8  |

| 1    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1.33000     | D9  |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1.33500     | DA  |

| 1    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1.34000     | DB  |

| 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1.34500     | DC  |

|      |      | 0    |      | 1    |      | 0    |      | 1.34300     | DD  |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    |             | DE  |

| 1    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1.35500     | DE  |

|      |      |      |      |      |      |      |      | 1.36000     |     |