Is Now Part of

## **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="mailto:www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or unavteries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor and is officers, employees, uniotificated use, even if such claim any manner.

June 2000 Revised April 2005

# FSTD16211 24-Bit Bus Switch with Level Shifting

Ordering Code:

exists between the A and B Ports.

5V inputs and 3.3V outputs.

FAIRCHILD

SEMICONDUCTOR

**General Description**

**FSTD16211**

| Order Number                               | Package Number | Package Description                                                                    |  |  |  |  |

|--------------------------------------------|----------------|----------------------------------------------------------------------------------------|--|--|--|--|

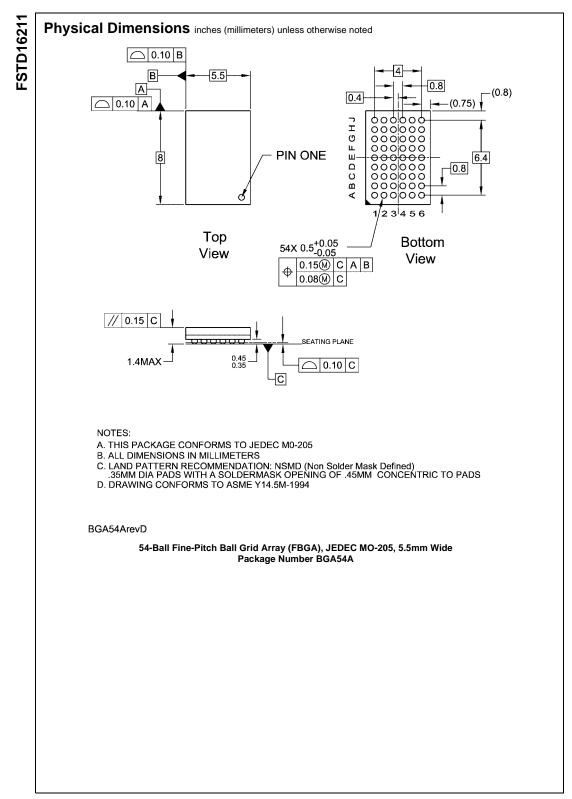

| FSTD16211G<br>(Note 1)(Note 2)             |                | 54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide<br>[TAPE and REEL] |  |  |  |  |

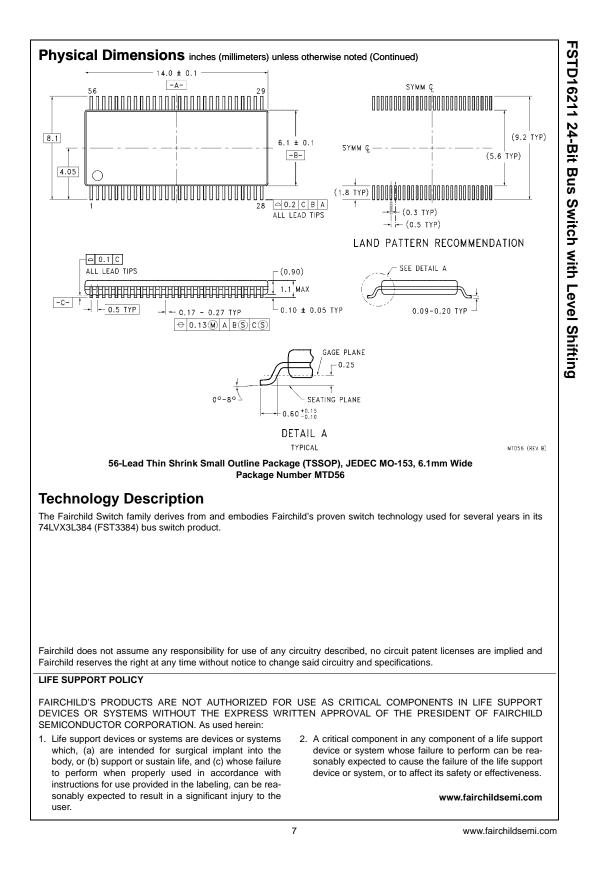

| FSTD16211MTD<br>(Note 2)                   | MTD56          | 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide            |  |  |  |  |

| Note 1: Ordering code "G" indicates Trays. |                |                                                                                        |  |  |  |  |

**Features**

■ Low I<sub>CC</sub>

(FBGA)

■ Voltage level shifting

$\blacksquare$  4 $\Omega$  switch connection between two ports

Control inputs compatible with TTL level

■ Zero bounce in flow-through mode

Minimal propagation delay through the switch

■ Also packaged in plastic Fine-Pitch Ball Grid Array

Note 2: Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

24-Bit Bus Switch with Level Shifting

The Fairchild Switch FSTD16211 provides 24-bits of high-

speed CMOS TTL-compatible bus switching. The low On

Resistance of the switch allows inputs to be connected to

outputs without adding propagation delay or generating

additional ground bounce noise. A diode to  $V_{CC}$  has been

integrated into the circuit to allow for level shifting between

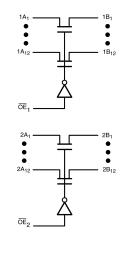

The device is organized as a 12-bit or 24-bit bus switch.

When  $\overline{OE}_1$  is LOW, the switch is ON and Port 1A is con-

nected to Port 1B. When  $\overline{\text{OE}}_2$  is LOW, Port 2A is connected to Port 2B. When  $\overline{\text{OE}}_{1/2}$  is HIGH, a high impedance state

### Logic Diagram

# FSTD16211

### **Connection Diagrams**

| Pin Assignment for TSSOP |    |    |                          |  |  |  |  |  |

|--------------------------|----|----|--------------------------|--|--|--|--|--|

| NC -                     |    | 56 | - OE,                    |  |  |  |  |  |

| 1A1 -                    | 2  | 55 |                          |  |  |  |  |  |

| 1A2 -                    | 3  | 54 | - 1B1                    |  |  |  |  |  |

| 1A3 —                    | 4  | 53 | - 1B <sub>2</sub>        |  |  |  |  |  |

| 1A4 —                    | 5  | 52 | — 1B <sub>3</sub>        |  |  |  |  |  |

| 1A <sub>5</sub> —        | 6  | 51 | — 1B <sub>4</sub>        |  |  |  |  |  |

| 1A <sub>6</sub> —        | 7  | 50 | — 1B <sub>5</sub>        |  |  |  |  |  |

| GND —                    | 8  | 49 | - GND                    |  |  |  |  |  |

| 1A7 —                    | 9  | 48 | — 1B <sub>6</sub>        |  |  |  |  |  |

| 1A <sub>8</sub> —        | 10 | 47 | — 1B <sub>7</sub>        |  |  |  |  |  |

| 1A <sub>9</sub> —        | 11 | 46 | — 1B <sub>8</sub>        |  |  |  |  |  |

| 1A <sub>10</sub> -       | 12 | 45 | — 1B <sub>9</sub>        |  |  |  |  |  |

| 1A <sub>11</sub> —       | 13 | 44 | — 1B <sub>10</sub>       |  |  |  |  |  |

| 1A <sub>12</sub> -       | 14 | 43 | — 1B <sub>11</sub>       |  |  |  |  |  |

| 2A1-                     | 15 | 42 | - 1B <sub>12</sub>       |  |  |  |  |  |

| 2A2-                     | 16 | 41 | — 2B1                    |  |  |  |  |  |

| V <sub>CC</sub>          | 17 | 40 | - 2B <sub>2</sub>        |  |  |  |  |  |

| 2A3-                     | 18 | 39 | — 2B <sub>3</sub>        |  |  |  |  |  |

| GND-                     | 19 | 38 | - GND                    |  |  |  |  |  |

| 2A4-                     | 20 | 37 | — 2B <sub>4</sub>        |  |  |  |  |  |

| 2A5-                     | 21 | 36 | — 2B <sub>5</sub>        |  |  |  |  |  |

| 2A <sub>6</sub> —        | 22 | 35 | — 2B <sub>6</sub>        |  |  |  |  |  |

| 2A7-                     | 23 | 34 | — 2B <sub>7</sub>        |  |  |  |  |  |

| 2A <sub>8</sub> —        | 24 | 33 | — 2B <sub>8</sub>        |  |  |  |  |  |

| 2A <sub>9</sub> —        | 25 | 32 | <b>—</b> 2B <sub>9</sub> |  |  |  |  |  |

| 2A <sub>10</sub> —       | 26 | 31 | - 2B <sub>10</sub>       |  |  |  |  |  |

| 2A <sub>11</sub> —       | 27 | 30 | — 2B <sub>11</sub>       |  |  |  |  |  |

| 2A <sub>12</sub> —       | 28 | 29 | - 2B <sub>12</sub>       |  |  |  |  |  |

### Pin Assignment for FBGA

|   | 1  | 2 | 3 | 4 | 5 | 6 |

|---|----|---|---|---|---|---|

| A | 0  | 0 | 0 | 0 | 0 | 0 |

| В | Ιõ | õ | õ | õ | õ | õ |

| υ | Õ  | Õ | Õ | Õ | Õ | Õ |

| D | Ó  | Ó | Ò | 0 | 0 | Ó |

| ш | Ó  | Ó | Ò | 0 | 0 | Ó |

| ч | 0  | 0 | 0 | 0 | 0 | 0 |

| G | 0  | 0 | 0 | 0 | 0 | 0 |

| н | 0  | 0 | 0 | 0 | 0 | 0 |

| ſ | 0  | 0 | 0 | 0 | 0 | 0 |

|   |    |   |   |   |   |   |

(Top Thru View)

### **Pin Descriptions**

| Pin Name                           | Description        |

|------------------------------------|--------------------|

| $\overline{OE}_1, \overline{OE}_2$ | Bus Switch Enables |

| 1A, 2A                             | Bus A              |

| 1B, 2B                             | Bus B              |

| NC                                 | No Connect         |

### **Pin Assignment for FBGA**

|   | 1                | 2                | 3                | 4                | 5                | 6                |

|---|------------------|------------------|------------------|------------------|------------------|------------------|

| Α | 1A <sub>2</sub>  | 1A <sub>1</sub>  | NC               | OE <sub>2</sub>  | 1B <sub>1</sub>  | 1B <sub>2</sub>  |

| В | 1A <sub>4</sub>  | 1A <sub>3</sub>  | 1A <sub>7</sub>  | OE <sub>1</sub>  | 1B <sub>3</sub>  | 1B <sub>4</sub>  |

| С | 1A <sub>6</sub>  | 1A <sub>5</sub>  | GND              | 1B <sub>7</sub>  | 1B <sub>5</sub>  | 1B <sub>6</sub>  |

| D | 1A <sub>10</sub> | 1A <sub>9</sub>  | 1A <sub>8</sub>  | 1B <sub>8</sub>  | 1B <sub>9</sub>  | 1B <sub>10</sub> |

| E | 1A <sub>12</sub> | 1A <sub>11</sub> | 2A <sub>1</sub>  | 2B <sub>1</sub>  | 1B <sub>11</sub> | 1B <sub>12</sub> |

| F | 2A <sub>4</sub>  | 2A <sub>3</sub>  | 2A <sub>2</sub>  | 2B <sub>2</sub>  | 2B <sub>3</sub>  | 2B <sub>4</sub>  |

| G | 2A <sub>6</sub>  | 2A <sub>5</sub>  | V <sub>CC</sub>  | GND              | 2B <sub>5</sub>  | 2B <sub>6</sub>  |

| н | 2A <sub>8</sub>  | 2A <sub>7</sub>  | 2A <sub>9</sub>  | 2B <sub>9</sub>  | 2B <sub>7</sub>  | 2B <sub>8</sub>  |

| J | 2A <sub>12</sub> | 2A <sub>11</sub> | 2A <sub>10</sub> | 2B <sub>10</sub> | 2B <sub>11</sub> | 2B <sub>12</sub> |

### **Truth Table**

| Inp             | uts             | Inputs/Outputs |         |  |

|-----------------|-----------------|----------------|---------|--|

| OE <sub>1</sub> | OE <sub>2</sub> | 1A, 1B         | 2A, 2B  |  |

| L               | L               | 1A = 1B        | 2A = 2B |  |

| L               | н               | 1A = 1B        | Z       |  |

| н               | L               | Z              | 2A = 2B |  |

| н               | Н               | Z              | Z       |  |

### Absolute Maximum Ratings(Note 3)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7.0V   |

|----------------------------------------------------------------------|------------------|

| DC Switch Voltage (V <sub>S</sub> ) (Note 4)                         | -0.5V to +7.0V   |

| DC Input Control Pin Voltage (VIN)(Note 5)                           | -0.5V to +7.0V   |

| DC Input Diode Current (I <sub>IK</sub> ) $V_{IN} < 0V$              | –50 mA           |

| DC Output (I <sub>OUT</sub> )                                        | 128 mA           |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | +/- 100 mA       |

| Storage Temperature Range (T <sub>STG</sub> )                        | –65°C to +150 °C |

|                                                                      |                  |

### Recommended Operating

| Conditions (Note 6)                              |                  |

|--------------------------------------------------|------------------|

| Power Supply Operating $(V_{CC)}$                | 4.5V to 5.5V     |

| Input Voltage (V <sub>IN</sub> )                 | 0V to 5.5V       |

| Output Voltage (V <sub>OUT</sub> )               | 0V to 5.5V       |

| Input Rise and Fall Time $(t_r, t_f)$            |                  |

| Switch Control Input                             | 0 ns/V to 5 ns/V |

| Switch I/O                                       | 0 ns/V to DC     |

| Free Air Operating Temperature (T <sub>A</sub> ) | -40 °C to +85 °C |

Note 3: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 4:  $\mathsf{V}_\mathsf{S}$  is the voltage observed/applied at either A or B Ports across the switch.

Note 5: The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

Note 6: Unused control inputs must be held HIGH or LOW. They may not float.

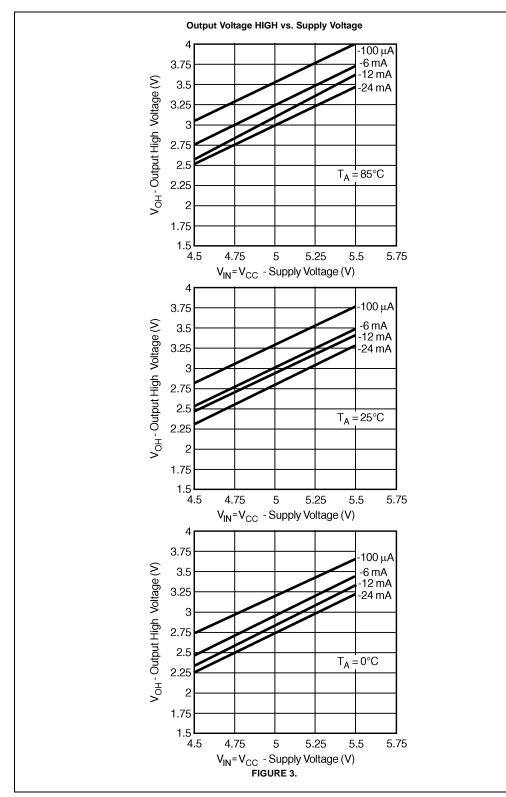

### **DC Electrical Characteristics**

|                  |                                               | V <sub>CC</sub> | T <sub>A</sub> = | -40 °C to +     | 85 °C |       |                                               |

|------------------|-----------------------------------------------|-----------------|------------------|-----------------|-------|-------|-----------------------------------------------|

| Symbol           | Parameter                                     | (V)             | Min              | Typ<br>(Note 7) | Мах   | Units | Conditions                                    |

| V <sub>IK</sub>  | Clamp Diode Voltage                           | 4.5             |                  |                 | -1.2  | V     | $I_{IN} = -18 \text{ mA}$                     |

| V <sub>IH</sub>  | HIGH Level Input Voltage                      | 4.5-5.5         | 2.0              |                 |       | V     |                                               |

| VIL              | LOW Level Input Voltage                       | 4.5-5.5         |                  |                 | 0.8   | V     |                                               |

| V <sub>OH</sub>  | HIGH Level                                    | 4.5-5.5         |                  | See Figure 3    | 3     | V     |                                               |

| II.              | Input Leakage Current                         | 5.5             |                  |                 | ±1.0  | μA    | $0 \le V_{IN} \le 5.5 V$                      |

|                  |                                               | 0               |                  |                 | 10    | μA    | $V_{IN} = 5.5V$                               |

| I <sub>OZ</sub>  | OFF-STATE Leakage Current                     | 5.5             |                  |                 | ±1.0  | μA    | $0 \le A, B \le V_{CC}$                       |

| R <sub>ON</sub>  | Switch On Resistance                          | 4.5             |                  | 4               | 7     | Ω     | V <sub>IN</sub> = 0V, I <sub>IN</sub> = 64 mA |

|                  | (Note 8)                                      | 4.5             |                  | 4               | 7     | Ω     | $V_{IN} = 0V, I_{IN} = 30 \text{ mA}$         |

|                  |                                               | 4.5             |                  | 35              | 50    | Ω     | $V_{IN} = 2.4V, I_{IN} = 15 \text{ mA}$       |

| I <sub>CC</sub>  | Quiescent Supply Current                      | 5.5             |                  |                 | 1.5   | mA    | $OE_1 = OE_2 = GND$                           |

|                  |                                               |                 |                  |                 |       |       | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$       |

|                  |                                               |                 |                  |                 | 10    | μA    | $OE_1 = OE_2 = V_{CC}$                        |

|                  |                                               |                 |                  |                 |       |       | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$       |

| I <sub>CCT</sub> | Increase in I <sub>CC</sub> per Control Input | 5.5             |                  |                 | 2.5   | mA    | One Control Input at 3.4V                     |

|                  |                                               |                 |                  |                 |       |       | Other Control Inputs at $V_{CC}$ or GND       |

Note 7: Typical values are at  $V_{CC}$  = 5.0V and  $T_A{=}\ {+}25^{\circ}C$

Note 8: Measured by the voltage drop between A and B pins at the indicated current through the switch. On Resistance is determined by the lower of the voltages on the two (A or B) pins.

FSTD16211

FSTD16211

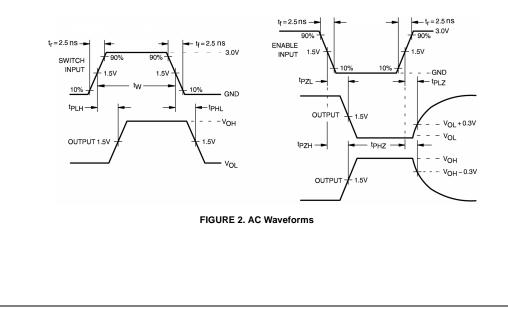

### **AC Electrical Characteristics**

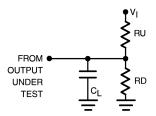

| Symbol                              | Parameter                             | $\label{eq:T_A} \begin{split} & \textbf{T}_{\textbf{A}} = -40 ~^\circ \textbf{C} ~ \textbf{to} ~ +85 ~^\circ \textbf{C}, \\ & \textbf{C}_{\textbf{L}} = 50 \textbf{pF}, ~ \textbf{RU} = \textbf{RD} = 500 \Omega \\ & \textbf{V}_{\textbf{CC}} = 4.5 - 5.5 \textbf{V} \end{split}$ |      | Units | Conditions                                             | Figure<br>Number |  |

|-------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|------------------|--|

|                                     |                                       | Min                                                                                                                                                                                                                                                                                | Max  |       |                                                        |                  |  |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Bus to Bus (Note 9) |                                                                                                                                                                                                                                                                                    | 0.25 | ns    | V <sub>I</sub> = OPEN                                  | Figures<br>1, 2  |  |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Output Enable Time                    | 1.5                                                                                                                                                                                                                                                                                | 5.5  | ns    | $V_I = 7V$ for $t_{PZL}$<br>$V_I = OPEN$ for $t_{PZH}$ | Figures<br>1, 2  |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Output Disable Time                   | 1.5                                                                                                                                                                                                                                                                                | 6.5  | ns    | $V_I = 7V$ for $t_{PLZ}$<br>$V_I = OPEN$ for $t_{PHZ}$ | Figures<br>1, 2  |  |

Note 9: This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On Resistance of the switch and the 50pF load capacitance, when driven by an ideal voltage source (zero output impedance).

### Capacitance (Note 10)

| Symbol           | Parameter                     | Тур | Max | Units | Conditions                     |

|------------------|-------------------------------|-----|-----|-------|--------------------------------|

| C <sub>IN</sub>  | Control Pin Input Capacitance | 3.5 |     | pF    | $V_{CC} = 5.0V$                |

| C <sub>I/O</sub> | Input/Output Capacitance      | 5.5 |     | pF    | $V_{CC}, \overline{OE} = 5.0V$ |

Note 10:  $T_A = +25 \,^{\circ}C$ , f = 1 MHz, Capacitance is characterized but not tested.

### AC Loading and Waveforms

Note: Input driven by  $50\Omega$  source terminated in  $50\Omega$ Note: CL includes load and stray capacitance Note: Input PRR = 1.0 MHz,  $t_W = 500$  ns

### FIGURE 1. AC Test Circuit

www.fairchildsemi.com

4

FSTD16211

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC