# IA186ES/IA188ES 8-Bit/16-Bit Microcontrollers Data Sheet

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 1 of 154

http://www.innovasic.com Customer Support: 1-888-824-4184 Copyright © 2015 by Innovasic Semiconductor, Inc.

Published by Innovasic Semiconductor, Inc. 3737 Princeton Drive NE, Suite 130, Albuquerque, NM 87107

AMD, Am186, and Am188 are trademarks of Advanced Micro Devices, Inc. MILES<sup>™</sup> is a trademark of Innovasic Semiconductor, Inc.

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 2 of 154

# TABLE OF CONTENTS

| List | of Fig | ures         |                                                                                                                             | 9  |

|------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| List | of Tab | oles         |                                                                                                                             | 10 |

| Conv | ventio | ns           |                                                                                                                             | 13 |

| Acro | nyms   | and Ab       | breviations                                                                                                                 | 14 |

| 1.   | Intro  | duction.     |                                                                                                                             | 15 |

|      | 1.1    | Genera       | ll Description                                                                                                              | 15 |

|      | 1.2    | Feature      | es                                                                                                                          | 15 |

| 2.   | Pack   | aging, P     | Pin Descriptions, and Physical Dimensions                                                                                   | 16 |

|      | 2.1    | Packag       | ges and Pinouts                                                                                                             | 16 |

|      |        | 2.1.1        | IA186ES TQFP Package                                                                                                        | 17 |

|      |        | 2.1.2        | IA188ES TQFP Package                                                                                                        |    |

|      |        | 2.1.3        | TQFP Physical Dimensions                                                                                                    |    |

|      |        | 2.1.4        | IA186ES PQFP Package                                                                                                        |    |

|      |        | 2.1.5        | IA188ES PQFP Package                                                                                                        |    |

|      |        | 2.1.6        | PQFP Physical Dimensions                                                                                                    | 30 |

|      | 2.2    |              | scriptions                                                                                                                  | 31 |

|      |        | 2.2.1        | a19/pio9, a18/pio8, a17/pio7, a16-a0-Address Bus (synchronous                                                               |    |

|      |        |              | outputs with tristate)                                                                                                      | 31 |

|      |        | 2.2.2        | ad15-ad8 (IA186ES)-Address/Data Bus (level-sensitive                                                                        |    |

|      |        |              | synchronous inouts with tristate)                                                                                           | 31 |

|      |        | 2.2.3        | ao15–ao8 (IA188ES)—Address Bus (level-sensitive synchronous                                                                 |    |

|      |        |              | outputs with tristate)                                                                                                      | 31 |

|      |        | 2.2.4        | ad7-ad0-Address/Data Bus (level-sensitive synchronous inouts with                                                           |    |

|      |        |              | tristate)                                                                                                                   |    |

|      |        | 2.2.5        | ale—Address Latch Enable (synchronous output)                                                                               |    |

|      |        | 2.2.6        | ardy—Asynchronous Ready (level-sensitive asynchronous input)                                                                | 32 |

|      |        | 2.2.7        | bhe_n/aden_n (IA186ES only)—Bus High Enable (synchronous                                                                    | 22 |

|      |        | <b>a a</b> a | output with tristate)/Address Enable (input with internal pullup)                                                           |    |

|      |        | 2.2.8        | clkouta—Clock Output A (synchronous output)                                                                                 |    |

|      |        | 2.2.9        | clkoutb—Clock Output B (synchronous output)                                                                                 | 33 |

|      |        | 2.2.10       | cts0_n/enrx0_n/pio21—Clear-to-Send 0/Enable-Receive-Request 0                                                               | 22 |

|      |        | 0 0 1 1      | (both are asynchronous inputs)                                                                                              |    |

|      |        | 2.2.11       | den_n/ds_n/pio5—Data Enable /Data Strobe (both are synchronous                                                              |    |

|      |        | 2 2 1 2      | outputs with tristate)<br>drq0/int5/pio12—DMA Request 0 (synchronous level-sensitive                                        |    |

|      |        | 2.2.12       |                                                                                                                             |    |

|      |        |              | input)/Maskable Interrupt Request 5 (asynchronous edge-triggered                                                            | 34 |

|      |        | 2212         | input)dra1/int6/nia13 DMA Paquest 1 (synchronous lavel sensitive)                                                           | 34 |

|      |        | 2.2.13       | drq1/int6/pio13—DMA Request 1 (synchronous level-sensitive input)/Maskable Interrupt Request 6 (asynchronous edge-triggered |    |

|      |        |              | input)/Maskable Interrupt Request 6 (asynchronous edge-triggered input)                                                     | 21 |

|      |        |              | ութաւ)                                                                                                                      |    |

| 2.2.14 | dt/r_n/pio4—Data Transmit or Receive (synchronous output with         |    |

|--------|-----------------------------------------------------------------------|----|

|        | tristate)                                                             | 34 |

| 2.2.15 | gnd—Ground                                                            | 35 |

| 2.2.16 | hlda—Bus Hold Acknowledge (synchronous output)                        | 35 |

| 2.2.17 | int0—Maskable Interrupt Request 0 (asynchronous input)                |    |

| 2.2.18 | int1/select_n—Maskable Interrupt Request 1/Slave Select (both are     |    |

|        | asynchronous inputs)                                                  | 35 |

| 2.2.19 | int2/inta0_n/pwd/pio31—Maskable Interrupt Request 2                   |    |

|        | (asynchronous input)/Interrupt Acknowledge 0 (synchronous             |    |

|        | output)/Pulse Width Demodulator (Schmitt trigger input)               | 36 |

| 2.2.20 | int3/inta1_n/irq—Maskable Interrupt Request 3 (asynchronous           |    |

|        | input)/Interrupt Acknowledge 1 (synchronous output)/Interrupt         |    |

|        | Acknowledge (synchronous output)                                      | 36 |

| 2.2.21 | int4/pio30—Maskable Interrupt Request 4 (asynchronous input)          | 37 |

| 2.2.22 | <pre>lcs_n/once0_n—Lower Memory Chip Select (synchronous output</pre> |    |

|        | with internal pullup)/ONCE Mode Request (input)                       | 37 |

| 2.2.23 | mcs0_n/pio14—Midrange Memory Chip Select (synchronous output          |    |

|        | with internal pullup)                                                 | 37 |

| 2.2.24 | mcs2_n-mcs1_n (pio24-pio 15)—Midrange Memory Chip Selects             |    |

|        | (synchronous outputs with internal pullup)                            | 37 |

| 2.2.25 | mcs3_n/rfsh_n/pio25—Midrange Memory Chip Select (synchronous          |    |

|        | outputs with internal pullup)/Automatic Refresh (synchronous output)  | 38 |

| 2.2.26 | nmi-Nonmaskable Interrupt (synchronous edge-sensitive input)          | 38 |

| 2.2.27 | pcs1_n-pcs0_n (pio17-pio16)—Peripheral Chip Selects 1-0               |    |

|        | (synchronous outputs)                                                 | 38 |

| 2.2.28 | pcs2_n/cts1_n/enrx1_n/pio18—Peripheral Chip Select 2                  |    |

|        | (synchronous output)/Clear-to-Send 1 (asynchronous input)/Enable-     |    |

|        | Receiver-Request 1 (asynchronous input)                               | 39 |

| 2.2.29 | pcs3_n/rts1_n/rtr1_n/pio18—Peripheral Chip Select 3 (synchronous      |    |

|        | output)/Ready-to-Send 1 (asynchronous output)/Ready-to-Receive 1      |    |

|        | (asynchronous input)                                                  | 39 |

| 2.2.30 | pcs5_n/A1/pio3—Peripheral Chip Select 5 (synchronous                  |    |

|        | output)/Latched Address Bit [1] (synchronous output)                  | 40 |

| 2.2.31 | pcs6_n/A2/pio2—Peripheral Chip Select 6 (synchronous                  |    |

|        | output)/Latched Address Bit [2] (synchronous output)                  | 40 |

| 2.2.32 | pio31-pio0-Programmable I/O Pins (asynchronous input/output           |    |

|        | open-drain)                                                           |    |

| 2.2.33 | rd_n—Read strobe (synchronous output with tristate)                   |    |

|        | res_n—Reset (asynchronous level-sensitive input)                      | 40 |

| 2.2.35 | rfsh2_n/aden_n (IA188ES only)—Refresh 2 (synchronous output           |    |

|        | with tristate)/Address Enable (input with internal pullup)            | 41 |

|    |      | 2.2.36 | rts0_n/rtr0_n/pio20—Ready-to-Send 0 (asynchronous output)/Ready-    |    |

|----|------|--------|---------------------------------------------------------------------|----|

|    |      |        | to-Receive 0 (asynchronous input)                                   | 41 |

|    |      | 2.2.37 | rxd0_n/pio23—Receive Data 0 (asynchronous input)                    | 41 |

|    |      | 2.2.38 | rxd1_n/pio28—Receive Data 1 (asynchronous input)                    | 41 |

|    |      | 2.2.39 | s2_n-s0_n—Bus Cycle Status (synchronous outputs with tristate)      | 41 |

|    |      | 2.2.40 | s6/lock_n/clkdiv2_n/pio29—Bus Cycle Status Bit [6] (synchronous     |    |

|    |      |        | output)/Bus Lock (synchronous output)/Clock Divide by 2 (input with |    |

|    |      |        | internal pullup)                                                    |    |

|    |      | 2.2.41 | srdy/pio6—Synchronous Ready (synchronous level-sensitive input)     |    |

|    |      |        | tmrin0/pio11—Timer Input 0 (synchronous edge-sensitive input)       |    |

|    |      |        | tmrin1/pio0—Timer Input 1 (synchronous edge-sensitive input)        |    |

|    |      |        | tmrout0/pio10—Timer Output 0 (synchronous output)                   |    |

|    |      |        | tmrout1/pio1—Timer Output 1 (synchronous output)                    |    |

|    |      |        | txd0/pio22—Transmit Data 0 (asynchronous output)                    |    |

|    |      | 2.2.47 | txd1/pio27—Transmit Data 1 (asynchronous output)                    | 43 |

|    |      | 2.2.48 | ucs_n/once1_n—Upper Memory Chip Select (synchronous                 |    |

|    |      |        | output)/ONCE Mode Request 1 (input with internal pullup)            |    |

|    |      |        | uzi_n/pio26—Upper Zero Indicate (synchronous output)                |    |

|    |      |        | v <sub>cc</sub> —Power Supply (input)                               | 44 |

|    |      | 2.2.51 | whb_n (IA186ES only)—Write High Byte (synchronous output with       |    |

|    |      |        | tristate)                                                           | 44 |

|    |      | 2.2.52 | wlb_n/wb_n—Write Low Byte (IA186ES only) (synchronous output        |    |

|    |      |        | with tristate)/Write Byte (IA188ES only) (synchronous output with   |    |

|    |      |        | tristate)                                                           |    |

|    |      |        | wr_n—Write Strobe (synchronous output)                              |    |

|    |      |        | x1—Crystal Input                                                    |    |

|    |      |        | x2—Crystal Input                                                    |    |

|    | 2.3  |        | sed by Emulators                                                    |    |

| 3. |      |        | atings, Thermal Characteristics, and DC Parameters                  |    |

| 4. |      |        | itecture                                                            |    |

|    | 4.1  |        | terface and Control                                                 |    |

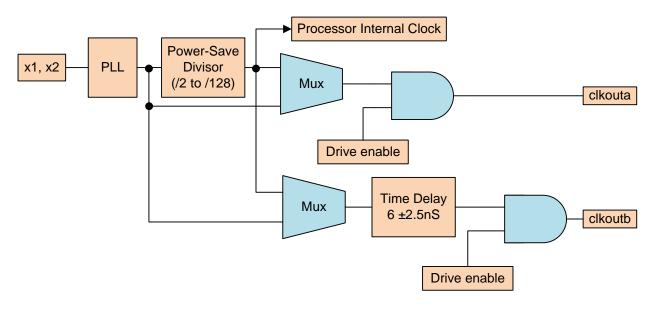

|    | 4.2  |        | and Power Management                                                |    |

|    |      | -      | 1 Clocks                                                            |    |

|    | 4.4  |        | -Save Mode                                                          |    |

|    | 4.5  |        | zation and Reset                                                    |    |

|    | 4.6  |        | Configuration Register                                              |    |

|    | 4.7  | -      | elects                                                              |    |

|    | 4.8  |        | elect Timing                                                        |    |

|    | 4.9  |        | - and Wait-State Programming                                        |    |

|    |      |        | elect Overlap                                                       |    |

|    |      |        | Memory Chip Select                                                  |    |

|    | 4.12 | Low-N  | Iemory Chip Select                                                  | 52 |

|    | 4.13  | Midran  | ge-Memory Chip Selects          | .52 |

|----|-------|---------|---------------------------------|-----|

|    |       |         | eral Chip Selects               |     |

|    |       |         | n Control                       |     |

|    |       |         | pt Control                      |     |

|    |       |         | pt Types                        |     |

|    | 4.18  | Timer   | Control                         | .55 |

|    |       |         | log Timer                       |     |

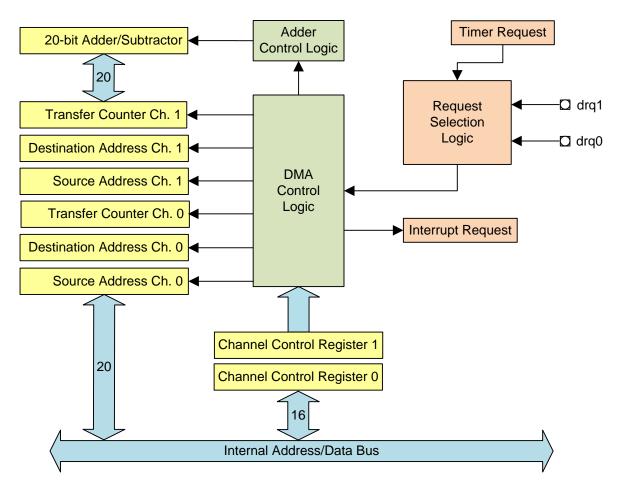

|    | 4.20  | Direct  | Memory Access                   | .57 |

|    | 4.21  | DMA (   | Operation                       | .57 |

|    |       |         | Channel Control Registers       |     |

|    | 4.23  | DMA I   | Priority                        | .59 |

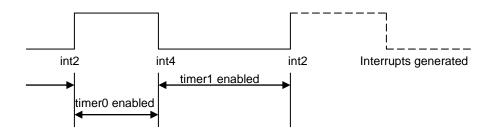

|    | 4.24  | Pulse V | Vidth Demodulation              | .59 |

|    | 4.25  | Asynch  | nronous Serial Ports            | .60 |

|    | 4.26  | Program | mmable I/O                      | .60 |

| 5. | Perip | heral A | rchitecture                     | .62 |

|    | 5.1   | Contro  | l and Registers                 | .62 |

|    |       | 5.1.1   | RELREG (0feh)                   |     |

|    |       | 5.1.2   | RESCON (0f6h)                   | .64 |

|    |       | 5.1.3   | PRL (0f4h)                      | .64 |

|    |       | 5.1.4   | AUXCON (0f2h)                   |     |

|    |       | 5.1.5   | SYSCON (0f0h)                   | .66 |

|    |       | 5.1.6   | WDTCON (0e6h)                   | .67 |

|    |       | 5.1.7   | EDRAM (0e4h)                    | .68 |

|    |       | 5.1.8   | CDRAM (0e2h)                    | .69 |

|    |       | 5.1.9   | MDRAM (0e0h)                    | .69 |

|    |       | 5.1.10  | D1CON (0dah) and D0CON (0cah)   | .69 |

|    |       | 5.1.11  | D1TC (0d8h) and D0TC (0c8h)     | .71 |

|    |       | 5.1.12  | D1DSTH (0d6h) and D0DSTH (0c6h) | .72 |

|    |       | 5.1.13  | DIDSTL (0d4h) and D0DSTL (0c4h) | .72 |

|    |       | 5.1.14  | D1SRCH (0d2h) and D0SRCH (0c2h) | .72 |

|    |       | 5.1.15  | D1SRCL (0d0h) and D0SRCL (0c0h) | .73 |

|    |       |         | MPCS (0a8h)                     |     |

|    |       | 5.1.17  | MMCS (0a6h)                     | .75 |

|    |       | 5.1.18  | PACS (0a4h)                     | .76 |

|    |       |         | LMCS (0a2h)                     |     |

|    |       | 5.1.20  | UMCS (0a0h)                     | .79 |

|    |       | 5.1.21  | SP0BAUD (088h)                  |     |

|    |       |         | SP1BAUD (018h)                  |     |

|    |       | 5.1.23  | SPORD (086h) and SP1RD (016h)   |     |

|    |       | 5.1.24  | SP0TD (084h) and SP1TD (014h)   |     |

|    |       | 5.1.25  | SPOSTS (082h) and SP1STS (012h) |     |

|    |       | 5.1.26  | SPOCT (080h) and SP1CT (010h)   | .84 |

|       | 5.1.27    | PDATA1 (07ah) and PDATA0 (074h)                            | 87  |

|-------|-----------|------------------------------------------------------------|-----|

|       | 5.1.28    | PDIR1 (078h) and PDIR0 (072h)                              | 89  |

|       | 5.1.29    | PMODE1 (076h) and PMODE0 (070h)                            | 90  |

|       |           | T1CON (05eh) and T0CON (056h)                              |     |

|       |           | T2CON (066h)                                               | 92  |

|       | 5.1.32    | T2COMPA (062h), T1COMPB (05ch), T1COMPA (05ah),            |     |

|       |           | T0COMPB (054h), and T0COMPA (052h)                         | 93  |

|       | 5.1.33    | T2CNT (060h), T1CNT (058h), and T0CNT (050h)               | 93  |

|       | 5.1.34    | SPOCON (044h) and SP1CON (042h) (Master Mode)              | 94  |

|       | 5.1.35    | I4CON (040h) (Master Mode)                                 | 95  |

|       | 5.1.36    | I3CON (03eh) and I2CON (03ch) (Master Mode)                | 95  |

|       | 5.1.37    | I1CON (03ah) and I0CON (038h) (Master Mode)                | 96  |

|       | 5.1.38    | TCUCON (032h) (Master Mode)                                | 97  |

|       | 5.1.39    | T2INTCON (03ah), T1INTCON (038h), and T0INTCON (032h)      |     |

|       |           | (Slave Mode)                                               | 97  |

|       | 5.1.40    | DMA1CON/INT6CON (036h) and DMA0CON/INT5CON (034h)          |     |

|       |           | (Master Mode)                                              | 98  |

|       | 5.1.41    | DMA1CON/INT6 (036h) and DMA0CON/INT5 (034h) (Slave         |     |

|       |           | Mode)                                                      | 98  |

|       | 5.1.42    | INTSTS (030h) (Master Mode)                                | 99  |

|       | 5.1.43    | INTSTS (030h) (Slave Mode)                                 | 99  |

|       | 5.1.44    | REQST (02eh) (Master Mode)                                 | 100 |

|       | 5.1.45    | REQST (02eh) (Slave Mode)                                  | 101 |

|       | 5.1.46    | INSERV (02ch) (Master Mode)                                | 101 |

|       | 5.1.47    | INSERV (02ch) (Slave Mode)                                 | 102 |

|       | 5.1.48    | PRIMSK (02ah) (Master and Slave Mode)                      | 103 |

|       | 5.1.49    | IMASK (028h) (Master Mode)                                 | 103 |

|       | 5.1.50    | IMASK (028h) (Slave Mode)                                  | 104 |

|       | 5.1.51    | POLLST (026h) (Master Mode)                                | 105 |

|       |           | POLL (024h) (Master Mode)                                  |     |

|       | 5.1.53    | EOI (022h) End-Of-Interrupt Register (Master Mode)         | 106 |

|       |           | EOI (022h) Specific End-Of-Interrupt Register (Slave Mode) |     |

|       | 5.1.55    | INTVEC (020h) Interrupt Vector Register (Slave Mode)       | 107 |

| 5.2   | Referen   | nce Documents                                              | 107 |

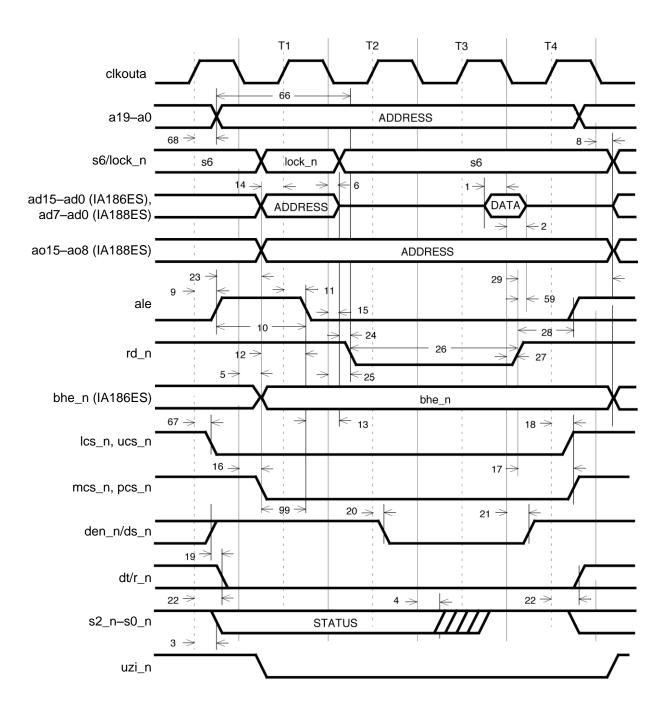

| AC S  | Specifica | tions                                                      | 108 |

| Instr |           | et Summary Table                                           |     |

| 7.1   | Key to    | Abbreviations Used in Instruction Set Summary Table        |     |

|       | 7.1.1     | Operand Address Byte                                       |     |

|       | 7.1.2     | Modifier Field                                             |     |

|       | 7.1.3     | Auxiliary Field                                            |     |

|       | 7.1.4     | r/m Field                                                  | 145 |

|       | 7.1.5     | Displacement                                               | 145 |

6. 7.

|     |       | 7.1.6    | Immediate Bytes                                          |     |

|-----|-------|----------|----------------------------------------------------------|-----|

|     |       | 7.1.7    | Segment Override Prefix                                  |     |

|     |       | 7.1.8    | Segment Register                                         | 145 |

|     | 7.2   | Explar   | nation of Notation Used in Instruction Set Summary Table | 146 |

|     |       | 7.2.1    | Opcode                                                   | 146 |

|     |       | 7.2.2    | Flags Affected After Instruction                         | 147 |

| 8.  | Inno  | vasic/A  | MD Part Number Cross-Reference Tables                    |     |

| 9.  | Errat | ta       |                                                          | 150 |

|     | 9.1   | Errata   | Summary                                                  |     |

|     | 9.2   | Errata   | Detail                                                   |     |

| 10. | Revi  | sion His | story                                                    | 153 |

| 11. | For A | Additior | nal Information                                          |     |

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 8 of 154

# LIST OF FIGURES

| Figure 1. IA186ES TQFP Package Diagram                 | 17  |

|--------------------------------------------------------|-----|

| Figure 2. IA188ES TQFP Package Diagram                 | 20  |

| Figure 3. TQFP Package Dimensions                      | 23  |

| Figure 4. IA186ES PQFP Package Diagram                 | 24  |

| Figure 5. IA188ES PQFP Package Diagram                 | 27  |

| Figure 6. PQFP Package Dimensions                      | 30  |

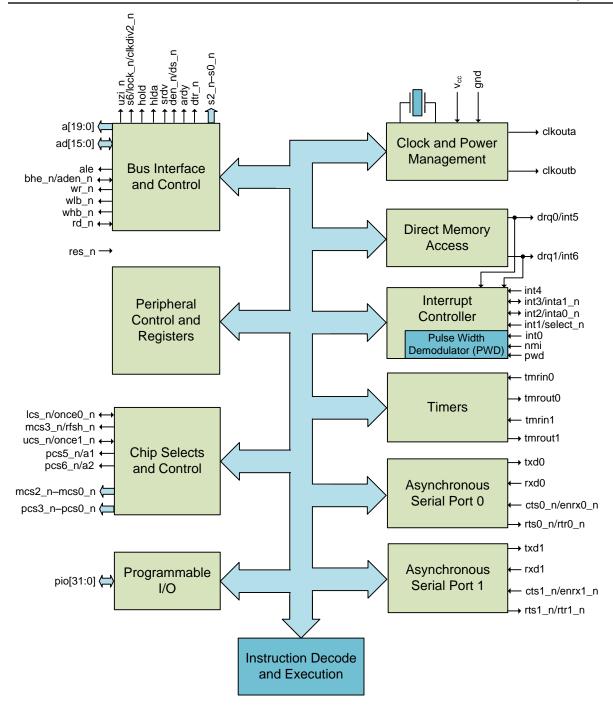

| Figure 7. Functional Block Diagram                     | 48  |

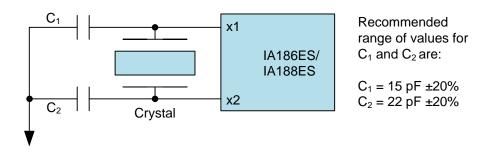

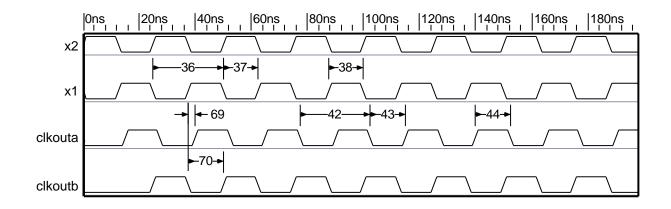

| Figure 8. Crystal Configuration                        | 49  |

| Figure 9. Organization of Clock                        | 49  |

| Figure 10. DMA Unit                                    | 58  |

| Figure 11. Typical Waveform at the int2/int0_n/pwd pin | 59  |

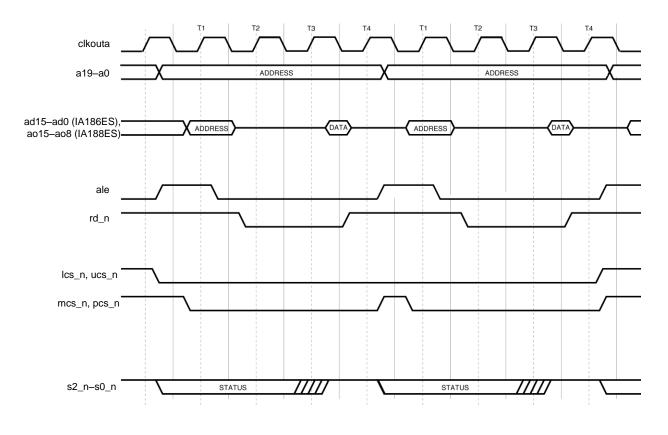

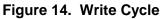

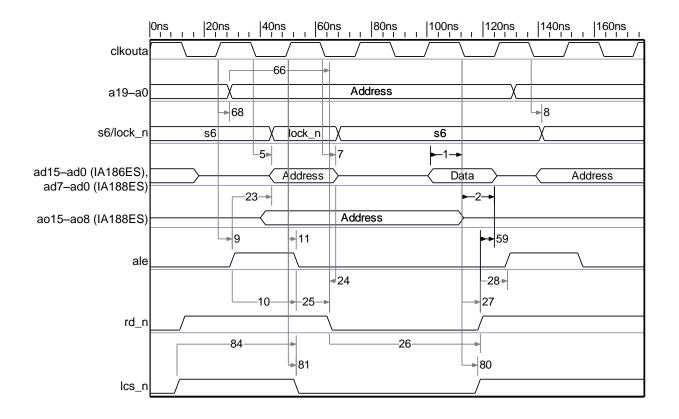

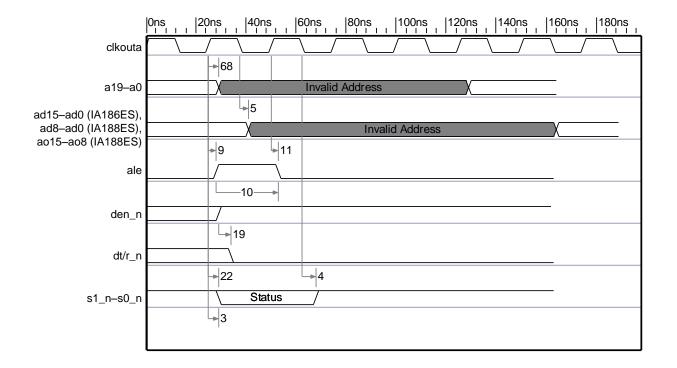

| Figure 12. Read Cycle                                  |     |

| Figure 13. Multiple Read Cycles                        | 114 |

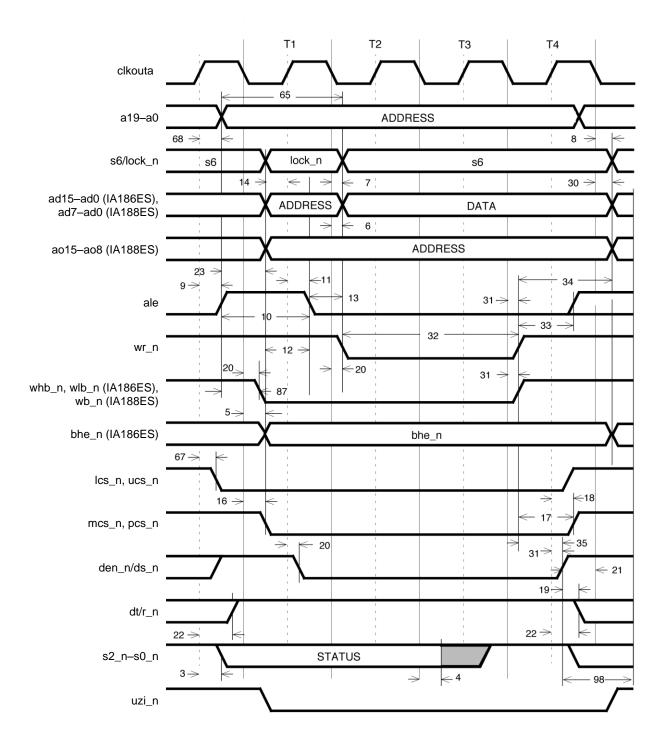

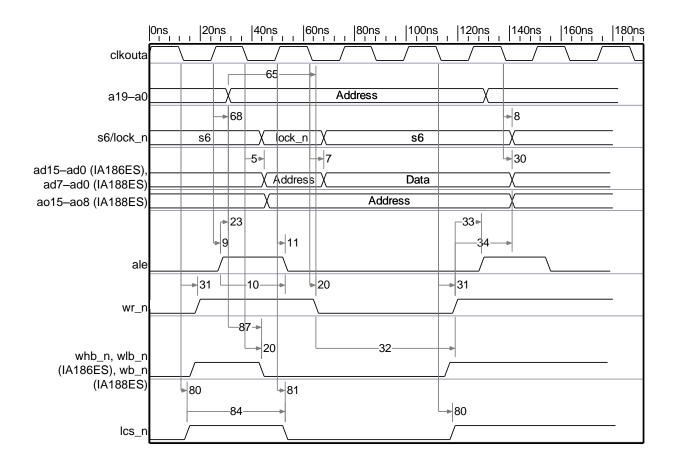

| Figure 14. Write Cycle                                 | 116 |

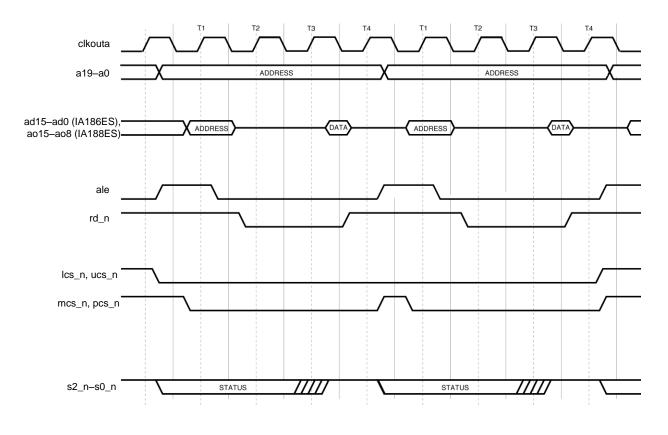

| Figure 15. Multiple Write Cycles                       | 117 |

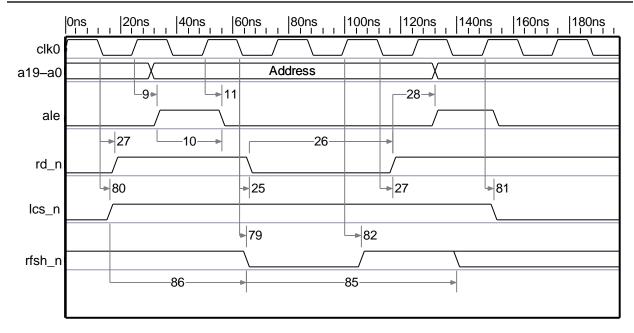

| Figure 16. PSRAM Read Cycle                            | 119 |

| Figure 17. PSRAM Write Cycle                           | 121 |

| Figure 18. PSRAM Refresh Cycle                         | 123 |

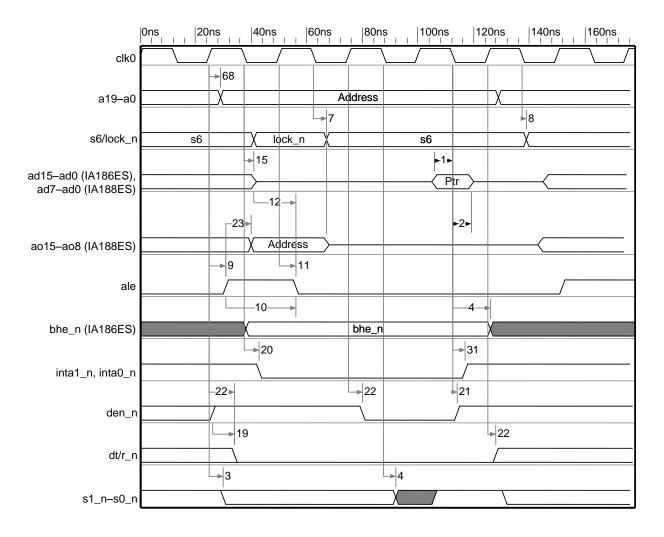

| Figure 19. Interrupt Acknowledge Cycle                 | 124 |

| Figure 20. Software Halt Cycle                         | 126 |

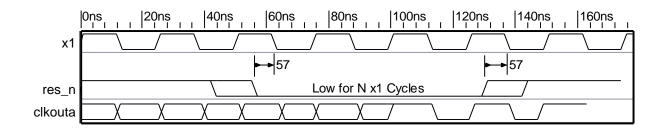

| Figure 21. Clock—Active Mode                           |     |

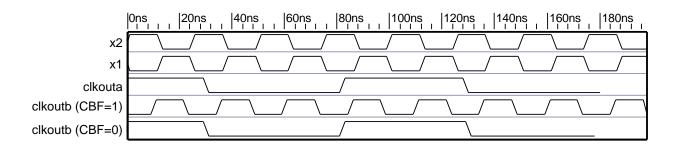

| Figure 22. Clock—Power-Save Mode                       | 128 |

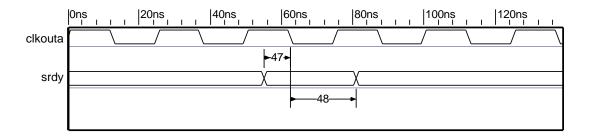

| Figure 23. srdy—Synchronous Ready                      | 129 |

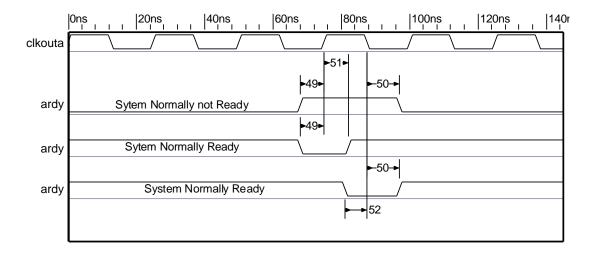

| Figure 24. ardy—Asynchronous Ready                     | 130 |

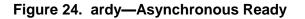

| Figure 25. Peripherals                                 | 130 |

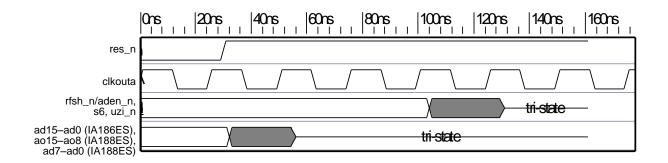

| Figure 26. Reset 1                                     | 131 |

| Figure 27. Reset 2                                     | 131 |

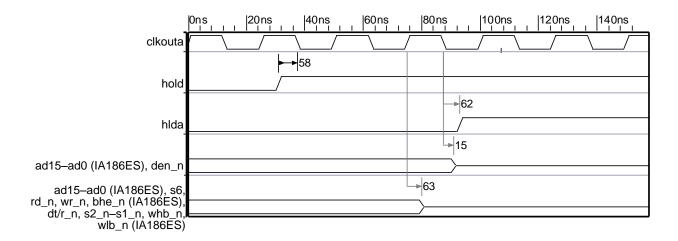

| Figure 28. Bus Hold Entering                           | 132 |

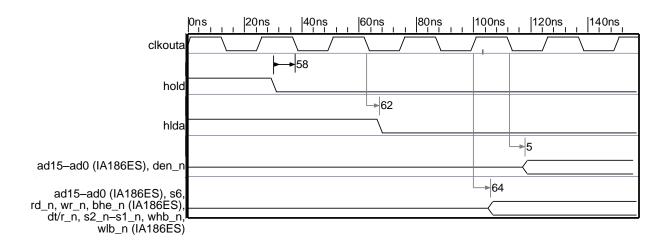

| Figure 29. Bus Hold Leaving                            | 132 |

# LIST OF TABLES

| Table 1. IA186ES TQFP Numeric Pin Listing                           | 18 |

|---------------------------------------------------------------------|----|

| Table 2. IA186ES TQFP Alphabetic Pin Listing                        | 19 |

| Table 3. IA188ES TQFP Numeric Pin Listing                           |    |

| Table 4. IA188ES TQFP Alphabetic Pin Listing                        | 22 |

| Table 5. IA186ES PQFP Numeric Pin Listing                           |    |

| Table 6. IA186ES PQFP Alphabetic Pin Listing                        | 26 |

| Table 7. IA188ES PQFP Numeric Pin Listing                           | 28 |

| Table 8. IA188ES PQFP Alphabetic Pin Listing                        |    |

| Table 9. Bus Cycle Types for bhe_n and ad0                          |    |

| Table 10. Bus Cycle Types for s2_n, s1_n, and s0_n                  | 42 |

| Table 11. IA186ES and IA188ES Absolute Maximum Ratings              | 45 |

| Table 12. IA186ES and IA188ES Thermal Characteristics               | 45 |

| Table 13. DC Characteristics Over Commercial Operating Ranges       | 46 |

| Table 14. Interrupt Types                                           |    |

| Table 15. Default Status of PIO Pins at Reset                       | 61 |

| Table 16. Peripheral Control Registers                              | 63 |

| Table 17. Peripheral Control Block Relocation Register              | 64 |

| Table 18. Reset Configuration Register                              | 64 |

| Table 19. Processor Release Level Register                          | 65 |

| Table 20. Auxiliary Configuration Register                          | 65 |

| Table 21. System Configuration Register                             | 66 |

| Table 22.    Watchdog Timer Control Register                        | 67 |

| Table 23. Enable Dynamic RAM Refresh Control Register               | 68 |

| Table 24. Count for Dynamic RAM Refresh Control Register            |    |

| Table 25. Memory Partition for Dynamic RAM Refresh Control Register | 69 |

| Table 26. DMA Control Registers                                     | 69 |

| Table 27. DMA Transfer Count Registers                              | 71 |

| Table 28. DMA Destination Address High Register                     | 72 |

| Table 29. DMA Destination Address Low Register                      | 72 |

| Table 30. DMA Source Address High Register                          | 73 |

| Table 31. DMA Source Address Low Register                           | 73 |

| Table 32. MCS and PCS Auxiliary Register                            | 74 |

| Table 33. Midrange Memory Chip Select Register                      | 75 |

| Table 34. Peripheral Chip Select Register                           |    |

| Table 35. Low-Memory Chip Select Register                           | 78 |

| Table 36. Upper-Memory Chip Select Register                         | 79 |

| Table 37. Baud Rates                                                | 81 |

| Table 38. Serial Port Baud Rate Divisor Registers                   | 81 |

| Table 39. Serial Port Receive Registers                             |    |

| Table 40.    Serial Port Transmit Registers                         | 82 |

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 10 of 154

| Table 41. | Serial Port Status Register                      | .83 |

|-----------|--------------------------------------------------|-----|

| Table 42. | Serial Port Control Registers                    | 84  |

| Table 43. | PIO Pin Assignments                              | .88 |

| Table 44. | PDATA 0                                          | .89 |

| Table 45. | PDATA 1                                          | .89 |

| Table 46. | PIO Mode and PIO Direction Settings              | .89 |

|           | PDIR0                                            |     |

| Table 48. | PDIR1                                            | .90 |

| Table 49. | PMODE0                                           | .90 |

| Table 50. | PMODE1                                           | .90 |

| Table 51. | Timer0 and Timer1 Mode and Control Registers     | .91 |

|           | Timer2 Mode and Control Registers                |     |

| Table 53. | Timer Maxcount Compare Registers                 | .93 |

| Table 54. | Timer Count Registers                            | .94 |

| Table 55. | Serial Port Interrupt Control Registers          | .94 |

| Table 56. | INT4 Control Register                            | .95 |

| Table 57. | INT2/INT3 Control Register                       | .96 |

|           | INT0/INT1 Control Register                       |     |

| Table 59. | Timer Control Unit Interrupt Control Register    | .97 |

|           | Timer Interrupt Control Register                 |     |

| Table 61. | DMA and Interrupt Control Register (Master Mode) | .98 |

| Table 62. | DMA and Interrupt Control Register (Slave Mode)  | .98 |

| Table 63. | Interrupt Status Register (Master Mode)          | .99 |

|           | Interrupt Status Register (Slave Mode)           |     |

| Table 65. | Interrupt Request Register (Master Mode)         | 100 |

| Table 66. | Interrupt Request Register (Slave Mode)          | 101 |

| Table 67. | In-Service Register (Master Mode)                | 102 |

| Table 68. | In-Service Register (Slave Mode)                 | 102 |

|           | Priority Mask Register                           |     |

| Table 70. | Interrupt MASK Register (Master Mode)            | 104 |

| Table 71. | Interrupt MASK Register (Slave Mode)             | 104 |

| Table 72. | POLL Status Register                             | 105 |

| Table 73. | Poll Register                                    | 106 |

| Table 74. | End-Of-Interrupt Register                        | 106 |

| Table 75. | Specific End-Of-Interrupt Register               | 106 |

| Table 76. | Interrupt Vector Register                        | 107 |

| Table 77. | Alphabetic Key to Waveform Parameters            | 108 |

|           | Numeric Key to Waveform Parameters               |     |

| Table 79. | Read Cycle Timing                                | 115 |

| Table 80. | Write Cycle Timing                               | 118 |

| Table 81. | PSRAM Read Cycle Timing                          | 120 |

| Table 82. | PSRAM Write Cycle Timing                         | 122 |

| Table 83. | PSRAM Refresh Cycle Timing                             |     |

|-----------|--------------------------------------------------------|-----|

| Table 84. | Interrupt Acknowledge Cycle Timing                     |     |

| Table 85. | Software Halt Cycle Timing                             |     |

| Table 86. | Clock Timing                                           |     |

| Table 87. | Ready and Peripheral Timing                            |     |

| Table 88. | Reset and Bus Hold Timing                              |     |

| Table 89. | Instruction Set Summary                                |     |

| Table 90. | Innovasic/AMD Part Number Cross-Reference for the TQFP | 148 |

| Table 91. | Innovasic/AMD Part Number Cross-Reference for the PQFP |     |

| Table 92. | Summary of Errata                                      |     |

| Table 93. | Revision History                                       |     |

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 12 of 154

#### CONVENTIONS

**Arial Bold** Designates headings, figure captions, and table captions.

Blue Designates hyperlinks (PDF copy only).

*Italics* Designates emphasis or caution related to nearby information. Italics is also used to designate variables, refer to related documents, and to differentiate terms from other common words (e.g., "During refresh cycles, the *a* and *ad* busses may not have the same address during the address phase of the *ad* bus cycle.").

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 13 of 154

# ACRONYMS AND ABBREVIATIONS

| AMD®                | Advanced Micro Devices                      |

|---------------------|---------------------------------------------|

| BIC                 | Bus Interface and Control                   |

| CDRAM               | Count for Dynamic RAM                       |

| CSC                 | Chip Selects and Control                    |

| DA                  | Disable Address                             |

| DMA                 | Direct Memory Access                        |

| EOI                 | End of Interrupt                            |

| INSERV              | In-Service                                  |

| ISR                 | Interrupt Service Routine                   |

| LMCS                | Low-Memory Chip Select                      |

| MC                  | Maximum Count                               |

| MDRAM               | Memory Partition for Dynamic RAM            |

| MILES <sup>TM</sup> | Managed IC Lifetime Extension System        |

| MMCS                | Midrange Memory Chip Select                 |

| NMI                 | nonmaskable interrupt                       |

| PCB                 | peripheral control block                    |

| PIO                 | programmable I/O                            |

| PLL                 | phase-lock-loop                             |

| POR                 | power-on reset                              |

| PQFP                | Plastic Quad Flat Package                   |

| PSRAM               | Pseudo-Static RAM                           |

| RCU                 | Refresh Control Unit                        |

| RoHS                | Restriction of Hazardous Substances         |

| SFNM                | Special Fully Nested mode                   |

| SYSCON              | System Configuration Register               |

| TQFP                | Thin Quad Flat Package                      |

| UART                | Universal Asynchronous Receiver-Transmitter |

| UMCS                | Upper Memory Chip Select                    |

| WDT                 | Watchdog Timer                              |

|                     |                                             |

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 14 of 154

# 1. Introduction

These devices are produced using Innovasic's Managed IC Lifetime Extension System (MILES<sup>TM</sup>). This cloning technology, which produces replacement ICs beyond simple emulations, is designed to achieve compatibility with the original device, including any "undocumented features." Please note that there may be some functional differences between the Innovasic device and the original device and customers should thoroughly test the device in system to ensure compatibility. Innovasic reports all known functional differences in the Errata section of this data sheet. Additionally, MILES<sup>TM</sup> captures the clone design in such a way that production of the clone can continue even as silicon technology advances.

### 1.1 General Description

The IA186ES/IA188ES family of microcontrollers replaces obsolete AMD Am186ES/188ES devices, allowing customers to retain existing board designs, software compilers/assemblers, and emulation tools and thus avoid expensive redesign efforts.

The IA186ES/IA188ES microcontrollers are an upgrade for the 80C186/188 microcontroller designs, with integrated peripherals to provide increased functionality and reduce system costs. The Innovasic devices are designed to satisfy requirements of embedded products designed for telecommunications, office automation/storage, and industrial controls.

#### 1.2 Features

- Pin-for-pin compatible with AMD Am186ES/188ES devices

- All features are retained, including:

- A phase-lock loop (PLL) allowing same crystal/system clock frequency

- An 8086/8088 instruction set with additional 186 instruction set extensions

- A programmable interrupt controller

- Two Direct Memory Access (DMA) channels

- Three 16-bit timers

- A wait-state generator and programmable chip select logic

- A dedicated watchdog timer (WDT)

- Two independent asynchronous serial ports (UARTs)

- DMA capability

- $\circ$  Hardware flow control

- 0 7-, 8-, or 9-bit data capability

- Pulse width demodulator feature

- Up to 32 programmable I/O (PIO) pins

- A pseudo-static/dynamic RAM controller

- A fully static CMOS design

- 40-MHz operation at industrial operating conditions

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 15 of 154 • +5-VDC power supply

# 2. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions for the IA186ES and the IA188ES is provided separately. Refer to sections, figures, and tables for information on the device of interest.

#### 2.1 Packages and Pinouts

The Innovasic Semiconductor IA186ES and IA188ES microcontroller is available in the following packages:

- 100-Pin Thin Quad Flat Package (TQFP), equivalent to original SQFP package

- 100-Plastic Quad Flat Package (PQFP), equivalent to original PQFP package

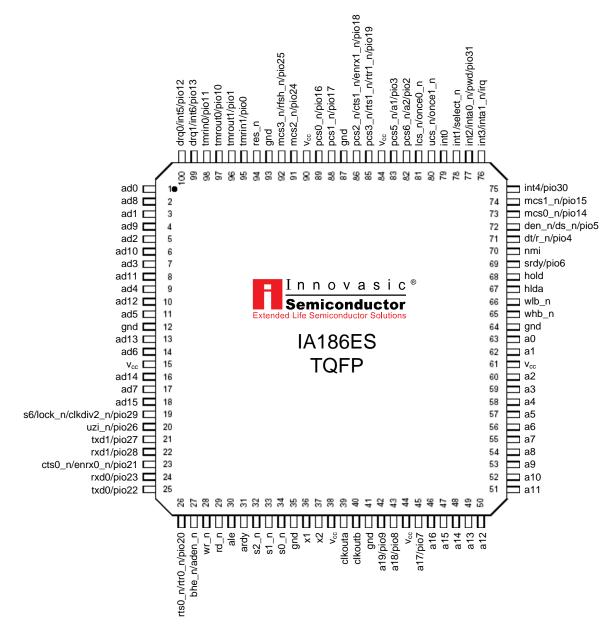

#### 2.1.1 IA186ES TQFP Package

The pinout for the IA186ES TQFP package is as shown in Figure 1. The corresponding pinout is provided in Tables 1 and 2.

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 17 of 154

http://www.innovasic.com Customer Support: 1-888-824-4184

| Pin | Name                      |

|-----|---------------------------|

| 1   | ad0                       |

| 2   | ad8                       |

| 3   | ad1                       |

| 4   | ad9                       |

| 5   | ad2                       |

| 6   | ad10                      |

| 7   | ad3                       |

| 8   | ad11                      |

| 9   | ad4                       |

| 10  | ad12                      |

| 11  | ad5                       |

| 12  | gnd                       |

| 13  | ad13                      |

| 14  | ad6                       |

| 15  | V <sub>CC</sub>           |

| 16  | ad14                      |

| 17  | ad7                       |

| 18  | ad15                      |

| 19  | s6/lock_n/clkdiv2_n/pio29 |

| 20  | uzi_n/pio26               |

| 21  | txd1/pio27                |

| 22  | rxd1/pio28                |

| 23  | cts0_n/enrx0_n/pio21      |

| 24  | rxd0/pio23                |

| 25  | txd0/pio22                |

| 26  | rts0_n/rtr0_n/pio20       |

| 27  | bhe_n/aden_n              |

| 28  | wr_n                      |

| 29  | rd_n                      |

| 30  | ale                       |

| 31  | ardy                      |

| 32  | s2_n                      |

| 33  | s1_n                      |

| 34  | s0_n                      |

# Table 1. IA186ES TQFP Numeric Pin Listing

| Pin | Name            |

|-----|-----------------|

| 35  | gnd             |

| 36  | x1              |

| 37  | x2              |

| 38  | V <sub>CC</sub> |

| 39  | clkouta         |

| 40  | clkoutb         |

| 41  | gnd             |

| 42  | a19/pio9        |

| 43  | a18/pio8        |

| 44  | V <sub>CC</sub> |

| 45  | a17/pio7        |

| 46  | a16             |

| 47  | a15             |

| 48  | a14             |

| 49  | a13             |

| 50  | a12             |

| 51  | a11             |

| 52  | a10             |

| 53  | a9              |

| 54  | a8              |

| 55  | а7              |

| 56  | a6              |

| 57  | a5              |

| 58  | a4              |

| 59  | a3              |

| 60  | a2              |

| 61  | V <sub>CC</sub> |

| 62  | a1              |

| 63  | a0              |

| 64  | gnd             |

| 65  | whb_n           |

| 66  | wlb_n           |

| 67  | hlda            |

| Pin | Name                        |

|-----|-----------------------------|

| 68  | hold                        |

| 69  | srdy/pio6                   |

| 70  | nmi                         |

| 71  | dt/r_n/pio4                 |

| 72  | den_n/ds_n/pio5             |

| 73  | mcs0_n/pio14                |

| 74  | mcs1_n/pio15                |

| 75  | int4/pio30                  |

| 76  | int3/inta1_n/irq            |

| 77  | int2/inta0_n/pwd/pio31      |

| 78  | int1/select_n               |

| 79  | int0                        |

| 80  | ucs_n/once1_n               |

| 81  | lcs_n/once0_n               |

| 82  | pcs6_n/a2/pio2              |

| 83  | pcs5_n/a1/pio3              |

| 84  | V <sub>CC</sub>             |

| 85  | pcs3_n/rts1_n/rtr1_n/pio19  |

| 86  | pcs2_n/cts1_n/enrx1_n/pio18 |

| 87  | gnd                         |

| 88  | pcs1_n/pio17                |

| 89  | pcs0_n/pio16                |

| 90  | V <sub>CC</sub>             |

| 91  | mcs2_n/pio24                |

| 92  | mcs3_n/rfsh_n/pio25         |

| 93  | gnd                         |

| 94  | res_n                       |

| 95  | tmrin1/pio0                 |

| 96  | tmrout1/pio1                |

| 97  | tmrout0/pio10               |

| 98  | tmrin0/pio11                |

| 99  | drq1/int6/pio13             |

| 100 | drq0/int5/pio12             |

| Name     | Pin | Name Pin Name          |     | Pin                         |    |

|----------|-----|------------------------|-----|-----------------------------|----|

| a0       | 63  | ad14                   | 16  | pcs2_n/cts1_n/enrx1_n/pio18 | 86 |

| a1       | 62  | ad15                   | 18  | pcs3_n/rts1_n/rtr1_n/pio19  | 85 |

| a2       | 60  | ale                    | 30  | pcs5_n/a1/pio3              | 83 |

| a3       | 59  | ardy                   | 30  | pcs6_n/a2/pio2              | 82 |

| a4       | 58  | bhe_n/aden_n           | 27  | rd_n                        | 29 |

| а5       | 57  | clkouta                | 39  | res_n                       | 94 |

| a6       | 56  | clkoutb                | 40  | rts0_n/rtr0_n/pio20         | 26 |

| а7       | 55  | cts0_n/enrx0_n/pio21   | 23  | rxd0/pio23                  | 24 |

| a8       | 54  | den_n/ds_n/pio5        | 72  | rxd1/pio28                  | 22 |

| a9       | 53  | drq0/int5/pio12        | 100 | s0_n                        | 34 |

| a10      | 52  | drq1/int6/pio13        | 99  | s1_n                        | 33 |

| a11      | 51  | dt/r_n/pio4            | 71  | s2_n                        | 32 |

| a12      | 50  | gnd                    | 12  | s6/lock_n/clkdiv2_n/pio29   | 19 |

| a13      | 49  | gnd                    | 36  | srdy/pio6                   | 69 |

| a14      | 48  | gnd                    | 41  | tmrin0/pio11                | 98 |

| a15      | 47  | gnd                    | 64  | tmrin1/pio0                 | 95 |

| a16      | 46  | gnd                    | 87  | tmrout0/pio10               | 97 |

| a17/pio7 | 45  | gnd                    | 93  | tmrout1/pio1                | 96 |

| a18/pio8 | 43  | hlda                   | 67  | txd0/pio22                  | 25 |

| a19/pio9 | 42  | hold                   | 68  | txd1/pio27                  | 21 |

| ad0      | 1   | int0                   | 79  | ucs_n/once1_n               | 80 |

| ad1      | 3   | int1/select_n          | 78  | uzi_n/pio26                 | 20 |

| ad2      | 5   | int2/inta0_n/pwd/pio31 | 77  | V <sub>CC</sub>             | 15 |

| ad3      | 7   | int3/inta1_n/irq       | 76  | V <sub>CC</sub>             | 38 |

| ad4      | 9   | int4/pio30             | 75  | V <sub>CC</sub>             | 44 |

| ad5      | 11  | lcs_n/once0_n          | 81  | V <sub>CC</sub>             | 61 |

| ad6      | 14  | mcs0_n/pio14           | 73  | V <sub>CC</sub>             | 84 |

| ad7      | 17  | mcs1_n/pio15           | 74  | V <sub>CC</sub>             | 90 |

| ad8      | 2   | mcs2_n/pio24           | 91  | whb_n                       | 65 |

| ad9      | 4   | mcs3_n/rfsh_n/pio25    | 92  | wlb_n                       | 66 |

| ad10     | 6   | nmi                    | 70  | wr_n                        | 28 |

| ad11     | 8   | pcs0_n/pio16           | 89  | x1                          | 36 |

| ad12     | 10  | pcs1_npio              | 88  | x2                          | 37 |

| ad13     | 13  |                        |     |                             |    |

# Table 2. IA186ES TQFP Alphabetic Pin Listing

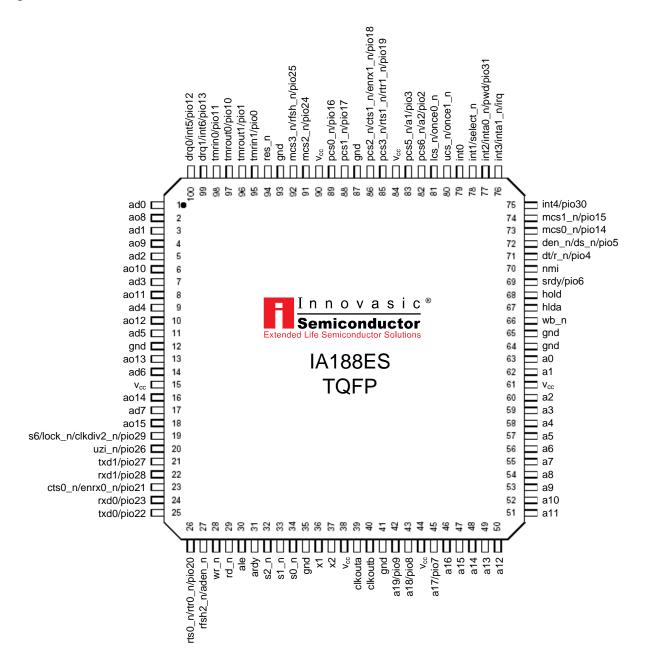

#### 2.1.2 IA188ES TQFP Package

The pinout for the IA186ES TQFP package is as shown in Figure 2. The corresponding pinout is provided in Tables 3 and 4.

#### Figure 2. IA188ES TQFP Package Diagram

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 20 of 154

http://www.innovasic.com Customer Support: 1-888-824-4184

| Pin | Name                      |

|-----|---------------------------|

| 1   | ad0                       |

| 2   | ao8                       |

| 3   | ad1                       |

| 4   | ao9                       |

| 5   | ad2                       |

| 6   | ao10                      |

| 7   | ad3                       |

| 8   | ao11                      |

| 9   | ad4                       |

| 10  | ao12                      |

| 11  | ad5                       |

| 12  | gnd                       |

| 13  | ao13                      |

| 14  | ad6                       |

| 15  | V <sub>CC</sub>           |

| 16  | ao14                      |

| 17  | ad7                       |

| 18  | ao15                      |

| 19  | s6/lock_n/clkdiv2_n/pio29 |

| 20  | uzi_n/pio26               |

| 21  | txd1/pio27                |

| 22  | rxd1/pio28                |

| 23  | cts0_n/enrx0_n/pio21      |

| 24  | rxd0/pio23                |

| 25  | txd0/pio22                |

| 26  | rts0_n/rtr0_n/pio20       |

| 27  | rfsh2_n/aden_n            |

| 28  | wr_n                      |

| 29  | rd_n                      |

| 30  | ale                       |

| 31  | ardy                      |

| 32  | s2_n                      |

| 33  | s1_n                      |

| 34  | s0_n                      |

# Table 3. IA188ES TQFP Numeric Pin Listing

| Pin | Name            |

|-----|-----------------|

| 35  | gnd             |

| 36  | x1              |

| 37  | x2              |

| 38  | V <sub>CC</sub> |

| 39  | clkouta         |

| 40  | clkoutb         |

| 41  | gnd             |

| 42  | a19/pio9        |

| 43  | a18/pio8        |

| 44  | V <sub>CC</sub> |

| 45  | a17/pio7        |

| 46  | a16             |

| 47  | a15             |

| 48  | a14             |

| 49  | a13             |

| 50  | a12             |

| 51  | a11             |

| 52  | a10             |

| 53  | a9              |

| 54  | a8              |

| 55  | а7              |

| 56  | a6              |

| 57  | а5              |

| 58  | a4              |

| 59  | a3              |

| 60  | a2              |

| 61  | V <sub>CC</sub> |

| 62  | a1              |

| 63  | a0              |

| 64  | gnd             |

| 65  | gnd             |

| 66  | wb_n            |

| 67  | hlda            |

| Pin | Name                        |

|-----|-----------------------------|

| 68  | hold                        |

| 69  | srdy/pio6                   |

| 70  | nmi                         |

| 71  | dt/r_n/pio4                 |

| 72  | den_n/ds_n/pio5             |

| 73  | mcs0_n/pio14                |

| 74  | mcs1_n/pio15                |

| 75  | int4/pio30                  |

| 76  | int3/inta1_n/irq            |

| 77  | int2/inta0_n/pwd/pio31      |

| 78  | int1/select_n               |

| 79  | int0                        |

| 80  | ucs_n/once1_n               |

| 81  | lcs_n/once0_n               |

| 82  | pcs6_n/a2/pio2              |

| 83  | pcs5_n/a1/pio3              |

| 84  | V <sub>CC</sub>             |

| 85  | pcs3_n/rts1_n/rtr1_n/pio19  |

| 86  | pcs2_n/cts1_n/enrx1_n/pio18 |

| 87  | gnd                         |

| 88  | pcs1_n/pio17                |

| 89  | pcs0_n/pio16                |

| 90  | V <sub>CC</sub>             |

| 91  | mcs2_n/pio24                |

| 92  | mcs3_n/rfsh_n/pio25         |

| 93  | gnd                         |

| 94  | res_n                       |

| 95  | tmrin1/pio0                 |

| 96  | tmrout1/pio1                |

| 97  | tmrout0/pio10               |

| 98  | tmrin0/pio11                |

| 99  | drq1/int6/pio13             |

| 100 | drq0/int5/pio12             |

| Name     | Pin | Name                   | Pin | Name                        | Pin |

|----------|-----|------------------------|-----|-----------------------------|-----|

| a0       | 63  | ao13                   | 13  | pcs2_n/cts1_n/enrx1_n/pio18 | 86  |

| a1       | 62  | ao14                   | 16  | pcs3_n/rts1_n/rtr1_n/pio19  | 85  |

| a2       | 60  | ao15                   | 18  | pcs5_n/a1/pio3              | 83  |

| a3       | 59  | ardy                   | 30  | pcs6_n/a2/pio2              | 82  |

| a4       | 58  | clkouta                | 39  | rd_n                        | 29  |

| а5       | 57  | clkoutb                | 40  | res_n                       | 94  |

| a6       | 56  | cts0_n/enrx0_n/pio21   | 23  | rfsh_n/aden_n               | 27  |

| а7       | 55  | den_n/ds_n/pio5        | 72  | rts0_n/rtr0_n/pio20         | 26  |

| a8       | 54  | drq0/int5/pio12        | 100 | rxd0/pio23                  | 24  |

| a9       | 53  | drq1/int6/pio13        | 99  | rxd1/pio28                  | 22  |

| a10      | 52  | dt/r_n/pio4            | 71  | s0_n                        | 34  |

| a11      | 51  | gnd                    | 12  | s1_n                        | 33  |

| a12      | 50  | gnd                    | 35  | s2_n                        | 32  |

| a13      | 49  | gnd                    | 41  | s6/lock_n/clkdiv2_n/pio29   | 19  |

| a14      | 48  | gnd                    | 64  | srdy/pio6                   | 69  |

| a15      | 47  | gnd                    | 65  | tmrin0/pio11                | 98  |

| a16      | 46  | gnd                    | 87  | tmrin1/pio0                 | 95  |

| a17/pio7 | 45  | gnd                    | 93  | tmrout0/pio10               | 97  |

| a18/pio8 | 43  | hlda                   | 67  | tmrout1/pio1                | 96  |

| a19/pio9 | 42  | hold                   | 68  | txd0/pio22                  | 25  |

| ale      | 30  | int0                   | 79  | txd1/pio27                  | 21  |

| ad0      | 1   | int1/select_n          | 78  | ucs_n/once1_n               | 80  |

| ad1      | 3   | int2/inta0_n/pwd/pio31 | 77  | uzi_n/pio26                 | 20  |

| ad2      | 5   | int3/inta1_n/irq       | 76  | V <sub>CC</sub>             | 15  |

| ad3      | 7   | int4/pio30             | 75  | V <sub>CC</sub>             | 38  |

| ad4      | 9   | lcs_n/once0_n          | 81  | V <sub>CC</sub>             | 44  |

| ad5      | 11  | mcs0_n/pio14           | 73  | V <sub>CC</sub>             | 61  |

| ad6      | 14  | mcs1_n/pio15           | 74  | V <sub>CC</sub>             | 84  |

| ad7      | 17  | mcs2_n/pio24           | 91  | V <sub>CC</sub>             | 90  |

| ao8      | 2   | mcs3_n/rfsh_n/pio25    | 92  | wb_n                        | 66  |

| ao9      | 4   | nmi                    | 70  | wr_n                        | 28  |

| ao10     | 6   | pcs0_n/pio16           | 89  | x1                          | 36  |

| ao11     | 8   | pcs1_n/pio17           | 88  | x2                          | 37  |

| ao12     | 10  |                        |     |                             |     |

# Table 4. IA188ES TQFP Alphabetic Pin Listing

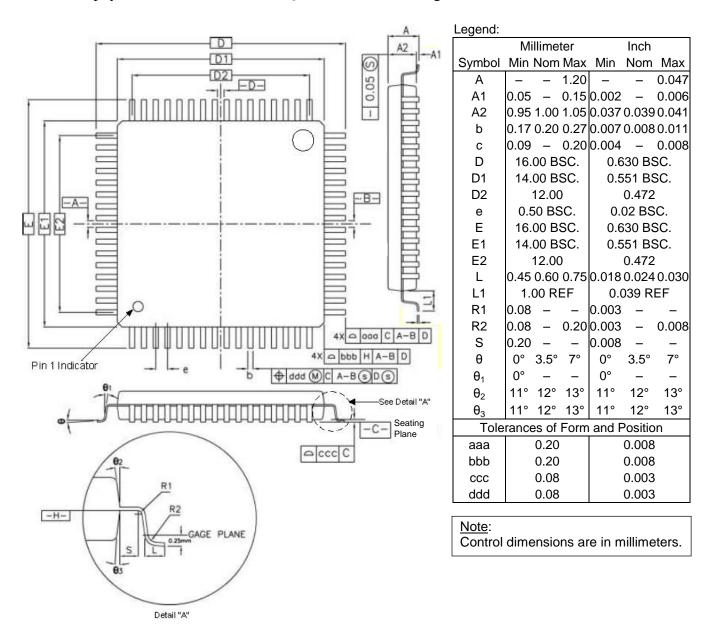

#### 2.1.3 TQFP Physical Dimensions

The physical dimensions for the TQFP are as shown in Figure 3.

Figure 3. TQFP Package Dimensions

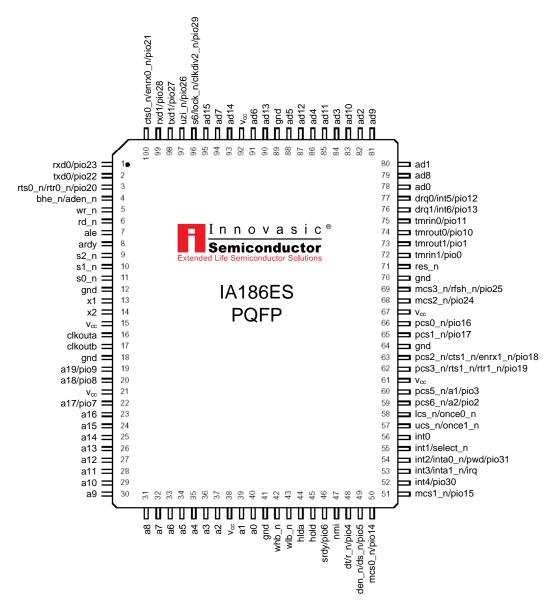

#### 2.1.4 IA186ES PQFP Package

The pinout for the IA186ES PQFP package is as shown in Figure 4. The corresponding pinout is provided in Tables 5 and 6.

Figure 4. IA186ES PQFP Package Diagram

| Pin | Name                | Pin | Name                        | Pin | Name                      |

|-----|---------------------|-----|-----------------------------|-----|---------------------------|

| 1   | rxd0/pio23          | 35  | a4                          | 68  | mcs2_n/pio24              |

| 2   | txd0/pio22          | 36  | a3                          | 69  | mcs3_n/rfsh_n/pio25       |

| 3   | rts0_n/rtr0_n/pio20 | 37  | a2                          | 70  | gnd                       |

| 4   | bhe_n/aden_n        | 38  | V <sub>CC</sub>             | 71  | res_n                     |

| 5   | wr_n                | 39  | a1                          | 72  | tmrin1/pio0               |

| 6   | rd_n                | 40  | a0                          | 73  | tmrout1/pio1              |

| 7   | ale                 | 41  | gnd                         | 74  | tmrout0/pio10             |

| 8   | ardy                | 42  | whb_n                       | 75  | tmrin0/pio11              |

| 9   | s2_n                | 43  | wlb_n                       | 76  | drq1/int6/pio13           |

| 10  | s1_n                | 44  | hlda                        | 77  | drq0/int5/pio12           |

| 11  | s0_n                | 45  | hold                        | 78  | ad0                       |

| 12  | gnd                 | 46  | srdy/pio6                   | 79  | ad8                       |

| 13  | x1                  | 47  | nmi                         | 80  | ad1                       |

| 14  | x2                  | 48  | dt/r_n/pio4                 | 81  | ad9                       |

| 15  | V <sub>CC</sub>     | 49  | den_n/ds_n/pio5             | 82  | ad2                       |

| 16  | clkouta             | 50  | mcs0_n/pio14                | 83  | ad10                      |

| 17  | clkoutb             | 51  | mcs1_n/pio15                | 84  | ad3                       |

| 18  | gnd                 | 52  | int4/pio30                  | 85  | ad11                      |

| 19  | a19/pio9            | 53  | int3/inta1_n/irq            | 86  | ad4                       |

| 20  | a18/pio8            | 54  | int2/inta0_n/pwd/pio31      | 87  | ad12                      |

| 21  | V <sub>CC</sub>     | 55  | int1/select_n               | 88  | ad5                       |

| 22  | a17/pio7            | 56  | int0                        | 89  | gnd                       |

| 23  | a16                 | 57  | ucs_n/once1_n               | 90  | ad13                      |

| 24  | a15                 | 58  | lcs_n/once0_n               | 91  | ad6                       |

| 25  | a14                 | 59  | pcs6_n/a2/pio2              | 92  | V <sub>CC</sub>           |

| 26  | a13                 | 60  | pcs5_n/a1/pio3              | 93  | ad14                      |

| 27  | a12                 | 61  | V <sub>CC</sub>             | 94  | ad7                       |

| 28  | a11                 | 62  | pcs3_n/rts1_n/rtr1_n/pio19  | 95  | ad15                      |

| 29  | a10                 | 63  | pcs2_n/cts1_n/enrx1_n/pio18 | 96  | s6/lock_n/clkdiv2_n/pio29 |

| 30  | a9                  | 64  | gnd                         | 97  | uzi_n/pio26               |

| 31  | a8                  | 65  | pcs1_n/pio17                | 98  | txd1/pio27                |

| 32  | а7                  | 66  | pcs0_n/pio16                | 99  | rxd1/pio28                |

| 33  | a6                  | 67  | V <sub>CC</sub>             | 100 | cts0_n/enrx0_n/pio21      |

| 34  | a5                  |     |                             |     |                           |

### Table 5. IA186ES PQFP Numeric Pin Listing

| Name     | Pin | Name                   | Pin                              | Name                       | Pin |

|----------|-----|------------------------|----------------------------------|----------------------------|-----|

| a0       | 40  | ad14                   | 4 93 pcs2_n/cts1_n/enrx1_n/pio18 |                            | 63  |

| a1       | 39  | ad15                   | 95                               | pcs3_n/rts1_n/rtr1_n/pio19 | 62  |

| a2       | 37  | ale                    | 7                                | pcs5_n/a1/pio3             | 60  |

| a3       | 36  | ardy                   | 8                                | pcs6_n/a2/pio2             | 59  |

| a4       | 35  | bhe_n/aden_n           | 4                                | rd_n                       | 6   |

| а5       | 34  | clkouta                | 16                               | res_n                      | 71  |

| a6       | 33  | clkoutb                | 17                               | rts0_n/rtr0_n/pio20        | 3   |

| а7       | 32  | cts0_n/enrx0_n/pio21   | 100                              | rxd0/pio23                 | 1   |

| a8       | 31  | den_n/ds_n/pio5        | 49                               | rxd1/pio28                 | 99  |

| a9       | 30  | drq0/int5/pio12        | 77                               | s0_n                       | 11  |

| a10      | 29  | drq1/int6/pio13        | 76                               | s1_n                       | 10  |

| a11      | 28  | dt/r_n/pio4            | 48                               | s2_n                       | 9   |

| a12      | 27  | gnd                    | 12                               | s6/lock_n/clkdiv2/pio29    | 96  |

| a13      | 26  | gnd                    | 18                               | srdy/pio6                  | 46  |

| a14      | 25  | gnd                    | 41                               | tmrin0/pio11               | 75  |

| a15      | 24  | gnd                    | 64                               | tmrin1/pio0                | 72  |

| a16      | 23  | gnd                    | 70                               | tmrout0/pio10              | 74  |

| a17/pio7 | 22  | gnd                    | 89                               | tmrout1/pio1               | 73  |

| a18/pio8 | 20  | hlda                   | 44                               | txd0/pio22                 | 2   |

| a19/pio9 | 19  | hold                   | 45                               | txd1/pio27                 | 98  |

| ad0      | 78  | int0                   | 56                               | ucs_n/once1_n              | 57  |

| ad1      | 80  | int1/select_n          | 55                               | uzi_n/pio26                | 97  |

| ad2      | 82  | int2/inta0_n/pwd/pio31 | 54                               | V <sub>CC</sub>            | 15  |

| ad3      | 84  | int3/inta1_n/irq       | 53                               | V <sub>CC</sub>            | 21  |

| ad4      | 86  | int4/pio30             | 52                               | V <sub>CC</sub>            | 38  |

| ad5      | 88  | lcs_n/once0_n          | 58                               | V <sub>CC</sub>            | 61  |

| ad6      | 91  | mcs0_n/pio14           | 50                               | V <sub>CC</sub>            | 67  |

| ad7      | 94  | mcs1_n/pio15           | 51                               | V <sub>CC</sub>            | 92  |

| ad8      | 79  | mcs2_n/pio24           | 68                               | whb_n                      | 42  |

| ad9      | 81  | mcs3_n/rfsh_n/pio25    | 69                               | wlb_n                      | 43  |

| ad10     | 83  | nmi                    | 47                               | wr_n                       | 5   |

| ad11     | 85  | pcs0_n/pio16           | 66                               | x1                         | 13  |

| ad12     | 87  | pcs1_n/pio17           | 65                               | x2                         | 14  |

| ad13     | 90  |                        |                                  |                            |     |

# Table 6. IA186ES PQFP Alphabetic Pin Listing

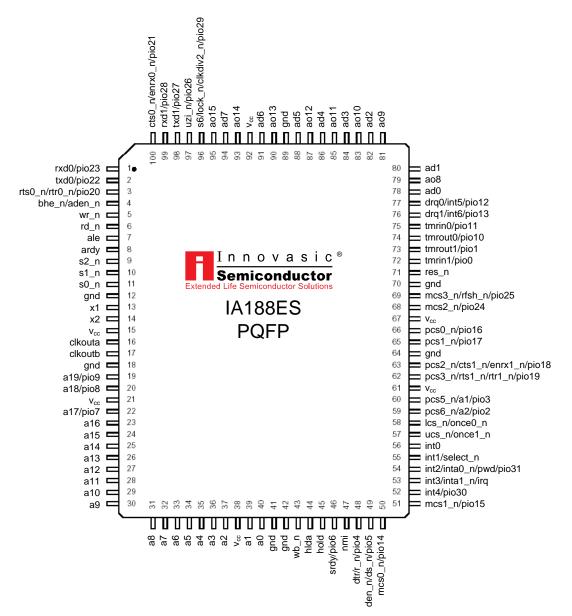

#### 2.1.5 IA188ES PQFP Package

The pinout for the IA188ES PQFP package is as shown in Figure 5. The corresponding pinout is provided in Tables 7 and 8.

#### Figure 5. IA188ES PQFP Package Diagram

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 27 of 154

http://www.innovasic.com Customer Support: 1-888-824-4184

| Pin | Name                | Pin | Name                        | Pin | Name                      |

|-----|---------------------|-----|-----------------------------|-----|---------------------------|

| 1   | rxd0/pio23          | 35  | a4                          | 68  | mcs2_n/pio24              |

| 2   | txd0/pio22          | 36  | а3                          | 69  | mcs3_n/rfsh_n/pio25       |

| 3   | rts0_n/rtr0_n/pio20 | 37  | a2                          | 70  | gnd                       |

| 4   | bhe_n/aden_n        | 38  | v <sub>cc</sub>             | 71  | res_n                     |

| 5   | wr_n                | 39  | a1                          | 72  | tmrin1/pio0               |

| 6   | rd_n                | 40  | a0                          | 73  | tmrout1/pio1              |

| 7   | ale                 | 41  | gnd                         | 74  | tmrout0/pio10             |

| 8   | ardy                | 42  | gnd                         | 75  | tmrin0/pio11              |

| 9   | s2_n                | 43  | wb_n                        | 76  | drq1/int6/pio13           |

| 10  | s1_n                | 44  | hlda                        | 77  | drq0/int5/pio12           |

| 11  | s0_n                | 45  | hold                        | 78  | ad0                       |

| 12  | gnd                 | 46  | srdy/pio6                   | 79  | ao8                       |

| 13  | x1                  | 47  | nmi                         | 80  | ad1                       |

| 14  | x2                  | 48  | dt/r_n/pio4                 | 81  | ao9                       |

| 15  | V <sub>CC</sub>     | 49  | den_n/ds_n/pio5             | 82  | ad2                       |

| 16  | clkouta             | 50  | mcs0_n/pio14                | 83  | ao10                      |

| 17  | clkoutb             | 51  | mcs1_n/pio15                | 84  | ad3                       |

| 18  | gnd                 | 52  | int4/pio30                  | 85  | ao11                      |

| 19  | a19/pio9            | 53  | int3/inta1_n/irq            | 86  | ad4                       |

| 20  | a18/pio8            | 54  | int2/inta0_n/pwd/pio31      | 87  | ao12                      |

| 21  | V <sub>CC</sub>     | 55  | int1/select_n               | 88  | ad5                       |

| 22  | a17/pio7            | 56  | int0                        | 89  | gnd                       |

| 23  | a16                 | 57  | ucs_n/once1_n               | 90  | ao13                      |

| 24  | a15                 | 58  | lcs_n/once0_n               | 91  | ad6                       |

| 25  | a14                 | 59  | pcs6_n/a2/pio2              | 92  | V <sub>CC</sub>           |

| 26  | a13                 | 60  | pcs5_n/a1/pio3              | 93  | ao14                      |

| 27  | a12                 | 61  | V <sub>CC</sub>             | 94  | ad7                       |

| 28  | a11                 | 62  | pcs3_n/rts1_n/rtr1_n/pio19  | 95  | ao15                      |

| 29  | a10                 | 63  | pcs2_n/cts1_n/enrx1_n/pio18 | 96  | s6/lock_n/clkdiv2_n/pio29 |

| 30  | a9                  | 64  | gnd                         | 97  | uzi_n/pio26               |

| 31  | a8                  | 65  | pcs1_n/pio17                | 98  | txd1/pio27                |

| 32  | а7                  | 66  | pcs0_n/pio16                | 99  | rxd1/pio28                |

| 33  | a6                  | 67  | V <sub>CC</sub>             | 100 | cts0_n/enrx0_n/pio21      |

| 34  | a5                  |     |                             |     |                           |

| ·   | •                   |     |                             |     |                           |

### Table 7. IA188ES PQFP Numeric Pin Listing

| Name     | Pin | Name                   | Pin | Name                        | Pin |

|----------|-----|------------------------|-----|-----------------------------|-----|

| a0       | 40  | ao13                   | 90  | pcs2_n/cts1_n/enrx1_n/pio18 | 63  |

| a1       | 39  | ao14                   | 93  | pcs3_n/rts1_n/rtr1_n/pio19  | 62  |

| a2       | 37  | ao15                   | 95  | pcs5_n/a1/pio3              | 60  |

| a3       | 36  | ardy                   | 8   | pcs6_n/a2/pio2              | 59  |

| a4       | 35  | bhe_n/aden_n           | 4   | rd_n                        | 6   |

| а5       | 34  | clkouta                | 16  | res_n                       | 71  |

| a6       | 33  | clkoutb                | 17  | rts0_n/rtr0_n/pio20         | 3   |

| а7       | 32  | cts0_n/enrx0_n/pio21   | 100 | rxd0/pio23                  | 1   |

| a8       | 31  | den_n/ds_n/pio5        | 49  | rxd1/pio28                  | 99  |

| a9       | 30  | drq0/int5/pio12        | 77  | s0_n                        | 11  |

| a10      | 29  | drq1/int6/pio13        | 76  | s1_n                        | 10  |

| a11      | 28  | dt/r_n/pio4            | 48  | s2_n                        | 9   |

| a12      | 27  | gnd                    | 12  | s6/lock_n/clkdiv2/pio29     | 96  |

| a13      | 26  | gnd                    | 18  | srdy/pio6                   | 46  |

| a14      | 25  | gnd                    | 41  | tmrin0/pio11                | 75  |

| a15      | 24  | gnd                    | 42  | tmrin1/pio0                 | 72  |

| a16      | 23  | gnd                    | 64  | tmrout0/pio10               | 74  |

| a17/pio7 | 22  | gnd                    | 70  | tmrout1/pio1                | 73  |

| a18/pio8 | 20  | gnd                    | 89  | txd0/pio22                  | 2   |

| a19/pio9 | 19  | hlda                   | 44  | txd1/pio27                  | 98  |

| ad0      | 78  | hold                   | 45  | ucs_n/once1_n               | 57  |

| ad1      | 80  | int0                   | 56  | uzi_n/pio26                 | 97  |

| ad2      | 82  | int1/select_n          | 55  | V <sub>CC</sub>             | 15  |

| ad3      | 84  | int2/inta0_n/pwd/pio31 | 54  | V <sub>CC</sub>             | 21  |

| ad4      | 86  | int3/inta1_n/irq       | 53  | V <sub>CC</sub>             | 38  |

| ad5      | 88  | lint4/pio30            | 52  | V <sub>CC</sub>             | 61  |

| ad6      | 91  | lcs_n/once0_n          | 58  | V <sub>CC</sub>             | 67  |

| ad7      | 94  | mcs0_n/pio14           | 50  | V <sub>CC</sub>             | 92  |

| ale      | 7   | mcs1_n/pio15           | 51  | wb_n                        | 43  |

| ao8      | 79  | mcs2_n/pio24           | 68  | wr_n                        | 5   |

| ao9      | 81  | mcs3_n/rfsh_n/pio25    | 69  | x1                          | 13  |

| ao10     | 83  | nmi                    | 47  | x2                          | 14  |

| ao11     | 85  | pcs0_n/pio16           | 66  |                             |     |

| ao12     | 87  | pcs1_n/pio17           | 65  |                             |     |

# Table 8. IA188ES PQFP Alphabetic Pin Listing

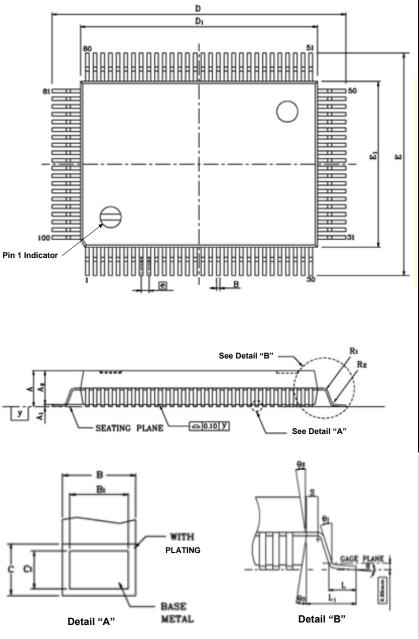

#### 2.1.6 PQFP Physical Dimensions

The physical dimensions for the PQFP are as shown in Figure 6.

| Legend         |       |         |            |                 |       |            |  |

|----------------|-------|---------|------------|-----------------|-------|------------|--|

|                | М     | illimet | er         |                 | Inch  |            |  |

| Symbol         | Min   | Nom     | Max        | Min             | Nom   | Max        |  |

| Α              | -     | -       | 3.40       | _               | -     | 0.134      |  |

| A <sub>1</sub> | 0.25  | I       | I          | 0.010           | Ι     | -          |  |

| A <sub>2</sub> | 2.73  | 2.85    | 2.97       | 0.107           | 0.112 | 0.117      |  |

| В              | 0.25  | 0.30    | 0.38       | 0.010           | 0.012 | 0.015      |  |

| B <sub>1</sub> | 0.22  | 0.30    | 0.33       | 0.009           | 0.012 | 0.013      |  |

| С              | 0.13  | 0.15    | 0.23       | 0.005           | 0.006 | 0.009      |  |

| C <sub>1</sub> | 0.11  | 0.15    | 0.17       | 0.004           | 0.006 | 0.007      |  |

| D              | 23.00 | 23.20   | 23.40      | 0.906           | 0.913 | 0.921      |  |

| D <sub>1</sub> | 19.90 | 20.00   | 20.10      | 0.783           | 0.787 | 0.791      |  |

| E              | 17.00 | 17.20   | 17.40      | 0.669           | 0.677 | 0.685      |  |

| E <sub>1</sub> | 13.90 | 14.00   | 14.10      | 0.547           | 0.551 | 0.555      |  |

| е              | 0.    | 65 BS   | C.         | 0.026 BSC.      |       |            |  |

| L              | 0.73  | 0.88    | 1.03       | 0.0290.0350.041 |       |            |  |

| L <sub>1</sub> | 1.    | 60 BS   | C.         | 0.063 BSC.      |       |            |  |

| R <sub>1</sub> | 0.13  | _       | _          | 0.005           | _     | -          |  |

| R <sub>2</sub> | 0.13  | -       | 0.30       | 0.005           | -     | 0.012      |  |

| S              | 0.20  | I       | I          | 800.0           | I     | -          |  |

| Y              | -     | -       | 0.10       | _               | -     | 0.004      |  |

| θ              | 0°    | _       | <b>7</b> ° | 0°              | _     | <b>7</b> ° |  |

| θ1             | 0°    | -       | _          | 0°              | _     | -          |  |

| θ2             | 9°    | 10°     | 11°        | <b>9</b> °      | 10°   | 11°        |  |

| θ3             | 9°    | 10°     | 11°        | <b>9</b> °      | 10°   | 11°        |  |

| Notes:         |       |         |            | •               |       |            |  |

Notes:

- Dimensions D<sub>1</sub> and E<sub>1</sub> do not include mold protrusion, but mold mismatch is included. Allowable protrusion is 0.25mm/0.010" per side.

- Dimension B does not include Dambar protrusion. Allowable protrusion is 0.08mm/0.003" total in excess of the B dimension at maximum material condition. Dambar cannot be located on the lower radius or the foot.

3. Controlling dimension: millimeter.

#### Figure 6. PQFP Package Dimensions

IA211050902-21 UNCONTROLLED WHEN PRINTED OR COPIED Page 30 of 154

#### 2.2 Pin Descriptions

# 2.2.1 a19/pio9, a18/pio8, a17/pio7, a16–a0—Address Bus (synchronous outputs with tristate)

These pins are the system's source of non-multiplexed I/O or memory addresses and occur a half clkouta cycle before the multiplexed address/data bus (ad15–ad0 for the IA186ES or ao15–ao8 and ad7–ad0 for the IA188ES).

The address bus is tristated during a bus hold or reset.

# 2.2.2 ad15–ad8 (IA186ES)—Address/Data Bus (level-sensitive synchronous inouts with tristate)

These pins are the system's source of time-multiplexed I/O or memory addresses and data. The address function of these pins may be disabled (see bhe\_n/aden\_n pin description). If the address function of these pins is enabled, the address will be present on this bus during  $t_1$  of the bus cycle and data will be present during  $t_2$ ,  $t_3$ , and  $t_4$  of the same bus cycle.

If whb\_n is not active, these pins are tristated during t<sub>2</sub>, t<sub>3</sub>, and t<sub>4</sub> of the bus cycle.

The address/data bus is tristated during a bus hold or reset.

These pins may be used to load the internal Reset Configuration register (RESCON, offset 0F6h) with configuration data during a POR.

# 2.2.3 ao15–ao8 (IA188ES)—Address Bus (level-sensitive synchronous outputs with tristate)

The address bus will contain valid high order address bits during the bus cycle ( $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_4$ ) if the bus is enabled by the AD bit in the Upper and Lower Memory Chip Select registers (UMCS, offset 0a0h, and LMCS, offset 0a2h).

These pins are combined with ad7–ad0 to complete the multiplexed address bus and are tristated during a bus hold or reset condition.

#### 2.2.4 ad7-ad0—Address/Data Bus (level-sensitive synchronous inouts with tristate)

These pins are the system's source of time-multiplexed low order byte of the addresses for I/O or memory and 8-bit data. The low order address byte will be present on this bus during  $t_1$  of the bus cycle and the 8-bit data will be present during  $t_2$ ,  $t_3$ , and  $t_4$  of the same bus cycle.

The address function of these pins may be disabled (see bhe\_n/aden\_n pin description).

If wlb\_n is not active, these pins are tristated during  $t_2$ ,  $t_3$ , and  $t_4$  of the bus cycle. The address/data bus is tristated during a bus hold or reset.

#### 2.2.5 ale—Address Latch Enable (synchronous output)

This signal indicates the presence of an address on the address bus (ad15–ad0 for the IA186ES or ao15–ao8 and ad7–ad0 for the IA188ES), which is guaranteed to be valid on the falling edge of ale.

In ONCE mode, this pin is tristated but not during bus hold or reset.

#### 2.2.6 ardy—Asynchronous Ready (level-sensitive asynchronous input)

This asynchronous signal provides an indication to the microcontroller that the addressed I/O device or memory space will complete a data transfer. This active high signal is asynchronous with respect to clkouta. If the falling edge of ardy is not synchronized to clkouta, an additional clock cycle may be added. The ardy or srdy must be synchronized to clkouta to guarantee the number of inserted wait states.

The ardy should be tied high to maintain a permanent assertion of the ready condition. On the other hand, if the ardy signal is not used by the system, it should be tied low, which passes control to the srdy signal.

# 2.2.7 bhe\_n/aden\_n (IA186ES only)—Bus High Enable (synchronous output with tristate)/Address Enable (input with internal pullup)

The bhe\_n-bhe\_n and address bit ad0 or a0 inform the system which bytes of the data bus (upper, lower, or both) are involved in the current memory access bus cycle, as shown in Table 9.

#### Table 9. Bus Cycle Types for bhe\_n and ad0

| bhe_n | ad0 | Type of Bus Cycle                |

|-------|-----|----------------------------------|

| 0     | 0   | Word Transfer                    |

| 0     | 1   | High Byte Transfer (Bits [15–8]) |

| 1     | 0   | Low Byte Transfer (Bits [7–0])   |

| 1     | 1   | Refresh                          |