# ST10R272L

# 16-BIT LOW VOLTAGE ROMLESS MCU WITH MAC

#### DATASHEET

- High Performance 16-bit CPU

- CPU Frequency: 0 to 50 MHz

- 40ns instruction cycle time at 50-MHz CPU clock

- Multiply-Accumulate unit (MAC)

- 4-stage pipeline

- Register-based design with multiple variable register banks

- Enhanced boolean bit manipulation facilities

- Additional instructions to support HLL and operating systems

- Single-cycle context switching support

- 1024 bytes on-Chip special function register area

- Memory Organisation

- 1KByte on-chip RAM

- Up to 16 MBytes linear address space for code and data (1 MByte with SSP used)

- External Memory Interface

- Programmable external bus characteristics for different address ranges

- 8-bit or 16-bit external data bus

- Multiplexed or demultiplexed external address/data buses

- Five programmable chip-select signals

- Hold and hold-acknowledge bus arbitration support

- One Channel PWM Unit

- Fail Safe Protection

- Programmable watchdog timer

- Oscillator Watchdog

- Interrupt

- 8-channel interrupt-driven single-cycle data transfer facilities via peripheral event controller (PEC)

- 16-priority-level interrupt system with 17 sources, sample-rate down to 40 ns

#### Timers

- Two multi-functional general purpose timer units with 5 timers

- Clock Generation via on-chip PLL, or via direct or prescaled clock input

- Serial Channels

- Synchronous/asynchronous

- High-speed-synchronous serial port SSP

- Up to 77 general purpose I/O lines

- No bootstrap loader

- Electrical Characteristics

- 5V Tolerant I/Os

- 5V Fail-Safe Inputs (Port 5)

- Power: 3.3 Volt +/-0.3V

- Idle and power down modes

- Support

- C-compilers, macro-assembler packages, emulators, evaluation boards, HLLdebuggers, simulators, logic analyser disassemblers, programming boards

- Package

- 100-Pin Thin Quad Flat Pack (TQFP)

Rev. 1.3

## Table of Contents

| 1 PIN DESCRIPTION                | 4  |

|----------------------------------|----|

| 2 FUNCTIONAL DESCRIPTION         | 11 |

| 3 MEMORY MAPPING                 | 12 |

| 4 CENTRAL PROCESSING UNIT        | 13 |

| 5 MULTIPLY-ACCUMULATE UNIT (MAC) | 14 |

| 5.1 MAC FEATURES                 | 15 |

| 5.2 MAC OPERATION                | 16 |

| 6 INTERRUPT AND TRAP FUNCTIONS   | 22 |

| 6.1 INTERRUPT SOURCES            | 23 |

| 6.2 HARDWARE TRAPS               | 24 |

| 7 PARALLEL PORTS                 | 25 |

| 8 EXTERNAL BUS CONTROLLER        | 25 |

| 9 PWM MODULE                     | 26 |

| 10 GENERAL PURPOSE TIMERS        | 27 |

| 10.1 GPT1                        | 27 |

| 10.2 GPT2                        | 29 |

| 11 SERIAL CHANNELS               | 30 |

| 12 WATCHDOG TIMER                | 32 |

| 13 SYSTEM RESET                  | 33 |

| 14 POWER REDUCTION MODES         | 34 |

| 15 SPECIAL FUNCTION REGISTERS    | 34 |

| 16 ELECTRICAL CHARACTERISTICS    | 40 |

| 16.1 ABSOLUTE MAXIMUM RATINGS    | 40 |

| 16.2 DC CHARACTERISTICS          | 42 |

# Table of Contents

| 16.3 AC CHARACTERISTICS                |

|----------------------------------------|

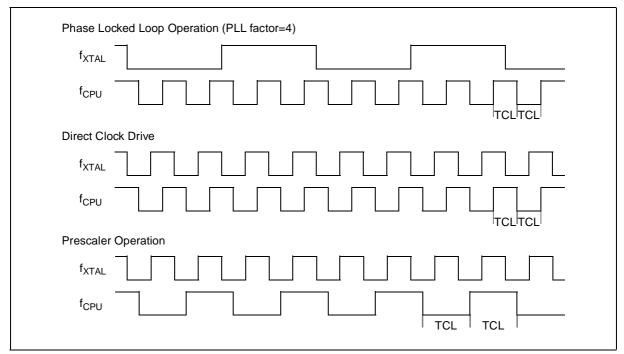

| 16.3.1 CPU Clock Generation Mechanisms |

| 16.3.2 Memory Cycle Variables 51       |

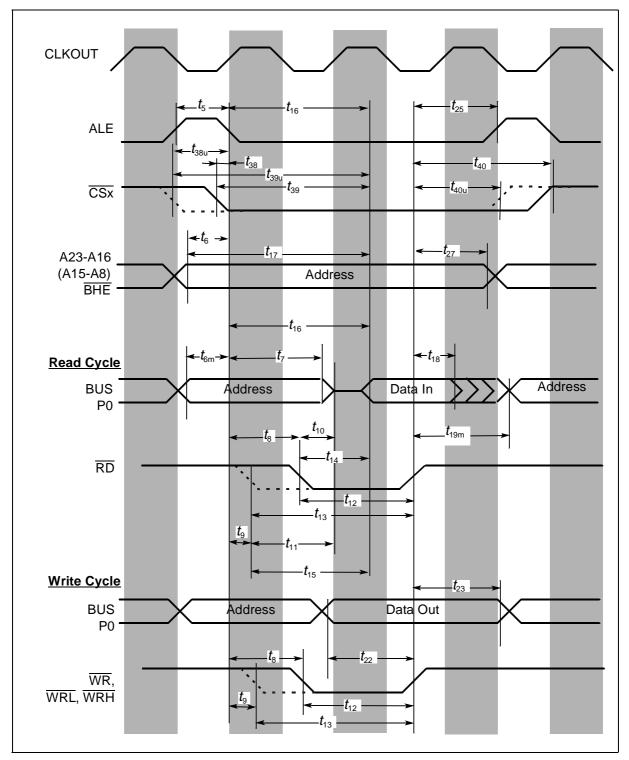

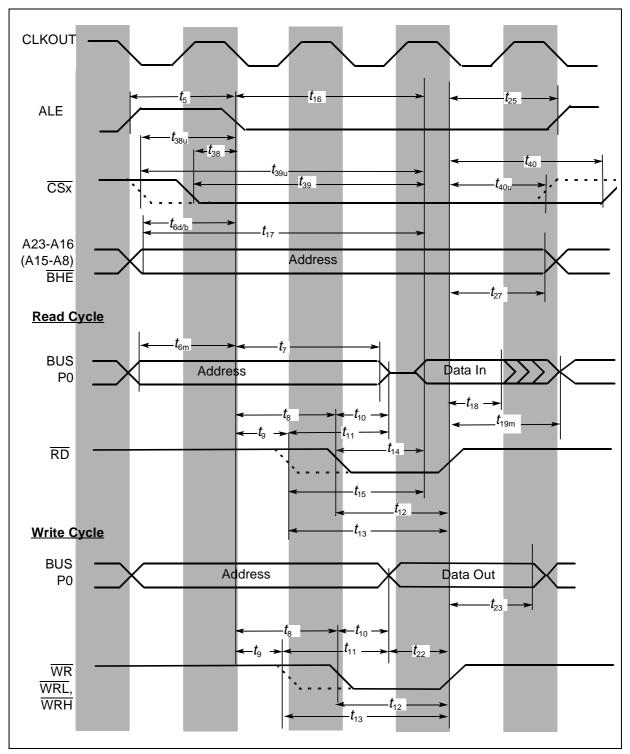

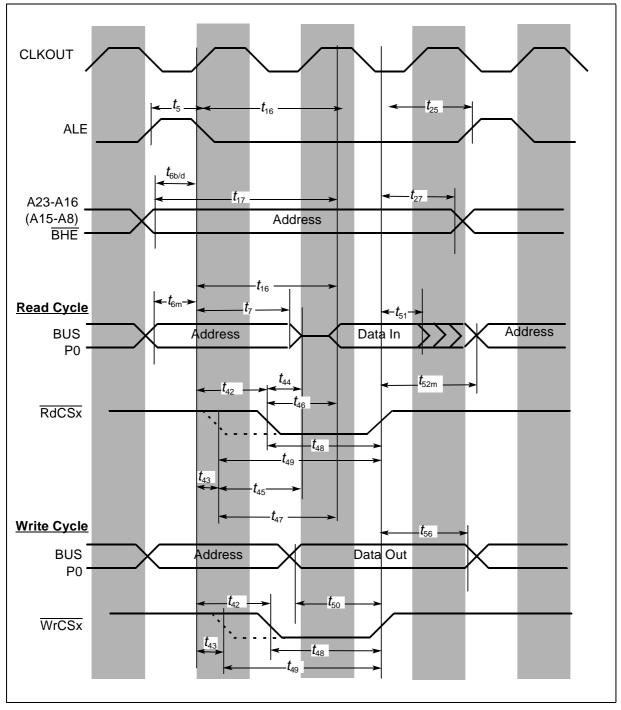

| 16.3.3 Multiplexed Bus                 |

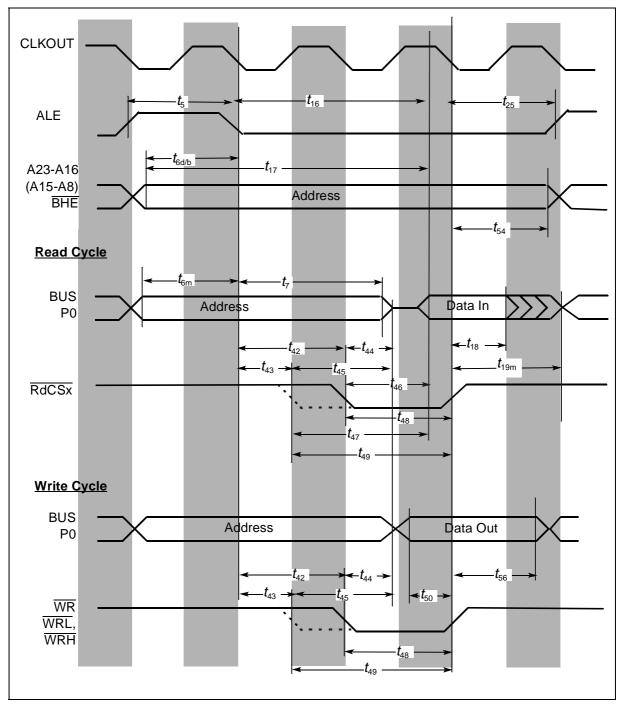

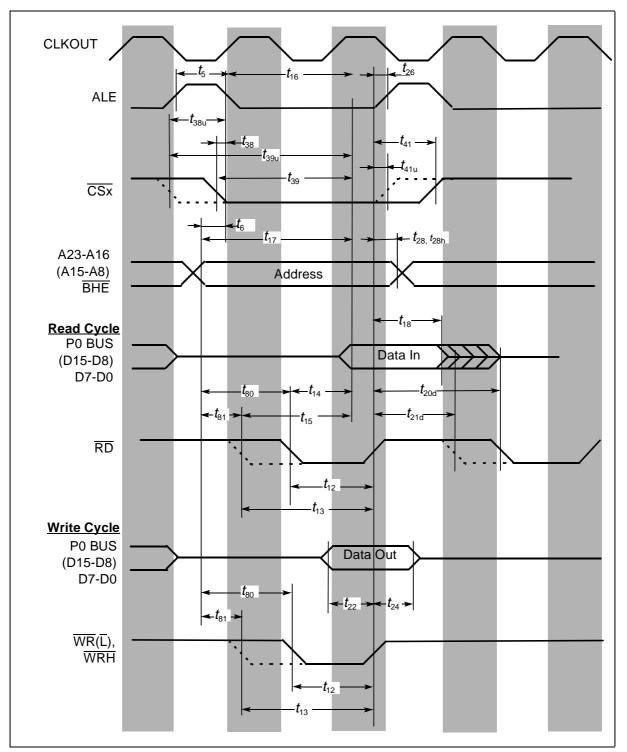

| 16.3.4 Demultiplexed Bus 59            |

| 16.3.5 CLKOUT and READY/READY          |

| 16.3.6 External Bus Arbitration        |

| 16.3.7 External Hardware Reset 72      |

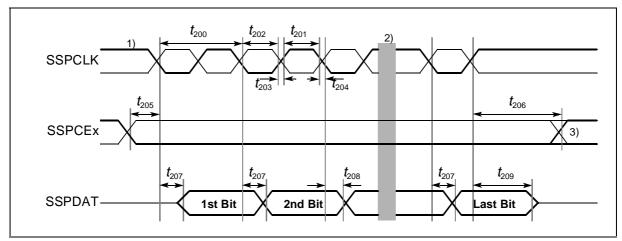

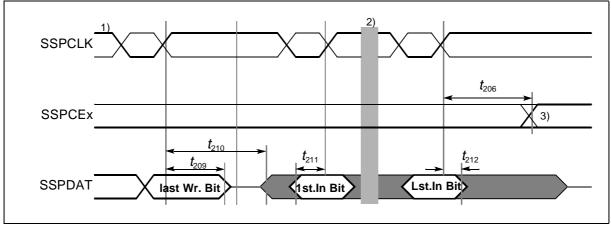

| 16.3.8 Synchronous Serial Port Timing  |

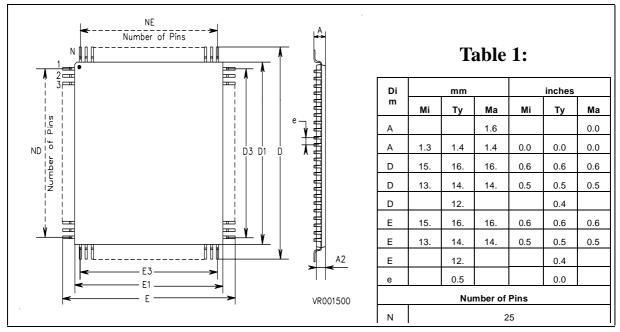

| 17 PACKAGE MECHANICAL DATA             |

| 18 ORDERING INFORMATION                |

# PZ DESCRIPTION

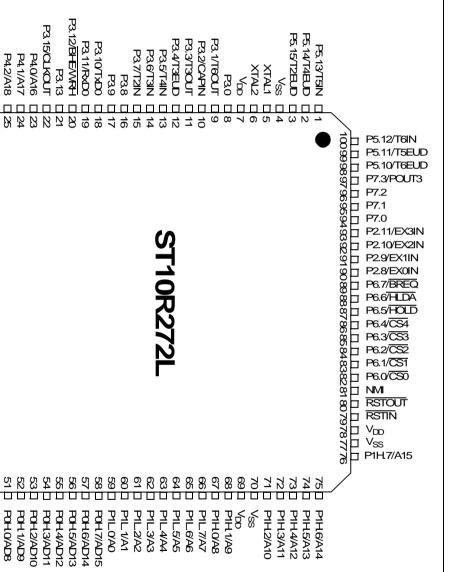

Figure **\_** TQFP-100 pin configuration (top view) P4.1/A17 P4.2/A18

P4.3/A19 08 V<sub>SS</sub> 08 V<sub>DD</sub> 08 P4.4/A20/SSPCE108

P4.4/A20/SSPCE1U 8 P4.5/A21/SSPCE0 08 P4.6/A22/SSPDAT 09 P4.7/A23/SSPCLK 08 RD 08 WR/WRL 08 READY/READY 08 ALE 08 EA 09

EA 137 V<sub>DD</sub> 138 V<sub>SS</sub> 1040 POL 0/AD0 1142 POL 1/AD1 1142 POL 1/AD1 1142 POL 2/AD2 1143 POL 2/AD2 1145 POL 3/AD3 11445 POL 3/AD3 1146 POL 3/AD5 1148 POL 5/AD5 1148 POL 6/AD6 1148 POL 6/AD6 1148 POL 7/AD7 115 V<sub>DD</sub> 115 V<sub>SS</sub> 115 V<sub>DD</sub> 115 V<sub>SS</sub> 115 V<sub>DD</sub> 11

4/77

| Symbol | Pin Number<br>(TQFP) | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                                                                                                                                                                                          |                                                                       |                                         |  |

|--------|----------------------|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------|--|

| P5.10  | 98-100               | I                       | 5S                 | 6-bit input-only port with Schmitt-Trigger characteristics.                                                                                                                                       |                                                                       |                                         |  |

| –P5.15 | 1- 3                 | I                       | 5S                 | Port 5 pins also serve as timer inputs:                                                                                                                                                           |                                                                       |                                         |  |

|        | 98                   | I                       | 5S                 | P5.10                                                                                                                                                                                             | T6EUD                                                                 | GPT2 Timer T6 Ext.Up/Down<br>Ctrl.Input |  |

|        | 99                   | I                       | 5S                 | P5.11                                                                                                                                                                                             | T5EUD                                                                 | GPT2 Timer T5 Ext.Up/Down<br>Ctrl.Input |  |

|        | 100                  | I                       | 5S                 | P5.12                                                                                                                                                                                             | T6IN                                                                  | GPT2 Timer T6 Count Input               |  |

|        | 1                    | I                       | 5S                 | P5.13                                                                                                                                                                                             | T5IN                                                                  | GPT2 Timer T5 Count Input               |  |

|        | 2                    | I                       | 5S                 | P5.14                                                                                                                                                                                             | T4EUD                                                                 | GPT1 Timer T4 Ext.Up/Down<br>Ctrl.Input |  |

|        | 3                    | I                       | 5S                 | P5.15                                                                                                                                                                                             | T2EUD                                                                 | GPT1 Timer T2 Ext.Up/Down<br>Ctrl.Input |  |

| XTAL1  | 5                    | I                       | 3Т                 | XTAL1:                                                                                                                                                                                            | (TAL1: Input to the oscillator amplifier and internal clock generator |                                         |  |

| XTAL2  | 6                    | 0                       | ЗТ                 | XTAL2:                                                                                                                                                                                            | Output of t                                                           | he oscillator amplifier circuit.        |  |

|        |                      |                         |                    | To clock the device from an external source, drive<br>XTAL1, while leaving XTAL2 unconnected.<br>Observe minimum and maximum high/low and<br>rise/fall times specified in the AC Characteristics. |                                                                       |                                         |  |

Table 1 Pin definitions

#### ST10R272L - PIN DESCRIPTION

| Symbol                   | Pin Number<br>(TQFP) | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                              |                                                                    |                                                                                                                                                                                                                      |

|--------------------------|----------------------|-------------------------|--------------------|---------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0 –<br>P3.13<br>P3.15 | 8-21<br>22           | I/O<br>I/O              | 5T<br>5T           | wise progr<br>pin configr<br>impedanc | rammable for<br>ured as input<br>e state. Port :<br>en drain drive | ing) bidirectional I/O port. Port 3 is bit-<br>input or output via direction bits. For a<br>t, the output driver is put into high-<br>3 outputs can be configured as push/<br>ers. The following pins have alternate |

|                          | 9                    | 0                       | 5T                 | P3.1                                  | T6OUT                                                              | GPT2 Timer T6 toggle latch output                                                                                                                                                                                    |

|                          | 10                   | I                       | 5T                 | P3.2                                  | CAPIN                                                              | GPT2 Register CAPREL capture input                                                                                                                                                                                   |

|                          | 11                   | 0                       | 5T                 | P3.3                                  | T3OUT                                                              | GPT1 Timer T3 toggle latch output                                                                                                                                                                                    |

|                          | 12                   | I                       | 5T                 | P3.4                                  | T3EUD                                                              | GPT1 Timer T3 ext.up/down ctrl.input                                                                                                                                                                                 |

|                          | 13                   | I                       | 5T                 | P3.5                                  | T4IN                                                               | GPT1 Timer T4 input for count/gate/<br>reload/capture                                                                                                                                                                |

|                          | 14                   | I                       | 5T                 | P3.6                                  | T3IN                                                               | GPT1 Timer T3 count/gate input                                                                                                                                                                                       |

|                          | 15                   | I                       | 5T                 | P3.7                                  | T2IN                                                               | GPT1 Timer T2 input for count/gate/<br>reload/capture                                                                                                                                                                |

|                          | 18                   | 0                       | 5T                 | P3.10                                 | TxD0                                                               | ASC0 clock/data output (asyn./syn.)                                                                                                                                                                                  |

|                          | 19                   | I/O                     | 5T                 | P3.11                                 | RxD0                                                               | ASC0 data input (asyn.) or I/O (syn.)                                                                                                                                                                                |

|                          | 20                   | 0                       | 5T                 | P3.12                                 | BHE                                                                | Ext. Memory High Byte Enable Signal                                                                                                                                                                                  |

|                          |                      | 0                       | 5T                 |                                       | WRH                                                                | Ext. Memory High Byte Write Strobe                                                                                                                                                                                   |

|                          | 22                   | 0                       | 5T                 | P3.15                                 | CLKOUT                                                             | System clock output (=CPU clock)                                                                                                                                                                                     |

Table 1 Pin definitions

| Symbol          | Pin Number<br>(TQFP) | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                               |             |                                                            |

|-----------------|----------------------|-------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|

| P4.0–<br>P4.7   | 23-26<br>29-32-      | I/O                     | 5T                 | An 8-bit bidirectional I/O port. Port 8 is bit-wise programmable<br>for input or output via direction bits. For a pin configured as<br>input, the output driver is put into high-impedance state.<br>Port 4 can be used to output the segment address lines for<br>external bus configuration.                                                                         |             |                                                            |

|                 | 23                   | 0                       | 5T                 | P4.0                                                                                                                                                                                                                                                                                                                                                                   | A16         | Least Significant Segment Addr. Line                       |

|                 |                      |                         |                    |                                                                                                                                                                                                                                                                                                                                                                        |             |                                                            |

|                 | 26                   | 0                       | 5T                 | P4.3                                                                                                                                                                                                                                                                                                                                                                   | A19         | Segment Address Line                                       |

|                 | 29                   | 0                       | 5T                 | P4.4                                                                                                                                                                                                                                                                                                                                                                   | A20         | Segment Address Line                                       |

|                 |                      | 0                       | 5T                 |                                                                                                                                                                                                                                                                                                                                                                        | SSPCE1      | Chip Enable Line 1                                         |

|                 | 30                   | 0                       | 5T                 | P4.5                                                                                                                                                                                                                                                                                                                                                                   | A21         | Segment Address Line                                       |

|                 |                      | 0                       | 5T                 |                                                                                                                                                                                                                                                                                                                                                                        | SSPCE0      | SSPChip Enable Line 0                                      |

|                 | 31                   | 0                       | 5T                 | P4.6 A22 Segment Address Line                                                                                                                                                                                                                                                                                                                                          |             |                                                            |

|                 |                      | I/O                     | 5T                 |                                                                                                                                                                                                                                                                                                                                                                        | SSPDAT      | SSP Data Input/Output Line                                 |

|                 | 32                   | 0                       | 5T                 | P4.7                                                                                                                                                                                                                                                                                                                                                                   | A23         | Most Significant Segment Addr. Line                        |

|                 |                      | 0                       | 5T                 |                                                                                                                                                                                                                                                                                                                                                                        | SSPCLK      | SSP Clock Output Line                                      |

| RD              | 33                   | 0                       | 5T                 |                                                                                                                                                                                                                                                                                                                                                                        | femory Read | d Strobe. RD is activated for every exter-<br>read access. |

| WR/<br>WRL      | 34                   | 0                       | 5T                 | External Memory Write Strobe. In WR-mode, this pin is activated for every external data write access. In WRL-mode, this pin is activated for low byte data write accesses on a 16-bit bus, and for every data write access on an 8-bit bus. See WRCFG in the SYSCON register for mode selection.                                                                       |             |                                                            |

| READY/<br>READY | 35                   | I                       | 5T                 | See WRCFG in the SYSCON register for mode selection.<br>Ready Input. Active level is programmable. When the Ready<br>function is enabled, the selected inactive level at this pin dur-<br>ing an external memory access will force the insertion of mem-<br>ory cycle time waitstates until the pin returns to the selected<br>active level. Polarity is programmable. |             |                                                            |

Table 1 Pin definitions

#### ST10R272L - PIN DESCRIPTION

| Symbol                                         | Pin Number<br>(TQFP)      | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|---------------------------|-------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                                            | 36                        | 0                       | 5T                 | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ĒĀ                                             | 37                        | I                       | 5T                 | External Access Enable pin. Low level at this pin during and after reset forces the ST10R272L to begin instruction execution out of external memory. A high level forces execution out of the internal ROM. The ST10R272L must have this pin tied to '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PORT0:<br>P0L.0–<br>P0L.7,<br>P0H.0 -<br>P0H.7 | 41 - 48<br>51 - 58        | I/O                     | 5T                 | PORT0 has two 8-bit bidirectional I/O ports P0L and P0H. It is<br>bit-wise programmable for input or output via direction bits. For<br>a pin configured as input, the output driver is put into high-<br>impedance state.For external bus configuration, PORT0 acts as address (A)<br>and address/data (AD) bus in multiplexed bus modes and as<br>the data (D) bus in demultiplexed bus modes.Demultiplexed bus modesDemultiplexed bus modesData Path Width: 8-bit16-bitP0H.0 – P0H.7:I/OD8 - D15Multiplexed bus modesData Path Width: 8-bit16-bitP0H.0 – P0H.7:I/OD8 - D15Multiplexed bus modesData Path Width: 8-bit16-bitP0H.0 – P0H.7:I/OD8 - D15POL.0 – P0L.7:AD0 – AD7AD0 – AD7AD0 – AD7AD0 – AD7AD8 – AD15 |

| PORT1:<br>P1L.0–<br>P1L.7,<br>P1H.0 -<br>P1H.7 | 59- 66<br>67, 68<br>71-76 | I/O                     | 5T                 | PORT1 has two 8-bit bidirectional I/O ports P1L and P1H. It is<br>bit-wise programmable for input or output via direction bits. For<br>a pin configured as input, the output driver is put into high-<br>impedance state. PORT1 acts as a 16-bit address bus (A) in<br>demultiplexed bus modes and also after switching from a<br>demultiplexed bus mode to a multiplexed bus mode.                                                                                                                                                                                                                                                                                                                                |

Table 1 Pin definitions

| Symbol        | Pin Number<br>(TQFP) | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                       |

|---------------|----------------------|-------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|

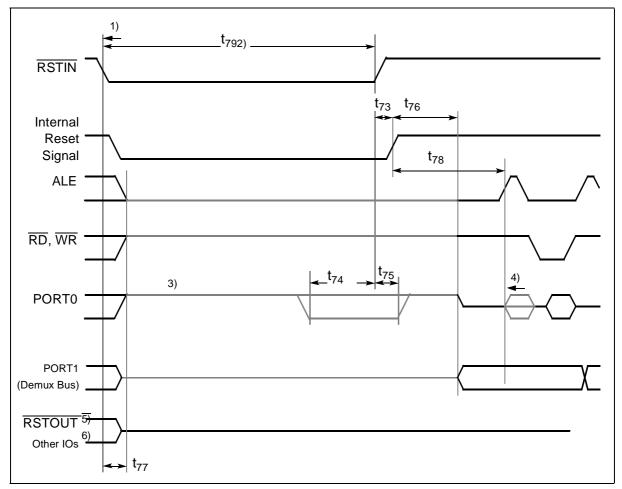

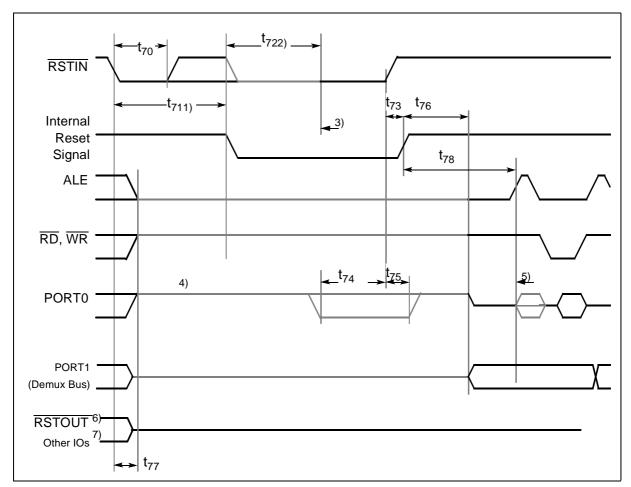

| RSTIN         | 79                   | I                       | 5T                 | Reset Input with Schmitt-Trigger characteristics. Resets the device when a low level is applied for a specified duration while the oscillator is running. An internal pullup resistor enables power-on reset using only a capacitor connected to $V_{SS}$ . With a bonding option, the $\overline{\text{RSTIN}}$ pin can also be pulled-down for 512 internal clock cycles for hardware, software or watchdog timer triggered resets |      |                                                                       |

| RSTOUT        | 80                   | 0                       | 5T                 | Internal Reset Indication Output. This pin is set to a low level<br>when the part is executes hardware-, software- or watchdog<br>timer reset. RSTOUT remains low until the EINIT (end of ini-<br>tialization) instruction is executed.                                                                                                                                                                                              |      |                                                                       |

| NMI           | 81                   | I                       | 5S                 | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. If it is not used, NMI should be pulled high externally.                                                                                                                                                                                                                                                        |      |                                                                       |

| P6.0-<br>P6.7 | 82-89                | I/O                     | 5T                 | An 8-bit bidirectional I/O port. Port 6 is bit-wise programmable<br>for input or output via direction bits. For a pin configured as<br>input, the output driver is put into high-impedance state. Port 6<br>outputs can be configured as push/pull or open drain drivers.<br>The following Port 6 pins have alternate functions:                                                                                                     |      |                                                                       |

|               | 82                   | 0                       | 5T                 | P6.0                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS0  | Chip Select 0 Output                                                  |

|               |                      |                         |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                                       |

|               | 86                   | 0                       | 5T                 | P6.4                                                                                                                                                                                                                                                                                                                                                                                                                                 | CS4  | Chip Select 4 Output                                                  |

|               | 87                   | I                       | 5T                 | P6.5                                                                                                                                                                                                                                                                                                                                                                                                                                 | HOLD | External Master Hold Request Input<br>(Master mode: O, Slave mode: I) |

|               | 88                   | I/O                     | 5T                 | P6.6                                                                                                                                                                                                                                                                                                                                                                                                                                 | HLDA | Hold Acknowledge Output                                               |

|               | 89                   | 0                       | 5T                 | P6.7                                                                                                                                                                                                                                                                                                                                                                                                                                 | BREQ | Bus Request Output                                                    |

Table 1 Pin definitions

\_\_\_\_\_

#### ST10R272L - PIN DESCRIPTION

| Symbol          | Pin Number<br>(TQFP)        | Input (I)<br>Output (O) | Kind <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                                                               |

|-----------------|-----------------------------|-------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.8 –<br>P2.11 | 90 - 93                     | I/O                     | 5T                 | Port 2 is a 4-bit bidirectional I/O port. It is bit-wise programma-<br>ble for input or output via direction bits. For a pin configured as<br>input, the output driver is put into high-impedance state. Port 2<br>outputs can be configured as push/pull or open drain drivers.                                                       |

|                 |                             |                         |                    | The following Port 2 pins have alternate functions:                                                                                                                                                                                                                                                                                    |

|                 | 90                          | I                       | 5T                 | P2.8 EX0IN Fast External Interrupt 0 Input                                                                                                                                                                                                                                                                                             |

|                 |                             |                         |                    |                                                                                                                                                                                                                                                                                                                                        |

|                 | 93                          | I                       | 5T                 | P2.11 EX3IN Fast External Interrupt 3 Input                                                                                                                                                                                                                                                                                            |

| P7.0 –<br>P7.3  | 94 - 97                     | I/O                     | 5T                 | Port 7 is a 4-bit bidirectional I/O port. It is bit-wise programma-<br>ble for input or output via direction bits. For a pin configured as<br>input, the output driver is put into high-impedance state. Port<br>7outputs can be configured as push/pull or open drain drivers.<br>The following Port 7 pins have alternate functions: |

|                 | 97                          | 0                       | 5T                 | P7.3 POUT3 PWM (Channel 3) Output                                                                                                                                                                                                                                                                                                      |

| RPD             | 40                          | I/O                     | 5T                 | Input timing pin for the return from powerdown circuit and power-up asynchronous reset.                                                                                                                                                                                                                                                |

| V <sub>DD</sub> | 7, 28,<br>38, 49,<br>69, 78 | -                       | PO                 | Digital supply voltage.                                                                                                                                                                                                                                                                                                                |

| V <sub>SS</sub> | 4, 27,<br>39, 50,<br>70, 77 | -                       | PO                 | Digital ground.                                                                                                                                                                                                                                                                                                                        |

#### Table 1 Pin definitions

1) The following I/O kinds are used. Refer to *ELECTRICAL CHARACTERISTICS* on page 40 for a detailed description.

PO: Power pin

- 3T: 3 V tolerant pin (voltage max. respect to Vss is -0.5 to VDD + 0.5)

- 5V: 5 V tolerant pin (voltage max. respect to Vss is -0.5 to 5.5 only if chip is powered)

5S: 5 V tolerant and fail-safe pin (-0.5-5.5 max. voltage w.r.t. Vss even if chip is not powered).

#### 2 FUNCTIONAL DESCRIPTION

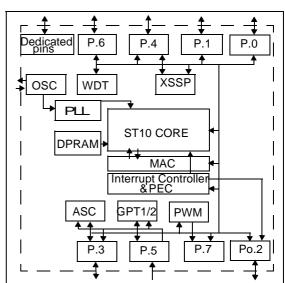

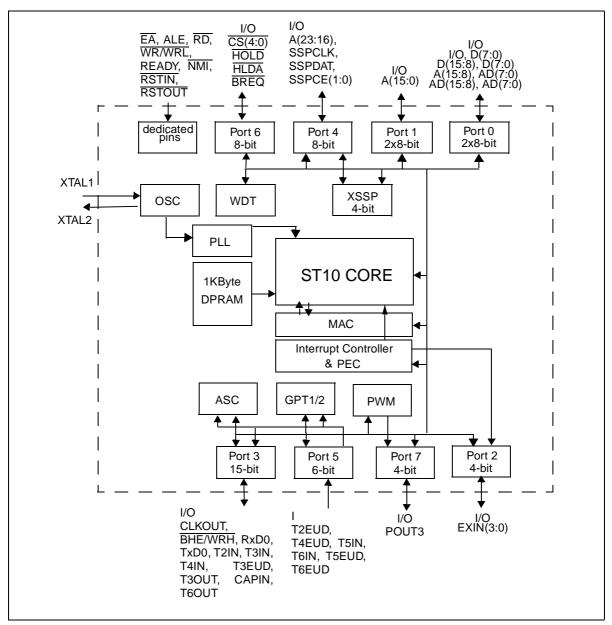

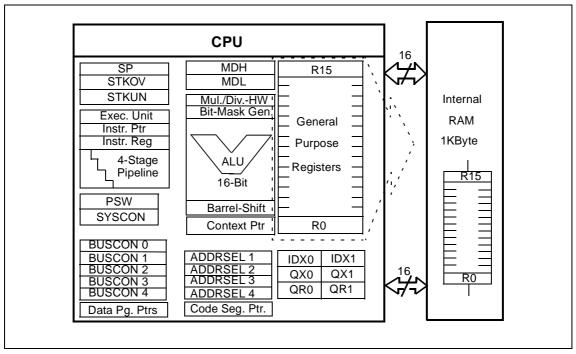

ST10R272L architecture combines the advantages of both RISC and CISC processors with an advanced peripheral subsystem. The following block diagram overviews the different onchip components and the internal bus structure.

Figure 2 Block diagram

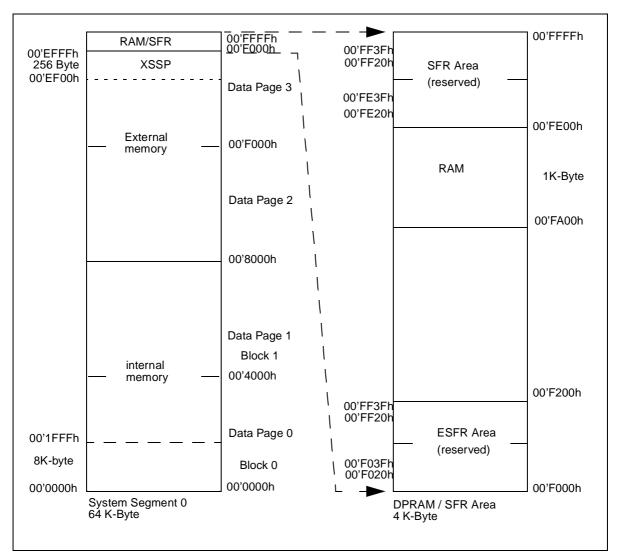

#### ST10R272L - MEMORY MAPPING

#### 3 MEMORY MAPPING

The ST10R272L is a ROMless device, the internal RAM space is 1 KByte. The RAM address space is used for variables, register banks, the system stack, the PEC pointers (in 00'FCE0h - 00'FCFFh) and the bit-addressable space (in 00'FD00h - 00'FDFFh).

Figure 3 Memory map

#### 4 CENTRAL PROCESSING UNIT

The main core of the CPU contains a 4-stage instruction pipeline, a MAC multiplyaccumulation unit, a separate multiply and divide unit, a bit-mask generator and a barrel shifter. Most instructions can be executed in one machine cycle requiring 40ns at 50MHz CPU clock.

The CPU includes an actual register context consisting of 16 wordwide GPRs physically located in the on-chip RAM area. A Context Pointer (CP) register determines the base address of the active register bank to be accessed by the CPU. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, one register bank may overlap others.

A system stack of up to 1024 bytes is provided as a storage for temporary data. The system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are compared against the stack pointer value during each stack access to detect stack overflow or underflow.

Figure 4 CPU block diagram

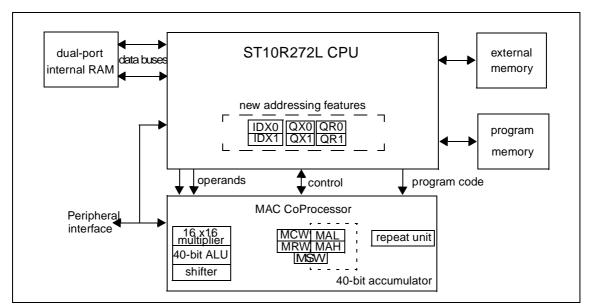

#### 5 MULTIPLY-ACCUMULATE UNIT (MAC)

The MAC is a specialized co-processor added to the ST10R272L CPU core to improve the performance of signal processing algorithms. It includes:

- a multiply-accumulate unit

- an address generation unit, able to feed the mac unit with 2 operands per cycle

- a repeat unit, to execute a series of multiply-accumulate instructions

New addressing capabilities enable the CPU to supply the MAC with up to 2 operands per instruction cycle. MAC instructions: multiply, multiply-accumulate, 32-bit signed arithmetic operations and the CoMOV transfer instruction have been added to the standard instruction set. Full details are provided in the 'ST10 Family Programming Manual'.

Figure 5 MAC architecture

#### 5.1 MAC Features

#### Enhanced addressing capabilities

- Double indirect addressing mode with pointer post-modification.

- Parallel Data Move allows one operand move during Multiply-Accumulate instructions without penalty.

- CoSTORE instruction (for fast access to the MAC SFRs) and CoMOV (for fast memory to memory table transfer).

#### General

- Two-cycle execution for all MAC operations.

- 16 x 16 signed/unsigned parallel multiplier.

- 40-bit signed arithmetic unit with automatic saturation mode.

- 40-bit accumulator.

- 8-bit left/right shifter.

- Scaler (one-bit left shifter)

- Data limiter

- Full instruction set with multiply and multiply-accumulate, 32-bit signed arithmetic and compare instructions.

- Three 16-bit status and control registers: MSW: MAC Status Word, MCW: MAC Control Word, MRW: MAC Repeat Word.

#### **Program control**

- Repeat Unit allows some MAC co-processor instructions to be repeated up to 8192 times. Repeated instructions may be interrupted.

- MAC interrupt (Class B Trap) on MAC condition flags.

57

#### 5.2 MAC Operation

#### Instruction pipelining

All MAC instructions use the 4-stage pipeline. During each stage the following tasks are performed:

- FETCH: All new instructions are double-word instructions.

- DECODE: If required, operand addresses are calculated and the resulting operands are fetched. IDX and GPR pointers are post-modified if necessary.

- EXECUTE: Performs the MAC operation. At the end of the cycle, the Accumulator and the MAC condition flags are updated if required. Modified GPR pointers are written-back during this stage, if required.

- WRITEBACK: Operand write-back in the case of parallel data move.

- Note At least one instruction which does not use the MAC must be inserted between two instructions that read from a MAC register. This is because the Accumulator and the status of the MAC are modified during the Execute stage. The CoSTORE instruction has been added to allow access to the MAC registers immediately after a MAC operation.

#### Address generation

MAC instructions can use some standard ST10 addressing modes such as GPR direct or #data4 for immediate shift value.

New addressing modes have been added to supply the MAC with two new operands per instruction cycle. These allow indirect addressing with address pointer post-modification.

Double indirect addressing requires two pointers. Any GPR can be used for one pointer, the other pointer is provided by one of two specific SFRs IDX0 and IDX1. Two pairs of offset registers QR0/QR1 and QX0/QX1 are associated with each pointer (GPR or IDX<sub>i</sub>). The GPR pointer allows access to the entire memory space, but IDX<sub>i</sub> are limited to the internal Dual-Port RAM, except for the CoMOV instruction.

The following table shows the various combinations of pointer post-modification for each of these 2 new addressing modes. In this document the symbols " $[Rw_n \otimes]$ " and " $[IDX_i \otimes]$ " refer to these addressing modes.

| Symbol                                     | Mnemonic                              | Address Pointer Operation                                             |

|--------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|

| "[IDX <sub>i</sub> $\otimes$ ]" stands for | [IDX <sub>i</sub> ]                   | $(IDX_j) \gets (IDX_j) \text{ (no-op)}$                               |

|                                            | [IDX <sub>i</sub> +]                  | $(IDX_{j}) \gets (IDX_{j}) + 2 \text{ (i=0,1)}$                       |

|                                            | [IDX <sub>i</sub> -]                  | $(IDX_j) \gets (IDX_j) \text{ -2 } (i\text{=}0,1)$                    |

|                                            | [IDX <sub>j</sub> + QX <sub>j</sub> ] | $(IDX_j) \gets (IDX_j) + (QX_j) \ (i, j = 0, 1)$                      |

|                                            | [IDX <sub>i</sub> - QX <sub>j</sub> ] | $(IDX_j) \gets (IDX_j) \text{ - } (QX_j) \text{ (i, j =0,1)}$         |

| "[Rw <sub>n</sub> ⊗]" stands for           | [Rwn]                                 | $(Rwn) \leftarrow (Rwn) (no-op)$                                      |

|                                            | [Rwn+]                                | (Rwn) ← (Rwn) +2 (n=0-15)                                             |

|                                            | [Rwn-]                                | (Rwn) ← (Rwn) -2 (k=0-15)                                             |

|                                            | [Rwn+QR <sub>j</sub> ]                | $(Rwn) \leftarrow (Rwn) + (QR_j) (n=0-15; j=0,1)$                     |

|                                            | [Rwn - QR <sub>j</sub> ]              | $(Rwn) \leftarrow (Rwn) \text{ - } (QR_j) \text{ (n=0-15; } j = 0,1)$ |

Table 2 Pointer post-modification combinations for IDXi and Rwn

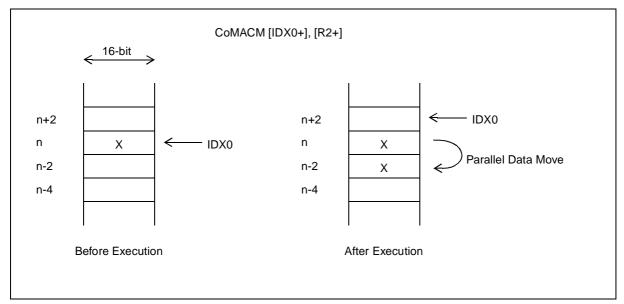

For the CoMACM class of instruction, Parallel Data Move mechanism is implemented. This class of instruction is only available with double indirect addressing mode. Parallel Data Move allows the operand pointed by  $IDX_i$  to be moved to a new location in parallel with the MAC operation. The write-back address of Parallel Data Move is calculated depending on the post-modification of  $IDX_i$ . It is obtained by the reverse operation than the one used to calculate the new value of  $IDX_i$ . The following table shows these rules.

| Instruction                                  | Writeback Address                       |

|----------------------------------------------|-----------------------------------------|

| CoMACM [IDX <sub>i</sub> +],                 | <idx<sub>i-2&gt;</idx<sub>              |

| CoMACM [IDX <sub>i</sub> -],                 | <idx<sub>i+2&gt;</idx<sub>              |

| CoMACM [IDX <sub>i</sub> +QX <sub>j</sub> ], | <idx<sub>i-QX<sub>j</sub>&gt;</idx<sub> |

| CoMACM [IDX <sub>i</sub> -QX <sub>j</sub> ], | <idx<sub>i+QX<sub>j</sub>&gt;</idx<sub> |

#### Table 3 Parallel data move addressing

#### ST10R272L - MULTIPLY-ACCUMULATE UNIT (MAC)

The Parallel Data Move shifts a table of operands in parallel with a computation on those operands. Its specific use is for signal processing algorithms like filter computation. The following figure gives an example of Parallel Data Move with CoMACM instruction.

#### Figure 6 Example of parallel data move

#### 16 x 16 signed/unsigned parallel multiplier

The multiplier executes 16 x 16-bit parallel signed/unsigned fractional and integer multiplies. The multiplier has two 16-bit input ports, and a 32-bit product output port. The input ports can accept data from the MA-bus and from the MB-bus. The output is sign-extended and then feeds a scaler that shifts the multiplier output according to the shift mode bit MP specified in the co-processor Control Word (MCW). The product can be shifted one bit left to compensate for the extra sign bit gained in multiplying two 16-bit signed (2's complement) fractional numbers if bit MP is set.

#### 40-bit signed arithmetic unit

The arithmetic unit over 32 bits wide to allow intermediate overflow in a series of multiply/ accumulate operations. The extension flag E, contained in the most significant byte of MSW, is set when the Accumulator has overflowed beyond the 32-bit boundary, that is, when there are significant (non-sign) bits in the top eight (signed arithmetic) bits of the Accumulator.

The 40-bit arithmetic unit has two 40-bit input ports A and B. The A-input port accepts data from 4 possible sources: 00,0000,0000h, 00,0000,8000h (round), the sign-extended product, or the sign-extended data conveyed by the 32-bit bus resulting from the concatenation of MA-and MB-buses. Product and Concatenation can be shifted left by one according to MP for the multiplier or to the instruction for the concatenation. The B-input port is fed either by the 40-bit shifted/not shifted and inverted/not inverted accumulator or by 00,0000,0000h. A-input and B-

input ports can receive 00,0000,0000h to allow direct transfers from the B-source and Asource, respectively, to the Accumulator (case of Multiplication, Shift.). The output of the arithmetic unit goes to the Accumulator.

It is also possible to saturate the Accumulator on a 32-bit value, automatically after every accumulation. Automatic saturation is enabled by setting the saturation bit MS in the MCW register. When the Accumulator is in the saturation mode and an 32-bit overflow occurs, the accumulator is loaded with either the most positive or the most negative value representable in a 32-bit value, depending on the direction of the overflow. The value of the Accumulator upon saturation is 00,7fff,ffffh (positive) or ff,8000,0000h (negative) in signed arithmetic. Automatic saturation sets the SL flag MSW. This flag is a sticky flag which means it stays set until it is explicitly reset by the user.

40-bit overflow of the Accumulator sets the SV flag in MSW. This flag is also a sticky flag.

#### 40-bit accumulator register

The 40-bit Accumulator consists of three SFR registers MAH, MAL and MAE. MAH and MAL are 16-bit wide. MAE is 8-bit wide and is contained within the least significant byte of MSW. Most co-processor operations specify the 40-bit Accumulator register as source and/or destination operand.

#### Data limiter

Saturation arithmetic is also provided to selectively limit overflow, when reading the accumulator by means of a CoSTORE <destination> MAS instruction. Limiting is performed on the MAC Accumulator. If the contents of the Accumulator can be represented in the destination operand size without overflow, the data limiter is disabled and the operand is not modified. If the contents of the accumulator cannot be represented without overflow in the destination operand size, the limiter will substitute a 'limited' data as explained in the following table.

| Register | E bit | N bit | Output of the Limiter |

|----------|-------|-------|-----------------------|

| х        | 0     | х     | unchanged             |

| MAS      | 1     | 0     | 7fffh                 |

| MAS      | 1     | 1     | 8000h                 |

#### Table 4 Data Limit Values

Note In this case, the accumulator and the status register are not affected. MAS readable from a CoSTORE instruction.

#### Accumulator shifter

The Accumulator shifter is a parallel shifter with a 40-bit input and a 40-bit output. The source operand of the shifter is the Accumulator and the possible shifting operations are:

- No shift (Unmodified)

- Up to 8-bit Arithmetic Left Shift

- Up to 8-bit Arithmetic Right Shift

E, SV and SL bits from MSW are affected by Left shifts, therefore if the saturation mechanism is enabled (MS), the behavior is similar to the one of the arithmetic unit. The carry flag C is also affected by left shifts.

#### Repeat unit

The MAC includes a repeat unit allowing the repetition of some co-processor instructions up to  $2^{13}$  (8192) times. The repeat count may be specified either by an immediate value (up to 31 times) or by the content of the Repeat Count (bits 12 to 0) in the MAC Repeat Word (MRW). If the Repeat Count equals "N" the instruction will be executed "N+1" times. At each iteration of a cumulative instruction the Repeat Count is tested for zero. If it is zero the instruction is terminated else the Repeat Count is decremented and the instruction is repeated. During such a repeat sequence, the Repeat Flag in MRW is set until the last execution of the repeated instruction.

The syntax of repeated instructions is shown in the following examples:

| 1 | Repeat #24 times   |   |                   |  |

|---|--------------------|---|-------------------|--|

|   | CoMAC[IDX0+],[R0+] | ; | repeated 24 times |  |

In example 1, the instruction is repeated according to a 5-bit immediate value. The Repeat Count in MRW is automatically loaded with this value minus one (MRW=23).

| 1 | MOV MRW, #00FFh      | ; load MRW            |

|---|----------------------|-----------------------|

|   | NOP                  | ; instruction latency |

|   | Repeat MRW times     |                       |

|   | CoMACM [IDX1-],[R2+] | ; repeated 256 times  |

In this example, the instruction is repeated according to the Repeat Count in MRW. Notice that due to the pipeline processing at least one instruction should be inserted between the write of MRW and the next repeated instruction.

Repeat sequences may be interrupted. When an interrupt occurs during a repeat sequence, the sequence is stopped and the interrupt routine is executed. The repeat sequence resumes at the end of the interrupt routine. During the interrupt, MR remains set, indicating that a repeated instruction has been interrupted and the Repeat Count holds the number (minus 1)

of repetition that remains to complete the sequence. If the Repeat Unit is used in the interrupt routine, MRW must be saved by the user and restored before the end of the interrupt routine.

Note The Repeat Count should be used with caution. In this case MR should be written as 0. In general MR should not be set by the user otherwise correct instruction processing can not be guaranteed.

#### **MAC** interrupt

57

The MAC can generate an interrupt according to the value of the status flags C (carry), SV (overflow), E (extension) or SL (limit) of the MSW. The MAC interrupt is globally enabled when the MIE flag in MCW is set. When it is enabled the flags C, SV, E or SL can triggered a MAC interrupt when they are set provided that the corresponding mask flag CM, VM, EM or LM in MCW is also set. A MAC interrupt request set the MIR flag in MSW, this flag must be reset by the user during the interrupt routine otherwise the interrupt processing restarts when returning from the interrupt routine.

The MAC interrupt is implemented as a Class B hardware trap (trap number Ah - trap priority I). The associated Trap Flag in the TFR register is MACTRP, bit #6 of the TFR (Remember that this flag must also be reset by the user in the case of an MAC interrupt request).

As the MAC status flags are updated (or eventually written by software) during the Execute stage of the pipeline, the response time of a MAC interrupt request is 3 instruction cycles (see Figure 3). It is the number of instruction cycles required between the time the request is sent and the time the first instruction located at the interrupt vector location enters the pipeline. Note that the IP value stacked after a MAC interrupt does not point to the instruction that triggers the interrupt.

| FETCH     | N   | N+1 | N+2 | N+3 | N+4      | 11       | 12       |

|-----------|-----|-----|-----|-----|----------|----------|----------|

| DECODE    | N-1 | N   | N+1 | N+2 | TRAP (1) | TRAP (2) | 11       |

| EXECUTE   | N-2 | N-1 | Ν   | N+1 | N+2      | TRAP (1) | TRAP (2) |

| WRITEBACK | N-3 | N-2 | N-1 | N   | N+1      | N+2      | TRAP (1) |

Figure 7 Pipeline diagram for MAC interrupt response time

#### Number representation & rounding

The MAC supports the two's-complement representation of binary numbers. In this format, the sign bit is the MSB of the binary word. This is set to zero for positive numbers and set to one for negative numbers. Unsigned numbers are supported only by multiply/multiply-accumulate instructions which specifies whether each operand is signed or unsigned.

In two's complement fractional format, the N-bit operand is represented using the 1.[N-1] format (1 signed bit, N-1 fractional bits). Such a format can represent numbers between -1 and  $+1-2^{-[N-1]}$ . This format is supported when MP of MCW is set.

The MAC implements 'two's complement rounding'. With this rounding type, one is added to the bit to the right of the rounding point (bit 15 of MAL), before truncation (MAL is cleared).

#### 6 INTERRUPT AND TRAP FUNCTIONS

The architecture of the ST10R272L supports several mechanisms for fast and flexible response to the service requests that can be generated from various sources, internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced, either by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In a standard interrupt service, program execution is suspended and a branch to the interrupt service routine is performed. For a PEC service, just one cycle is 'stolen' from the current CPU activity. A PEC service is a single, byte or word data transfer between any two memory locations, with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is decremented for each PEC service, except in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are very well suited, for example, to the transmission or reception of blocks of data. The ST10R272L has 8 PEC channels, each of which offers fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield, exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher priority service request. For standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs, feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

#### 6.1 Interrupt Sources

| Source of Interrupt or PEC<br>Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location | Trap<br>Number |

|-----------------------------------------------|-----------------|----------------|---------------------|--------------------|----------------|

| External Interrupt 0                          | CC8IR           | CC8IE          | CC8INT              | 60h                | 18h            |

| External Interrupt 1                          | CC9IR           | CC9IE          | CC9INT              | 64h                | 19h            |

| External Interrupt 2                          | CC10IR          | CC10IE         | CC10INT             | 68h                | 1Ah            |

| External Interrupt 3                          | CC11IR          | CC11IE         | CC11INT             | 6Ch                | 1Bh            |

| GPT1 Timer 2                                  | T2IR            | T2IE           | T2INT               | 88h                | 22h            |

| GPT1 Timer 3                                  | T3IR            | T3IE           | T3INT               | 8Ch                | 23h            |

| GPT1 Timer 4                                  | T4IR            | T4IE           | T4INT               | 90h                | 24h            |

| GPT2 Timer 5                                  | T5IR            | T5IE           | T5INT               | 94h                | 25h            |

| GPT2 Timer 6                                  | T6IR            | T6IE           | T6INT               | 98h                | 26h            |

| GPT2 CAPREL Register                          | CRIR            | CRIE           | CRINT               | 9Ch                | 27h            |

| ASC0 Transmit                                 | SOTIR           | SOTIE          | SOTINT              | A8h                | 2Ah            |

| ASC0 Transmit Buffer                          | SOTBIR          | SOTBIE         | SOTBINT             | 11Ch               | 47h            |

| ASC0 Receive                                  | SORIR           | SORIE          | SORINT              | ACh                | 2Bh            |

| ASC0 Error                                    | SOEIR           | SOEIE          | SOEINT              | B0h                | 2Ch            |

| PWM Channel 3                                 | PWMIR           | PWMIE          | PWMINT              | FCh                | 3Fh            |

| SSP Interrupt                                 | XP1IR           | XP1IE          | XP1INT              | 104h               | 41h            |

| PLL Unlock                                    | XP3IR           | XP3IE          | XP3INT              | 10Ch               | 43h            |

Table 5 List of possible interrupt sources, flags, vector and trap numbers

#### 6.2 Hardware Traps

Exceptions or error conditions that arise during run-time are called Hardware Traps. Hardware traps cause immediate non-maskable system reaction similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is additionally signified by an individual bit in the trap flag register (TFR). Except when another higher prioritized trap service is in progress, a hardware trap will interrupt any actual program execution. In turn, hardware trap services can not normally be interrupted by standard or PEC interrupts. The following table shows all of the possible exceptions or error conditions that can arise during run-time:

| Exception Condition         | Trap Flag | Trap Vector | Vector<br>Location                          | Trap<br>Number     | Trap<br>Priority           |

|-----------------------------|-----------|-------------|---------------------------------------------|--------------------|----------------------------|

| Reset Functions:            |           |             |                                             |                    |                            |

| Hardware Reset              |           | RESET       | 00'0000h                                    | 00h                | ш                          |

| Software Reset              |           | RESET       | 00'0000h                                    | 00h                | ш                          |

| Watchdog Timer Overflow     |           | RESET       | 00'0000h                                    | 00h                | 111                        |

| Class A Hardware Traps:     |           |             |                                             |                    |                            |

| Non-Maskable Interrupt      | NMI       | NMITRAP     | 00'0008h                                    | 02h                | П                          |

| Stack Overflow              | STKOF     | STOTRAP     | 00'0010h                                    | 04h                | П                          |

| Stack Underflow             | STKUF     | STUTRAP     | 00'0018h                                    | 06h                | П                          |

| Class B Hardware Traps:     |           |             |                                             |                    |                            |

| Undefined opcode            | UNDOPC    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| Protected instruction fault | PRTFLT    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| Illegal word operand access | ILLOPA    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| Illegal instruction access  | ILLINA    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| Illegal external bus access | ILLBUS    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| MAC trap                    | MACTRP    | BTRAP       | 00'0028h                                    | 0Ah                | I                          |

| Reserved                    |           |             | [2Ch – 3Ch]                                 | [0Bh – 0Fh]        |                            |

| Software Traps              |           |             |                                             |                    |                            |

| TRAP Instruction            |           |             | Any [00'0000h<br>– 00'01FCh]<br>steps of 4h | Any<br>[00h – 7Fh] | Current<br>CPU<br>Priority |

Table 6 Exceptions or error conditions

#### 7 PARALLEL PORTS

The ST10R272L provides up to 77 I/O lines organized into 7 input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs by direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of three I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation by control registers. During the internal reset, all port pins are configured as inputs.

All port lines have programmable alternate input or output functions associated with them. PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A23/19/17...A16 in systems where segmentation is enabled to access more than 64 KBytes of memory. Port 6 provides optional bus arbitration signals (BREQ, HLDA, HOLD) and chip select signals. Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE and the system clock output (CLKOUT). Port 5 is used for timer control signals. Port 2 lines can be used as fast external interrupt lines. Port 7 includes alternate function for the PWM signal. All port lines that are not used for these alternate functions may be used as general purpose I/O lines.

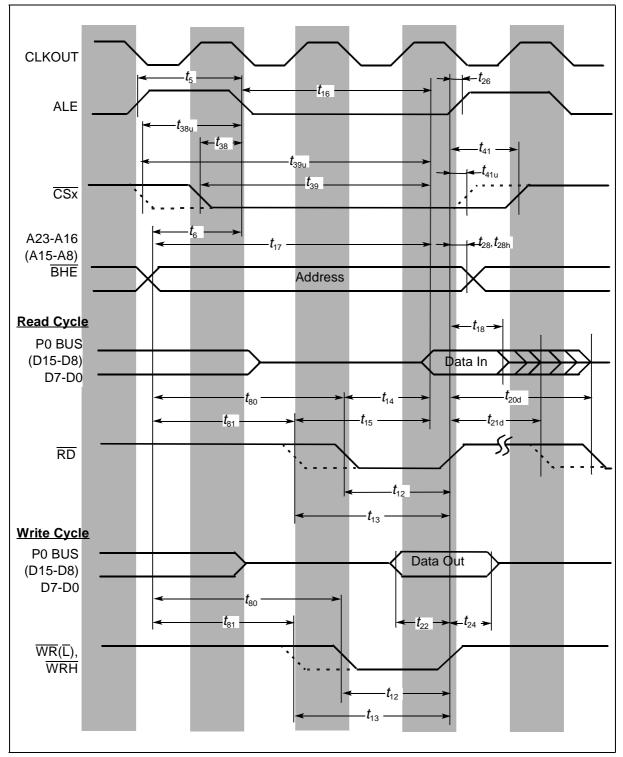

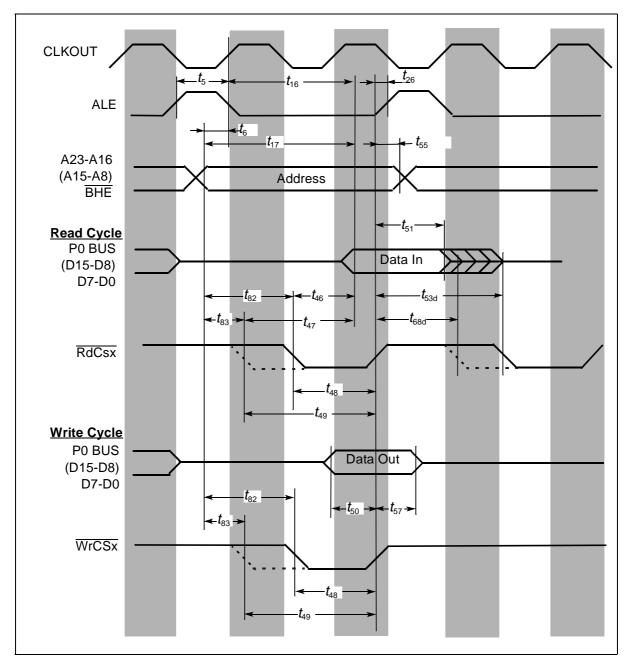

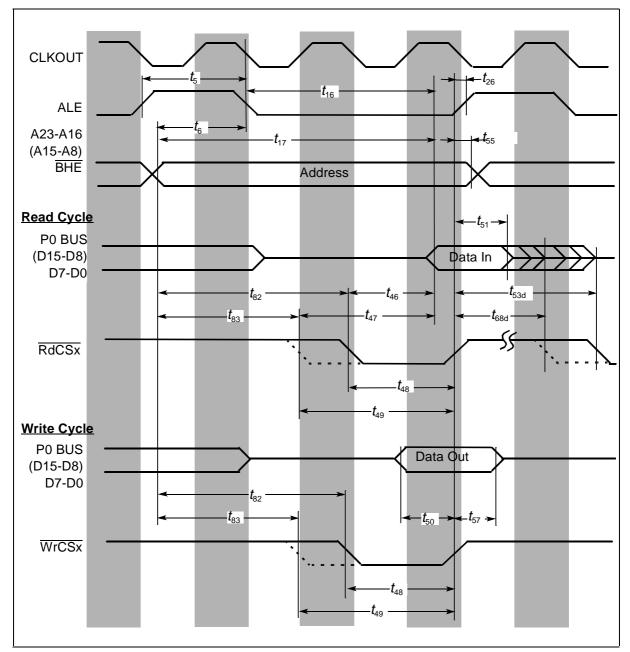

#### 8 EXTERNAL BUS CONTROLLER

All external memory accesses are performed by the on-chip External Bus Controller which can be programmed either to single chip mode when no external memory is required, or to the following external memory access modes:

| 16-bit data, demultiplexed | 16-/18-/20-/24-bit addresses |

|----------------------------|------------------------------|

| 16-bit data, multiplexed   | 16-/18-/20-/24-bit addresses |

| 8-bit data, multiplexed    | 16-/18-/20-/24-bit addresses |

| 8-bit data, demultiplexed  | 16-/18-/20-/24-bit addresses |

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/output on PORT0/P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

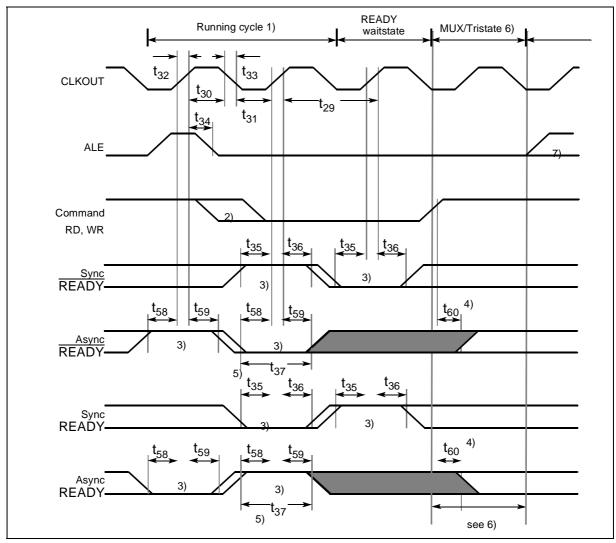

Memory cycle time, memory tri-state time, length of ALE and read write delay are programmable so that a wide range of different memory types and external peripherals can be used. Up to 4 independent address windows can be defined (via ADDRSELx / BUSCONx register pairs) to access different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 etc. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0. Up to 5 external  $\overline{CS}$  signals (4 windows plus default) can be generated to reduce external glue logic. Access to very slow memories is supported by the READY function.

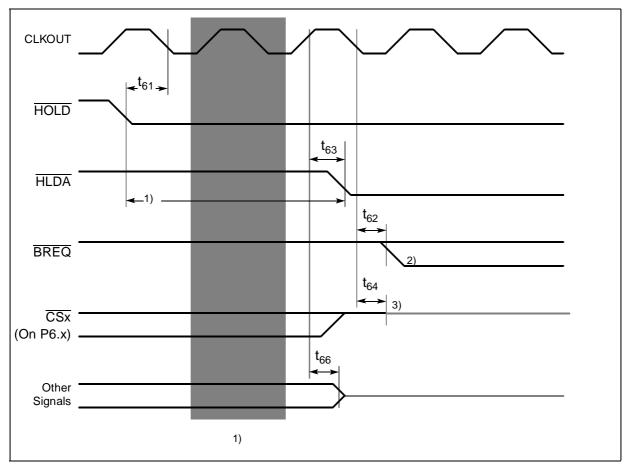

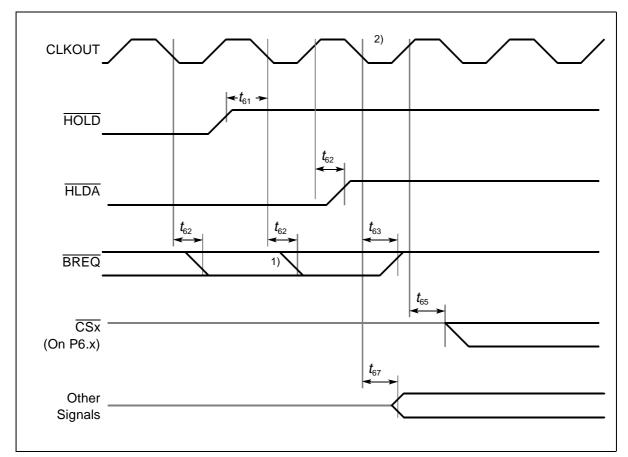

A HOLD/HLDA protocol is available for bus arbitration so that external resources can be shared with other bus masters. In slave mode, the slave controller can be connected to another master controller without glue logic. For applications which require less than 16 MBytes

of external memory space, the address space can be restricted to 1 MByte, 256 KByte or to 64 KByte.

#### 9 PWM MODULE

A 1-channel Pulse Width Modulation (PWM) Module operates on channel 3. The pulse width modulation module can generate up to four PWM output signals using edge-aligned or centrealigned PWM. In addition, the PWM module can generate PWM burst signals and single shot outputs. The table below shows the PWM frequencies for different resolutions. The level of the output signals is selectable and the PWM module can generate interrupt requests.

| Mode 0<br>edge aligned   | Resolution | 8-bit     | 10-bit   | 12-bit   | 14-bit   | 16-bit  |

|--------------------------|------------|-----------|----------|----------|----------|---------|

| CPU clock/1              | 20ns       | 195.3 KHz | 48.83KHz | 12.21KHz | 3.052KHz | 762.9Hz |

| CPU clock/64             | 1.28ns     | 3.052KHz  | 762.9Hz  | 190.7Hz  | 47.68Hz  | 11.92Hz |

| Mode 1<br>center aligned | Resolution | 8-bit     | 10-bit   | 12-bit   | 14-bit   | 16-bit  |

| CPU clock/1              | 20ns       | 97.66KHz  | 24.41KHz | 6.104KHz | 1.525KHz | 381.5Hz |

| CPU clock/64             | 1.28ns     | 1.525Hz   | 381.5 Hz | 95.37Hz  | 23.84Hz  | 0Hz     |

Table 7 PWM unit frequencies and resolution at 50MHz CPU clock

#### 10 GENERAL PURPOSE TIMERS

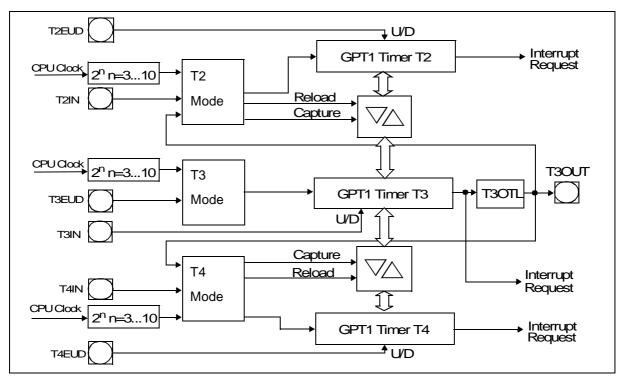

The GPTs are flexible multifunctional timer/counters used for time-related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation or pulse multiplication. The GPT unit contains five 16-bit timers, organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

#### 10.1 GPT1

Each of the three timers T2, T3, T4 of the GPT1 module can be configured individually for one of four basic modes of operation: **timer**, **gated timer**, **counter mode and incremental interface mode**. In timer mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler. In counter mode, the timer is clocked in reference to external events. Pulse width or duty cycle measurement is supported in gated timer mode where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. Table 8 GPT1 timer input frequencies, resolution and periods for each pre-scaler option at 50MHz CPU clock. This also applies to the Gated Timer Mode of T3 and to the auxiliary timers T2 and T4 in Timer and Gated Timer Mode

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD).

In Incremental Interface Mode, the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B by their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has output toggle latches (TxOTL) which changes state on each timer over-flow/ underflow. The state of this latch may be output on port pins (TxOUT) e. g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

| F <sub>CPU</sub> =50MHz | Timer inp | Timer input selection |               |            |            |            |             |              |  |  |

|-------------------------|-----------|-----------------------|---------------|------------|------------|------------|-------------|--------------|--|--|

| 0.0                     | 000b      | 001b                  | 010b          | 011b       | 100b       | 101b       | 110b        | 111b         |  |  |

| Prescaler<br>Factor     | 8         | 16                    | 32            | 64         | 128        | 256        | 512         | 1024         |  |  |

| Input<br>Frequency      | 6.25 MHz  | 3.125<br>MHz          | 1.5625<br>MHz | 781<br>KHz | 391<br>KHz | 195<br>KHz | 97.5<br>KHz | 48.83<br>KHz |  |  |

| Resolution              | 160ns     | 320ns                 | 640ns         | 1.28 us    | 2.56 us    | 5.12 us    | 10.24 us    | 20.48 us     |  |  |

| Period                  | 10.49ms   | 20.97ms               | 41.94ms       | 83.88ms    | 168ms      | 336ms      | 672ms       | 1.342s       |  |  |

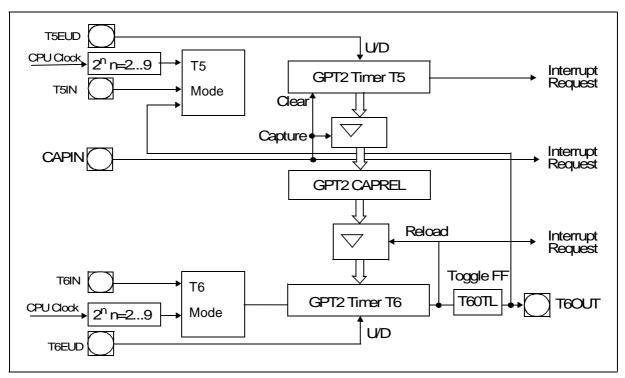

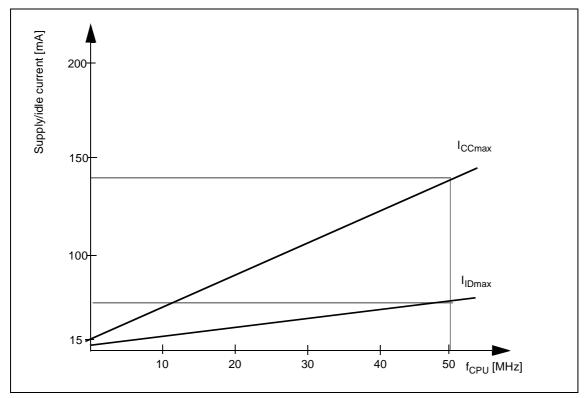

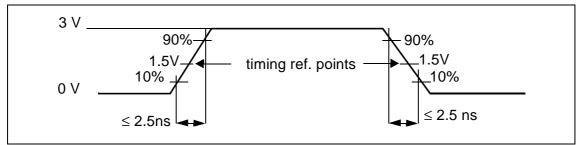

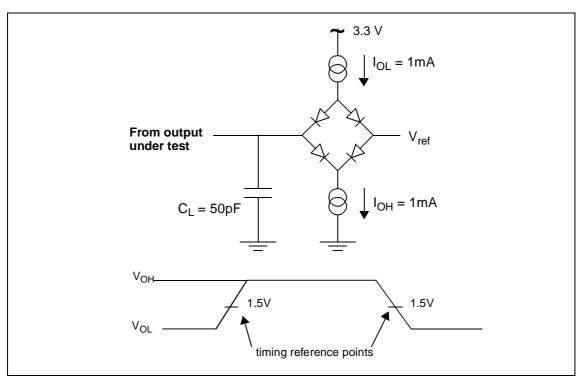

Table 8 GPT1 timer input frequencies, resolution and periods