# STPIC6A259

PRELIMINARY DATA

# POWER LOGIC 8-BIT ADDRESSABLE LATCH

# LOW R<sub>DS(on)</sub>: 1Ω TYP

- OUTPUT SHORT-CIRCUIT PROTECTION

- 75mJ AVAILANCHE ENERGY

- EIGHT 350mA DMOS OUTPUTS

- 50V SWITCHING CAPABILITY

- FOUR DISTINCT FUNCTION MODES

- LOW POWER CONSUMPTION

#### DESCRIPTION

This power logic 8-bit addressable latch controls open-drain DMOS transistor outputs and is general-purpose designed for storage applications in digital systems. Specific uses include working registers, serial-holding registers, and decoders or demultiplexers. This is a multifunctional device capable of operating as addressable latches or an 8-line eight demultiplexer with active-low DMOS outputs. Each open-drain DMOS transistor features an independent chopping current-limiting circuit to prevent damage in the case of a short circuit.

Four distinct modes of operation are selectable by controlling the clear (CLR) and enable (G) inputs and enumerated in the function table. In the addressable-latch mode, data at the data-in (D) terminal is written into the addressed latch. The addressed DMOS-transistor output inverts the data input with all unadressed DMOS-transistor output remaining in their previous state. In the MOS-transistor outputs, emain in their previous states and are unaffected by the data or address inputs. To eliminate the possibility of entering erroneus data in the latch, enable G should be

# ORDI:RING CODES

| Control of the |

|----------------|

| SOP            |

| .(5)           |

held high (inactive) while the address lines are changing. In the 8-line demoultiplexing mode, the addressed output is inverted with respect to the D input and all other output are high. In the clear mode, all outputs are high and unaffected by the address and data inputs.

Separate power ground (PGND) and logic ground (ICND) terminals are provided to facilitate maximum system flexibility. All PGND terminals are interally connected, and each pGND terminal must be externally connected to the power system ground in order to minimize parasitic impedance. A single-point connection between LGND and PGND must be made externally in a manner that reduces crosstalk between the logi and load circuits.

The STPIC6A259 is offered in a termally enhanced SO-24 package. The STPIC6A259 is characterized for operation over the operating case temperature range -40°C to 125°C.

| Туре          | Package                     | Comments                          |

|---------------|-----------------------------|-----------------------------------|

| STPIC6A259M   | SO-24 Batwing (Tube)        | 50parts per tube / 20tube per box |

| STPIC6A259MTR | SO-24 Batwing (Tape & Reel) | 2500 parts per reel               |

#### March 2001

This is preliminary information on a new product now in development are or undergoing evaluation. Details subject to change without notice.

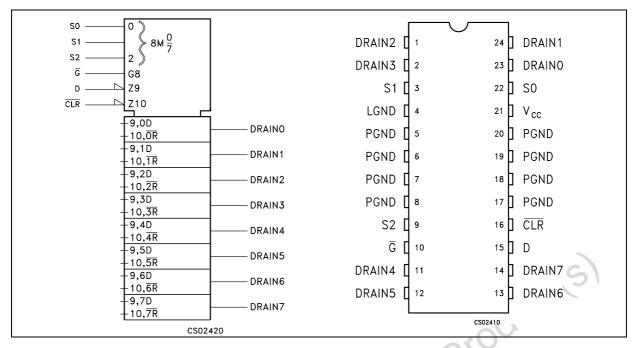

# LOGIC SYMBOL AND PIN CONFIGURATION

# FUNCTIONAL TABLE

| INPUTS |   | S | OUTPUT OF       | EACH<br>OTHER   | FUNCTION      |  |

|--------|---|---|-----------------|-----------------|---------------|--|

| CLR    | G | D | DRAIN           | DRAIN           | FUNCTION      |  |

| Н      | L | Н | L               | Q <sub>io</sub> | Addressable   |  |

| Н      | L | L | Н               | Q <sub>io</sub> | Latch         |  |

| Н      | Н | Х | Q <sub>io</sub> | Q <sub>io</sub> | Memory        |  |

| L      | L | Н | L               | Н               | 8-Line        |  |

| L      | L | L | Н               | Н               | Demultiplexer |  |

| L      | Н | Х | Н               | Н               | Clear         |  |

# FUNCTIONAL TABLE

| SEL    | ECT INP | UTS | DRAIN ADDRESSED |  |  |

|--------|---------|-----|-----------------|--|--|

| S2     | S2 S1   |     | DRAIN ADDRESSED |  |  |

| 5      | L       | L   | 0               |  |  |

| L<br>L | L       | Н   | 1               |  |  |

| L      | Н       | L   | 2               |  |  |

| L      | Н       | Н   | 3               |  |  |

| Н      | L       | L   | 4               |  |  |

| Н      | L       | Н   | 5               |  |  |

| Н      | Н       | L   | 6               |  |  |

| Н      | Н       | Н   | 7               |  |  |

57

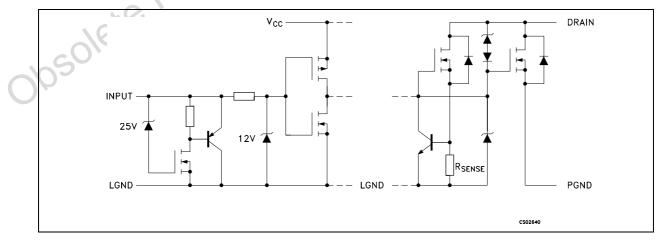

# INPUT AND OUTPUT EQUIVALENT CIRCUITS

2/13

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                               | Value       | Unit |

|------------------|-------------------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>  | Logic Supply Voltage (See Note 2)                                       | 7           | V    |

| VI               | Logic Input Voltage Range                                               | -0.3 to 7   | V    |

| V <sub>DS</sub>  | Power DMOS Drain to Source Voltage (See Note 2)                         | 50          | V    |

| I <sub>DS</sub>  | Continuous Source to Drain Diode Anode Current                          | 1           | Α    |

| I <sub>DS</sub>  | Pulsed Source to Drain Diode Anode Current (See Note 3)                 | 2           | Α    |

| I <sub>D</sub>   | Pulsed Drain Current, Each Output, All Output ON (T <sub>C</sub> =25°C) | 1.1         | Α    |

| I <sub>D</sub>   | Continuous Current, Each Output, All Output ON (T <sub>C</sub> =25°C)   | 350         | mA   |

| I <sub>D</sub>   | Peak Drain Current Single Output (T <sub>C</sub> =25°C) (See Note 3)    | 1.1         | А    |

| E <sub>AS</sub>  | Single Pulse Avalanche Energy (See Note 6)                              | 75          | mJ   |

| I <sub>AS</sub>  | Avalanche Current (See Note 4)                                          | 600         | mA   |

| Pd               | Continuous total dissipation ( $T_C \le 25^{\circ}C$ )                  | 1750        | mW   |

| Pd               | Continuous total dissipation ( $T_C = 125^{\circ}C$ )                   | 350         | mW   |

| ТJ               | Operating Virtual Junction Temperature Range                            | -40 to +150 | °C   |

| Т <sub>С</sub>   | Operating Case Temperature Range                                        | -40 to +125 | °C   |

| T <sub>stg</sub> | Storage Temperature Range                                               | -65 to +150 | °C   |

| ΤL               | Lead Temperature 1.6mm (1/16inch) from case for 10 seconds              | 260         | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

# THERMAL DATA

| not implied.          |                                     | e v i |      |

|-----------------------|-------------------------------------|-------|------|

| THERMA                | LDATA                               |       |      |

| Symbol                | Parameter                           |       | Unit |

| R <sub>thj-case</sub> | Thermal Resistance Junction-case    | 10    | °C/W |

| R <sub>thj-amb</sub>  | Thermal Resistance Junction-ambient | 50    | °C/W |

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                                                                              | Min.                | Max.                | Unit |

|-----------------|----------------------------------------------------------------------------------------|---------------------|---------------------|------|

| V <sub>CC</sub> | Logic Supply Voltage                                                                   | 4.5                 | 5.5                 | V    |

| V <sub>IH</sub> | High Level Input Voltage                                                               | 0.85V <sub>CC</sub> | V <sub>CC</sub>     | V    |

| V <sub>IL</sub> | Low Level Input Voltage                                                                | 0                   | 0.15V <sub>CC</sub> | V    |

| I <sub>DP</sub> | Pulse Drain Output Current (T <sub>C</sub> =25°C, V <sub>CC</sub> =5V) (see note 3, 5) | -1.8                | 0.6                 | A    |

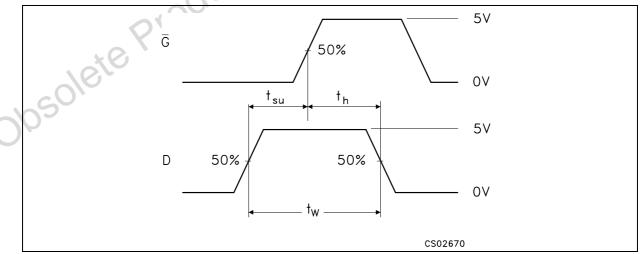

| t <sub>su</sub> | Set-up Time, D High Before $\overline{G} \uparrow$ (see Figure 2)                      | 10                  |                     | ns   |

| t <sub>h</sub>  | Hold Time, D High Before $\overline{G} \uparrow$ (see Figure 2)                        | 5                   |                     | ns   |

| t <sub>W</sub>  | Pulse Duration (see Figure 2)                                                          | 15                  |                     | ns   |

| т <sub>с</sub>  | Operating Case Temperature                                                             | -40                 | 125                 | °C   |

| Symbol               | Parameter                                  | Test Conditions                                                                                  | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>(BR)DSX</sub> | Drain-to-Source breakdown<br>Voltage       | I <sub>D</sub> = 1mA                                                                             | 50   |      |      | V    |

| $V_{SD}$             | Source-to-Drain Diode<br>Forward Voltage   | I <sub>F</sub> = 350 mA (See Note 3)                                                             |      | 0.8  | 1.1  | V    |

| I <sub>IH</sub>      | High Level Input Current                   | $V_{I} = V_{CC}$                                                                                 |      |      | 1    | μΑ   |

| IIL                  | Low Level Input Current                    | $V_{I} = 0$                                                                                      |      |      | -1   | μΑ   |

| I <sub>CC</sub>      | Logic Supply Current                       | I <sub>O</sub> = 0                                                                               |      | 0.5  | 5    | mA   |

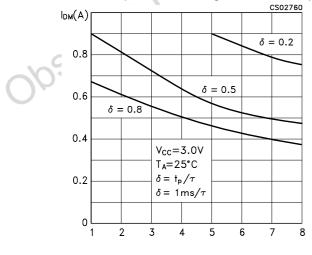

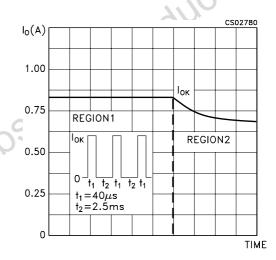

| Ι <sub>ΟΚ</sub>      | Output Current at Which<br>Chopping Starts | $T_{C} = 25^{\circ}C$ (See Note 3 and Figg. 3, 4)                                                | 0.6  | 0.8  | 1.1  | A    |

| I <sub>(nom)</sub>   | Nominal Current                            | $V_{DS(on)} = 0.5V$ $I_{(nom)} = I_D$<br>$V_{CC} = 5V$ $T_C = 85^{\circ}C$<br>(See Note 5, 6, 7) |      | 350  |      | mA   |

| ۱ <sub>D</sub>       | Off-State Drain Current                    | $V_{DS} = 40V$ $T_{C}=25^{\circ}C$                                                               |      | 0.1  | 1    | μA   |

|                      |                                            | $V_{DS} = 40V$ $T_{C} = 125^{\circ}C$                                                            |      | 0.2  | 5    | μA   |

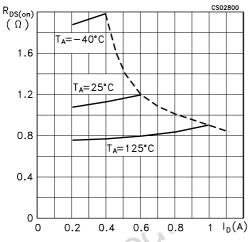

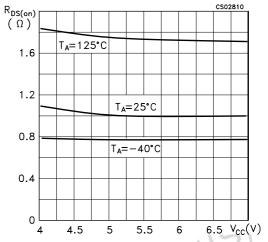

| R <sub>DS(on)</sub>  | Termination Resistance                     | $I_D = 350 \text{mA}$ $T_C = 25^{\circ} \text{C}$                                                |      | 1    | 1.5  | Ω    |

| . /                  | (See Note 5, 6 and figg. 9, 10)            | $I_D = 350 \text{mA}$ $T_C = 125^{\circ}\text{C}$                                                |      | 1.7  | 2.5  | Ω    |

# DC CHARACTERISTICS (V<sub>CC</sub>=5V, T<sub>C</sub>= 25°C, unless otherwise specified.)

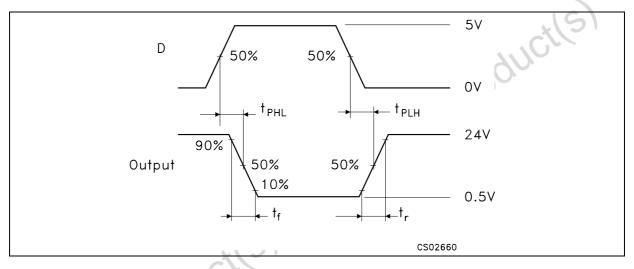

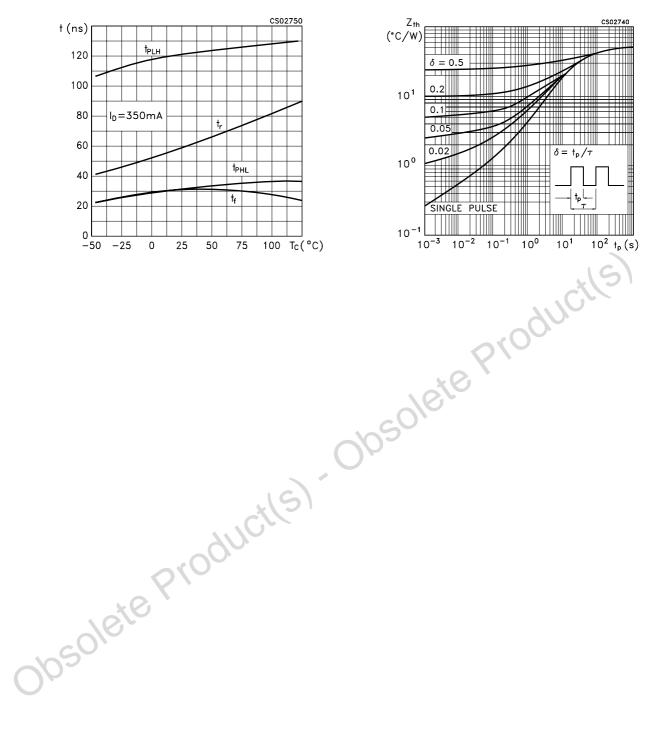

# SWITCHING CHARACTERISTICS ( $V_{CC}=5V$ , $T_{C}=25^{\circ}C$ , unless otherwise specified.)

| Symbol           | Parameter                                                     | Test Conditions                                                      | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| t <sub>PHL</sub> | Propagation Dealy Time,<br>High to Low Level Output<br>from D | C <sub>L</sub> = 30pF I <sub>D</sub> = 350mA<br>(See Figg. 1, 2, 11) | S,   | 30   |      | ns   |

| t <sub>PLH</sub> | Propagation Dealy Time,<br>Low to High Level Output<br>from D | 00501                                                                |      | 125  |      | ns   |

| t <sub>r</sub>   | Rise Time, Drain Output                                       | U.                                                                   |      | 60   |      | ns   |

| t <sub>f</sub>   | Fall Time, Drain Output                                       |                                                                      |      | 30   |      | ns   |

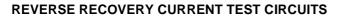

| t <sub>a</sub>   | Reverse Recovery Current<br>Rise Time                         | I <sub>F</sub> = 350mA di/dt = 20A/μs<br>(See Note 5, 6 and Fig. 5)  |      | 100  |      | ns   |

| t <sub>rr</sub>  | Reverse Recovery Time                                         |                                                                      |      | 300  |      | ns   |

Note 1: All Voltage valuea are with respect to LGND and PGND Note 2: Each power DMOS source is internally connected to GND Note 3: Pulse duration  $\leq$  100ms and duty cycle  $\leq$  2% Note 4: Drain Supply Voltage = 15V, starting junction temperature (T<sub>JS</sub>) = 25°C. L = 210µH and I<sub>AS</sub> = 600mA (See Fig. 6) Note 5: Technique should limit T<sub>J</sub> - T<sub>C</sub> to 10°C maximum

Note 6: These parameters are measured with voltage sensing contacts separate from the current-carrying contacts.

Note 7: Nominal Current is defined for a consistent comparison between devices from different sources. It is the current that produces a voltage drop of 0.5V at  $T_c = 85^{\circ}C$ .

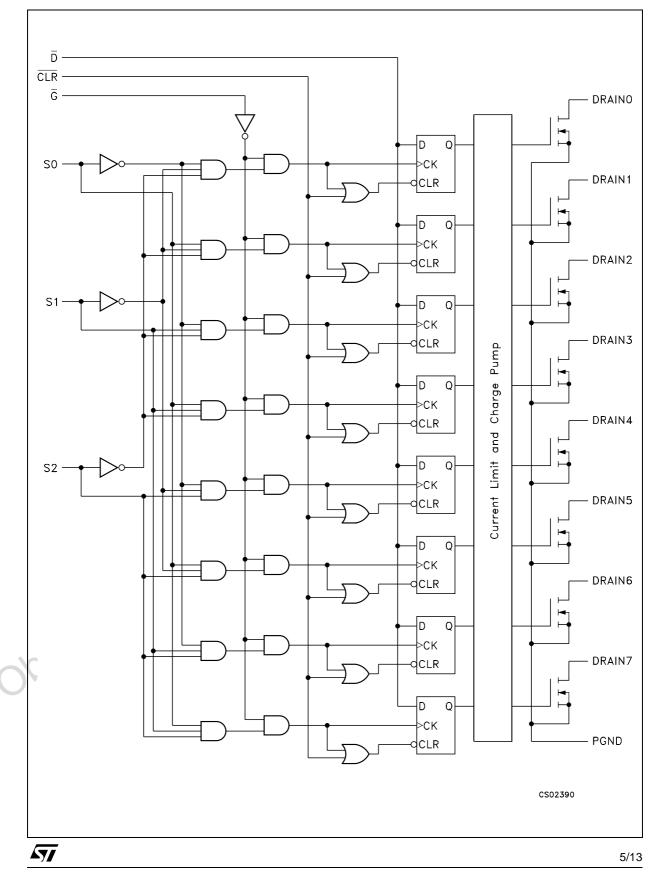

### LOGIC DIAGRAM

# STPIC6A259

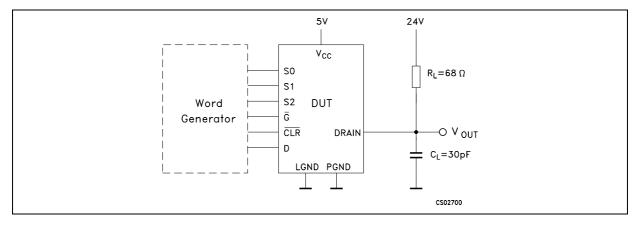

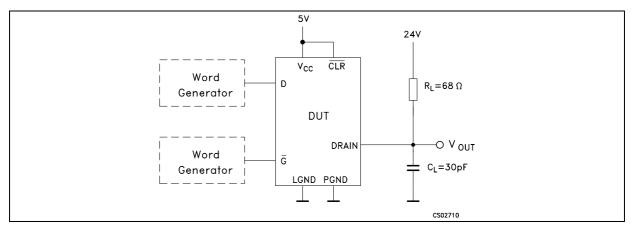

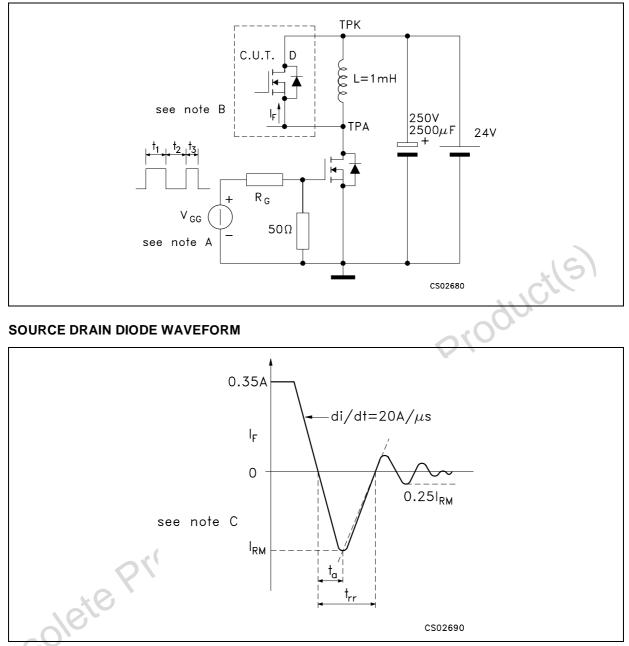

# **TYPICAL OPERATION MODE TEST CIRCUITS**

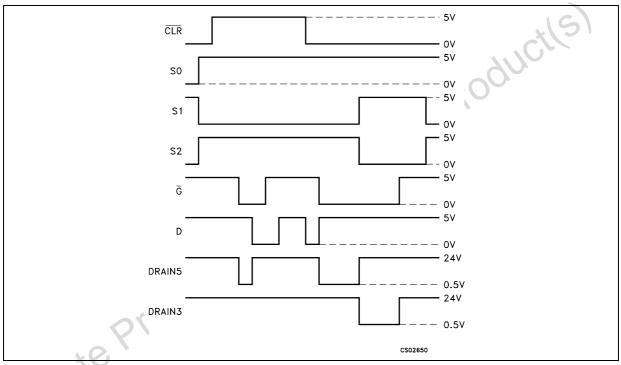

#### **TYPICAL OPERATION MODE WAVEFORMS**

NOTE: A) The word generator has the following characteristics:  $t_r \le 10$ ns,  $t_f \le 10$ ns,  $t_W = 300$ ns, pulse repetition rate (PRR) = 5KHz,  $Z_O = 50\Omega$ B)  $C_L$  includes probe and jig capacitance.

# **TYPICAL OPERATION MODE TEST CIRCUITS**

### SWITCHING TIME WAVEFORM

# INPUT SETUP AND HOLD WAVEFORM

NOTE: A) The word generator has the following characteristics:  $t_r \le 10$ ns,  $t_f \le 10$ ns,  $t_W = 300$ ns, pulse repetition rate (PRR) = 5KHz,  $Z_0 = 50\Omega$ B)  $C_L$  includes probe and jig capacitance.

NOTE: A) The V<sub>GG</sub> amplitude and R<sub>G</sub> are adjusted for di/dt = 20A/ $\mu$ s. A V<sub>GG</sub> double-pulse trainn is used to set I<sub>F</sub> = 0.35A. where t<sub>1</sub> = 10 $\mu$ s, t<sub>2</sub> = 7 $\mu$ s and t<sub>3</sub> = 3 $\mu$ s B) The Drain terminal under test is connected to the TPK test point. All other terminals are connected together and connected to the TPA test point. C) I<sub>RM</sub> = maximum recovery current.

# SINGLE PULSE AVALANCHE ENERGY TEST CIRCUITS

#### SINGLE PULSE AVALANCHE ENERGY WAVEFORM

NOTE: A) The word generator has the following characteristics:  $t_f \le 10$ ns,  $t_f \le 10$ ns,  $Z_O = 50\Omega$ B) Input pulse duration, tW is increased until peak current IAS = 600 mA. Energy test level is defined as  $E_{AS} = (I_{AS} \times V_{(BR)DSX} \times t_{AV})/2 = 75$ mJ.

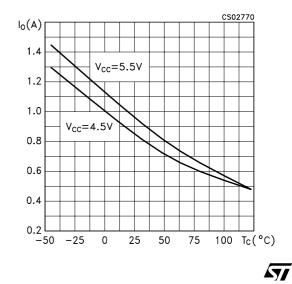

# **TYPICAL PERFORMANCE CHARACTERISTICS** (unless otherwise specified $T_i = 25$ °C)

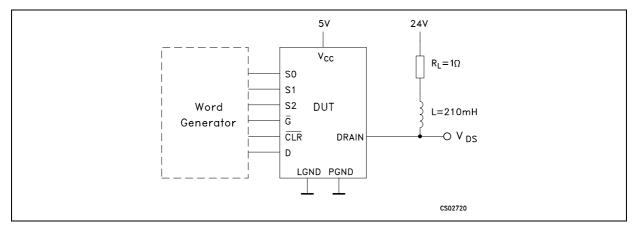

**Figure 1 :** Maximum Continuous Drain Current vs Number of Outputs Conducting Simultaneously

Figure 2 : Static Drain-Source ON-State Resistance vs Drain Current

Figure 3 : MaximumPeak Drain Current vs Number of Outputs Conducting Simultaneously

Figure 4 : Static Drain-Source ON-State Resistance vs Logic Supply Voltage

Figure 5 : Chopping Mode Characteristics

Figure 6 : Output Current vs Case Temperature

Figure 7 : Switching Time vs Case Temperature

Figure 8 : Switching Time vs Case Temperature

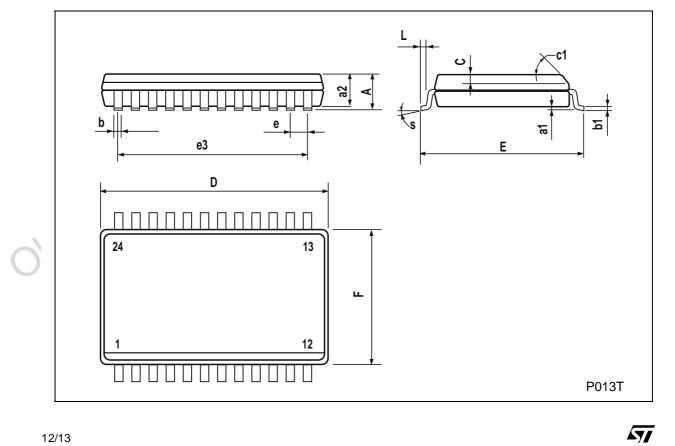

| DIM. |       | mm    | •     | inch   |       |       |  |  |

|------|-------|-------|-------|--------|-------|-------|--|--|

|      | MIN.  | TYP.  | MAX.  | MIN.   | TYP.  | MAX.  |  |  |

| А    |       |       | 2.65  |        |       | 0.104 |  |  |

| a1   | 0.10  |       | 0.20  | 0.004  |       | 0.007 |  |  |

| a2   |       |       | 2.45  |        |       | 0.096 |  |  |

| b    | 0.35  |       | 0.49  | 0.013  |       | 0.019 |  |  |

| b1   | 0.23  |       | 0.32  | 0.009  |       | 0.012 |  |  |

| С    |       | 0.50  |       |        | 0.020 |       |  |  |

| c1   |       |       | 45 (  | (typ.) |       |       |  |  |

| D    | 15.20 |       | 15.60 | 0.598  |       | 0.614 |  |  |

| E    | 10.00 |       | 10.65 | 0.393  |       | 0.420 |  |  |

| е    |       | 1.27  |       |        | 0.05  |       |  |  |

| e3   |       | 13.97 |       |        | 0.55  |       |  |  |

| F    | 7.40  |       | 7.60  | 0.291  |       | 0.299 |  |  |

| L    | 0.50  |       | 1.27  | 0.19   |       | 0.050 |  |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without apprecievely supplied. STMicroelectronics are not authorized for use as critical components in life support devices or systems without expressed without expressed in the support devices or systems without expressed metal to a sufficient or support devices or systems without expressed metal.

© The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom

© http://www.st.com