## NXP Semiconductors

Advance Information

# **IO-link master transceiver**

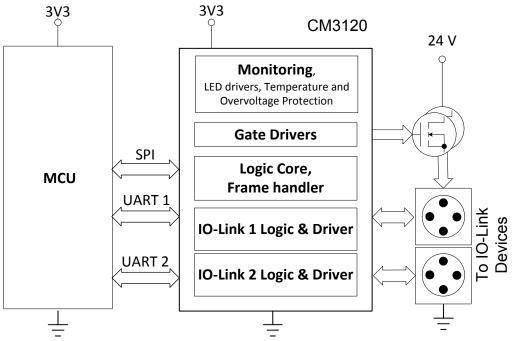

The CM3120 is an IO-Link master physical layer dedicated to the industrial market. It includes two fully-featured IO-Link channels, which can work in three different operation modes. This circuit integrates an IO-Link frame handler fully compliant with the IO-Link v1.1 specification, and which implements most of the IO-Link communication tasks. The frame handler significantly decreases load of the master microcontroller. The CM3120 also provides several protection and monitoring mechanisms such as overcurrent, overvoltage, and overtemperature.

### Features

- Two IO-Link channels with three different operation modes (SIO, UART, and frame handler)

- Protection mechanisms (overcurrent, overtemperature, overvoltage)

- · Configurable through a SPI interface

- Operating voltage range from 8.0 V to 32 V

- Suitable for 2/4/8/16 port-applications

- · Can operate as a Master or Device

- Two integrated LED drivers

- Integrated hardware frame handler (supports all IO-link v1.1 frames and COM1, COM2, and COM3 baud rates)

- · Integrated NMOS gate drivers to control current to the C/Q and L+ lines

### **IO-LINK TRANSCEIVER**

### Applications

- Factory automation

- Fieldbus gateways

- Programmable logic controllers

- Process controllers

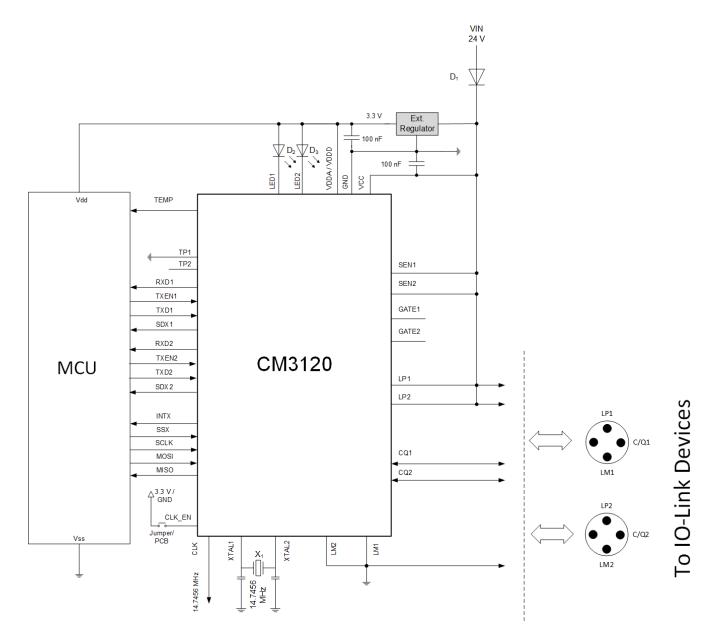

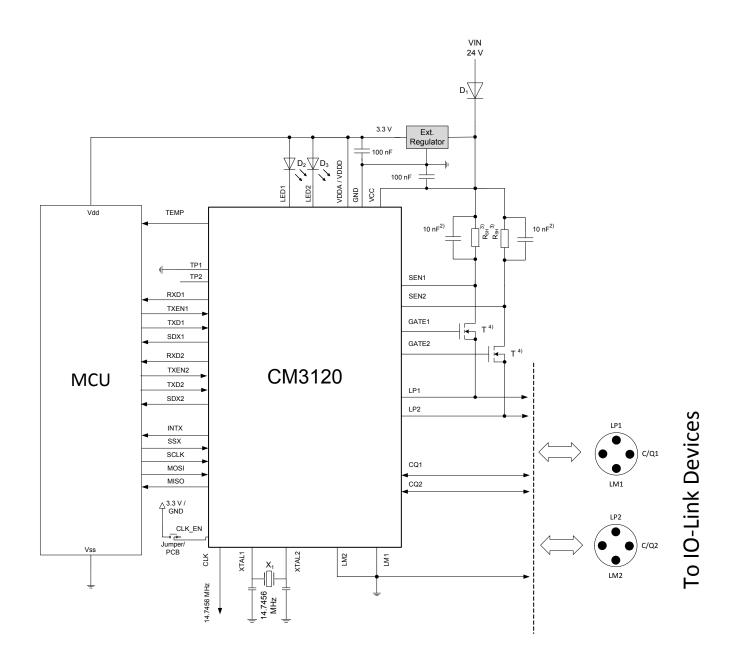

Figure 1. CM3120 simplified application diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

# 1 Orderable parts

### Table 1. Orderable part variations

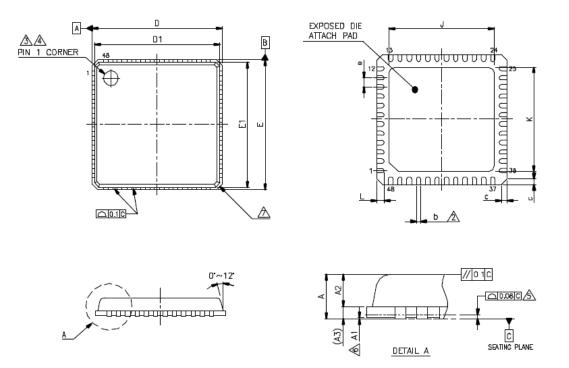

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | V <sub>DD</sub> voltage | Package                                  |

|----------------------------|-------------------------------|-------------------------|------------------------------------------|

| MC34CM3120EP               | -40 °C to 85 °C               | 5.0 V                   | QFN48 with exposed pad (7.0 mm x 7.0 mm) |

Notes

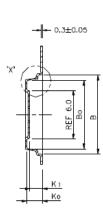

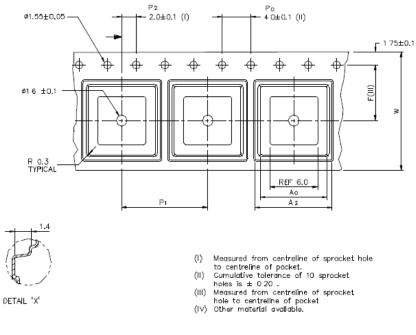

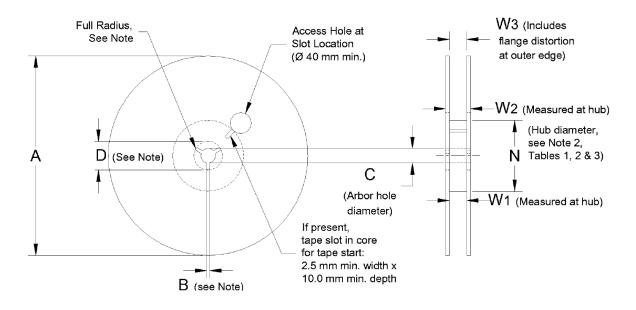

1. To order parts in Tape and Reel, add the R2 suffix to the part number.

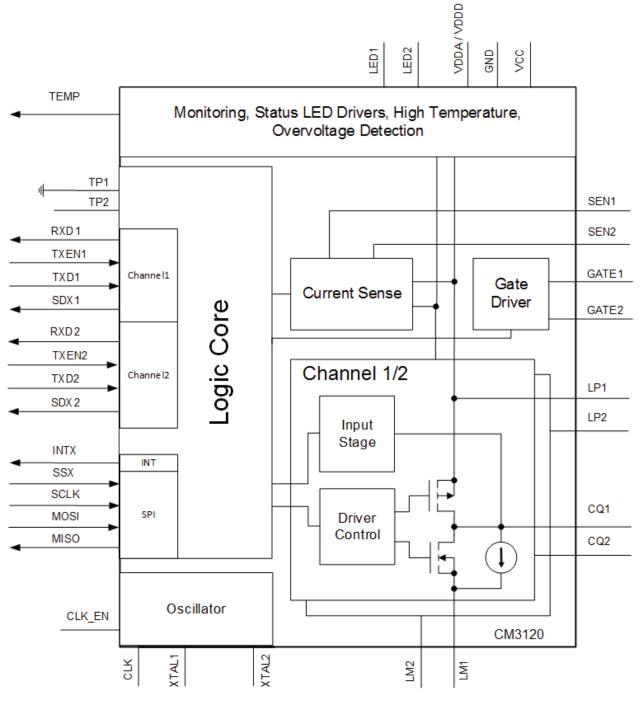

# 2 Internal block diagram

# 3 Pin connections

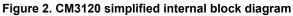

## 3.1 Pinout diagram

### Figure 3. CM3120 pin connections

Functional descriptions of many of these pins can be found in the Functional Pin Description section beginning on page 9.

## 3.2 Pin definitions

### Table 2. CM3120 pin definitions

| Pin                                             | Pin name       | Pin<br>function | Definition                                        |  |  |  |

|-------------------------------------------------|----------------|-----------------|---------------------------------------------------|--|--|--|

| 1                                               | RXD1/<br>CYCT1 | OUT             | RXD1: CQ1 input; inverted                         |  |  |  |

| 2                                               | TXD1/<br>SYNC1 | IN              | TXD1: CQ1 output; internal pull-down; inverted    |  |  |  |

| 3                                               | TXEN1          | IN              | 21 driver enable; active high, internal pull-down |  |  |  |

| 4                                               | SDX1           | OUT             | Device 1 short detected; active low               |  |  |  |

| 5, 11, 21, 25,<br>27, 29, 32, 34,<br>36, 42, 45 | NC             | NC              | Not Connected                                     |  |  |  |

| 6                                               | INTX           | OUT             | SPI interrupt signal; active low                  |  |  |  |

| 7                                               | SSX            | IN              | SPI slave select; active low; internal pull-up    |  |  |  |

| 8                                               | SCLK           | IN              | SPI clock; internal pull-down                     |  |  |  |

| 9                                               | MOSI           | IN              | SPI data in; internal pull-down                   |  |  |  |

| 10                                              | MISO           | OUT             | SPI data out; tri-state if SSX is high            |  |  |  |

## Table 2. CM3120 pin definitions (continued)

| Pin | Pin name       | Pin<br>function | Definition                                                    |  |

|-----|----------------|-----------------|---------------------------------------------------------------|--|

| 12  | CLK            | OUT             | Buffered clock feed through                                   |  |

| 13  | VDDD           | PWR             | 3.3 V digital voltage supply                                  |  |

| 14  | VDDA           | PWR             | .3 V analog voltage supply                                    |  |

| 15  | GND            | PWR             | Ground                                                        |  |

| 16  | RXD2/<br>CYCT2 | OUT             | RXD2: CQ2 input; inverted                                     |  |

| 17  | TXD2/<br>SYNC2 | IN              | RXD2: CQ2 output; internal pull-down; inverted                |  |

| 18  | TXEN2          | IN              | CQ2 driver enable; active high, internal pull-down            |  |

| 19  | SDX2           | OUT             | Device 2 short detected; active low                           |  |

| 20  | TP2            | OUT             | Test Point 2; leave open                                      |  |

| 22  | VCC            | PWR             | 24 V main voltage supply                                      |  |

| 23  | SEN1           | IN              | Sense input channel 1                                         |  |

| 24  | SEN2           | IN              | Sense input channel 2                                         |  |

| 26  | LP2            | PWR             | Sensor supply channel 1                                       |  |

| 28  | CQ2            | IN/OUT          | IO-Link channel 2                                             |  |

| 30  | LM2            | PWR             | Sensor ground 2                                               |  |

| 31  | LM1            | PWR             | Sensor ground channel 1                                       |  |

| 33  | CQ1            | IN/OUT          | IO-Link channel 1                                             |  |

| 35  | LP1            | PWR             | Sensor supply channel 1                                       |  |

| 37  | GATE2          | OUT             | NMOS gate driver channel 2                                    |  |

| 38  | GATE1          | OUT             | NMOS gate driver channel 1                                    |  |

| 39  | LGND           | PWR             | LED ground                                                    |  |

| 40  | LED2           | IN              | LED driver channel 2                                          |  |

| 41  | LED1           | IN              | LED driver channel 1                                          |  |

| 43  | XTAL1          | IN              | Crystal input; external clock source input                    |  |

| 44  | XTAL2          | OUT             | Crystal feedback                                              |  |

| 46  | TEMP           | OUT             | High temperature indication                                   |  |

| 47  | TP1            | IN              | Test Point 1; internal pull-down; leave open or tie to ground |  |

| 48  | CLK_EN         | IN              | Enable buffered clock feed through; internal pull-down        |  |

# 4 Electrical characteristics

## 4.1 Maximum ratings

Stress(es) beyond those listed under Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the following operational sections of the specifications is not implied. Exposure to maximum rating condition(s) for extended periods may affect device reliability.

### Table 3. Maximum ratings

T<sub>A</sub> = 25 °C ±1.0 °C, unless otherwise specified. All voltages are with respect to ground unless otherwise noted.

| Symbol                 | Rating                                                           |      | Max. | Unit | Notes |

|------------------------|------------------------------------------------------------------|------|------|------|-------|

| Electrical ratings     |                                                                  |      |      |      |       |

| V <sub>CC</sub>        | Supply Voltage - Static                                          | -0.7 | 36   | V    |       |

| P <sub>TOT_QFN48</sub> | Power Dissination, OEN48 Package on Multilayer PCB, Pad soldered |      | 2.0  | W    |       |

| Thermal ratings  |                                         |   |      |     |     |

|------------------|-----------------------------------------|---|------|-----|-----|

|                  | FIT Rate                                | _ | 50   | FIT |     |

| V <sub>ESD</sub> | ESD Voltage<br>• Human Body Model (HBM) | _ | 2000 | V   | (2) |

| LACT_QFN48       | T <sub>AMB</sub> = 60 °C                |   | 2.0  | vv  |     |

Thermal ratings

| T <sub>A</sub>        | Operating Temperature                           | -40 | 85  | °C   |  |

|-----------------------|-------------------------------------------------|-----|-----|------|--|

| TJ                    | Maximum Temperature Junction                    | —   | 150 | °C   |  |

| T <sub>JC_QFN48</sub> | Thermal Resistance Case, Junction to Case       | —   | 0.5 | °C/W |  |

| T <sub>JA_QFN48</sub> | Thermal Resistance Ambient, Junction to Ambient |     | 29  | °C/W |  |

| T <sub>STG</sub>      | Storage Ambient Temperature                     |     | 155 | °C   |  |

| T <sub>SOLDER</sub>   | Lead Soldering Temperature (within 10 s)        |     | 260 | °C   |  |

Notes

2. Human Body Model (HBM) per EIA/JESD22-A114-B for all pins

## 4.2 Electrical characteristics

### Table 4. CM3120 electrical characteristics

Characteristics noted under conditions: Typical values are at  $T_A$  = 25 °C ±1.0 °C, unless otherwise noted.

| Symbol               | Characteristic                                                                   |      | Тур | Max                   | Unit | Notes |

|----------------------|----------------------------------------------------------------------------------|------|-----|-----------------------|------|-------|

| General paramet      | ers                                                                              |      |     |                       |      |       |

| V <sub>CC</sub>      | Main Supply Voltage                                                              |      | 24  | 32                    | V    |       |

| Ivcc                 | Quiescent Current Main Supply                                                    |      | _   | 5.0                   | mA   |       |

| V <sub>DD</sub>      | Pad Supply Voltage                                                               |      | 3.3 | 3.5                   | V    |       |

| I <sub>VDD</sub>     | Quiescent Current Pad Supply                                                     |      |     | 5.0                   | mA   |       |

| IO-link channels     |                                                                                  |      |     |                       |      |       |

| V <sub>CQ</sub>      | Permissible Voltage Range                                                        | -0.3 | —   | V <sub>CC</sub> + 0.3 | V    |       |

| I <sub>CQ_LOAD</sub> | Load or Discharge Current. can be disabled; see CFG1/2 (0x2F/0x4F)<br>on page 25 |      | 10  | 15                    | mA   |       |

| I <sub>CQH</sub>     | DC Driver Current 'H'                                                            | _    | _   | 300                   | mA   |       |

| I <sub>CQL</sub>     | DC Driver Current 'L'                                                            |      | _   | 300                   | mA   |       |

### Table 4. CM3120 electrical characteristics (continued)

Characteristics noted under conditions: Typical values are at T<sub>A</sub> = 25 °C  $\pm$ 1.0 °C, unless otherwise noted.

| Symbol                 | Characteristic                                                                              |                      | Тур                    | Max                  | Unit | Notes |

|------------------------|---------------------------------------------------------------------------------------------|----------------------|------------------------|----------------------|------|-------|

| IO-link channels       | (continued)                                                                                 |                      |                        |                      |      |       |

| V <sub>RESH</sub>      | Residual Voltage 'H', Voltage drop at I <sub>CQH_MAX</sub>                                  | —                    | —                      | 3.0                  | V    |       |

| V <sub>RESL</sub>      | Residual Voltage 'L', Voltage drop at I <sub>CQL_MAX</sub>                                  | —                    | —                      | 3.0                  | V    |       |

| I <sub>PEAKH</sub>     | Output Peak Current 'H', Duration t <sub>PEAK</sub> = 1.0 ms                                | 0.5                  | 1.0                    |                      | А    |       |

| I <sub>PEAKL</sub>     | Output Peak Current 'L', Duration t <sub>PEAK</sub> = 1.0 ms                                | 0.5                  | 1.0                    |                      | А    |       |

| C <sub>LOAD</sub>      | Capacitive Load                                                                             | —                    | 1.0                    |                      | nF   |       |

| t <sub>RISE</sub>      | Output Driver Rise Time, CNOM=1.0 nF                                                        | —                    | —                      | 300                  | ns   |       |

| t <sub>FALL</sub>      | Output Driver Fall Time, CNOM=1.0 nF                                                        | —                    | —                      | 300                  | ns   |       |

| t <sub>BBM</sub>       | Break Before Make Delay                                                                     | —                    | —                      | 50                   | ns   |       |

| t <sub>DETH</sub>      | Input Detection Time 'H'                                                                    | —                    | _                      | 300                  | ns   |       |

| t <sub>DETH</sub>      | Input Detection Time 'L'                                                                    | _                    | _                      | 300                  | ns   |       |

| V <sub>THH_IOL</sub>   | Input Threshold 'H', IO-Link mode; see CFG1/2 (0x2F/0x4F) on page 25                        | 10.5                 | _                      | 13                   | V    |       |

| V <sub>THL_IOL</sub>   | Input Threshold 'L", IO-Link mode; see CFG1/2 (0x2F/0x4F) on page 25                        | 8.0                  | —                      | 11.5                 | V    |       |

| V <sub>HYS_IOL</sub>   | Hysteresis Input Threshold, IO-Link mode; see CFG1/2 (0x2F/0x4F) on page 25                 |                      | 2.0                    | _                    | V    |       |

| V <sub>THH_RAT</sub>   | Input Threshold 'H', Ratiometric mode; see CFG1/2 (0x2F/0x4F) on page 25                    |                      | _                      | _                    | V    |       |

| V <sub>THL_RAT</sub>   | Input Threshold 'L', Ratiometric mode; see CFG1/2 (0x2F/0x4F) on page 25                    |                      | _                      | 0.4 V <sub>CC</sub>  | V    |       |

| V <sub>HYS_RAT</sub>   | Hys_RAT Hysteresis Input Threshold, Ratiometric mode; see CFG1/2 (0x2F/<br>0x4F) on page 25 |                      | 0.0125 V <sub>CC</sub> | _                    | V    |       |

| NMOS gate drive        | rs                                                                                          |                      |                        |                      |      |       |

| t <sub>GATE_ON</sub>   | On Switching Time, CGATE = 1.0 nF                                                           | —                    | 1.0                    |                      | ms   |       |

| t <sub>GATE_OFF</sub>  | Off Switching Time, CGATE = 1.0 nF                                                          | —                    | 10                     |                      | μs   |       |

| V <sub>GATE</sub>      | Output Voltage, VCC $\geq$ 15 V                                                             | V <sub>CC</sub> +4.0 | —                      | V <sub>CC</sub> +8.0 | V    |       |

| C <sub>GATE</sub>      | External Capacitance                                                                        | —                    | 1.0                    | _                    | nF   |       |

| I <sub>TGSL</sub>      | Transistor Leakage Current, Gate to Source (external NMOS)                                  | —                    | —                      | 1.0                  | μA   |       |

| Oscillator             |                                                                                             |                      |                        |                      |      |       |

| fosc                   | Frequency, External crystal                                                                 | —                    | 14,7456                | —                    | MHz  |       |

| t <sub>OSC_START</sub> | Startup Time                                                                                | —                    | 30                     |                      | ms   |       |

| t <sub>OSC_RISE</sub>  | Rise Time                                                                                   | —                    | 5.0                    |                      | ns   |       |

| t <sub>OSC_FALL</sub>  | Fall Time                                                                                   | —                    | 5.0                    |                      | ns   |       |

| C <sub>OUT_MAX</sub>   | CLK Pin Driving Capability                                                                  | —                    | —                      | 15                   | pF   |       |

| Digital pads           |                                                                                             |                      |                        |                      |      |       |

| V <sub>INH</sub>       | Input Voltage 'H'                                                                           | 0.7 V <sub>DD</sub>  | —                      | —                    | V    |       |

| V <sub>INL</sub>       | Input Voltage 'L'                                                                           | —                    | —                      | 0.3 V <sub>DD</sub>  | V    |       |

| V <sub>IHYST</sub>     | Input Hysteresis                                                                            | —                    | 340                    | —                    | mV   |       |

| C <sub>IN</sub>        | Input Capacitance                                                                           | —                    | 5.0                    | —                    | pF   |       |

| I <sub>ILEAK</sub>     | Input Leakage Current, No pull-up/pull-down                                                 | -1.0                 | —                      | 1.0                  | μA   |       |

### Table 4. CM3120 electrical characteristics (continued)

Characteristics noted under conditions: Typical values are at T<sub>A</sub> = 25 °C  $\pm$ 1.0 °C, unless otherwise noted.

| Symbol                 | Symbol Characteristic                                                                |                     | Тур  | Max                  | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------------|---------------------|------|----------------------|------|-------|

| Digital pads (con      | tinued)                                                                              |                     |      |                      |      | 1     |

| V <sub>OUTH</sub>      | Output Voltage 'H'                                                                   | 0.8 V <sub>DD</sub> | —    | —                    | V    |       |

| V <sub>OUTL</sub>      | Output Voltage 'L'                                                                   | _                   |      | 0.4                  | V    |       |

| I <sub>OLEAK</sub>     | Output Leakage Current, Tri-state Active                                             | _                   | _    | 1.0                  | μA   |       |

| C <sub>OUT</sub>       | Output Capacitance                                                                   | _                   | -5.0 | —                    | pF   |       |

| I <sub>OUT</sub>       | Output Driving Current                                                               | 6.0                 |      | —                    | mA   |       |

| I <sub>IH</sub>        | Weak Pull-up Current, V <sub>IN</sub> = 0 V                                          | _                   | -30  | —                    | μA   |       |

| I <sub>IL</sub>        | Weak Pull-down Current, V <sub>IN</sub> = V <sub>DD</sub>                            | _                   | 30   | —                    | μA   |       |

| Serial peripheral      | interface                                                                            |                     |      |                      |      |       |

| f <sub>SPI</sub>       | SPI Clock Frequency                                                                  | 1.0                 |      | 20                   | MHz  |       |

| t <sub>SPI_CLK</sub>   | SPI Clock Period                                                                     | 50                  | _    | 1000                 | ns   |       |

| t <sub>SPI_S</sub>     | SPI Start Clock After Select                                                         | 25                  | _    | —                    | ns   |       |

| t <sub>SPI_E</sub>     | SPI End of Select After Clock                                                        | 25                  | _    | —                    | ns   |       |

| t <sub>SPI_I</sub>     | SPI Idle Between Access                                                              | 100                 | _    | —                    | ns   |       |

| Current sensing        |                                                                                      |                     |      |                      |      |       |

| V <sub>EXT_SD</sub>    | Ext. Short Detection Threshold                                                       | _                   | 200  | —                    | mV   |       |

| I <sub>EXT_SD</sub>    | Ext. Short Detection Current, $R_{SHUNT}$ = 500 m $\Omega$                           | _                   | 400  | _                    | mA   |       |

| I <sub>INT_SD</sub>    | Int. Short Detection Current                                                         | _                   | 350  | _                    | mA   |       |

| t <sub>ovlddet</sub>   | Driver Overload Detection Time, Configurable, see Error! Reference source not found. | 0.1                 | _    | 6.4                  | ms   |       |

| tovlddis               | Driver Overload Polling Time, see Error! Reference source not found.                 | 1.0                 |      | 6400                 | ms   |       |

| t <sub>SHORTDET</sub>  | Short-circuit Detection Time, Configurable; see SHRT1/2 (0x22/0x42) on page 19       | 0.1                 | _    | 336                  | ms   |       |

| Monitoring thresh      | nolds                                                                                |                     |      |                      |      |       |

| VCC <sub>OK_MIN</sub>  | Min. Voltage Monitor Threshold                                                       | _                   | 7.5  | _                    | V    |       |

| VCC <sub>OK_MAX</sub>  | Max. Voltage Monitor Threshold                                                       | _                   | 34   | —                    | V    |       |

| VCC <sub>OK_HYST</sub> | Voltage Monitor Hysteresis                                                           | _                   | 0.6  | —                    | V    |       |

| T <sub>INT</sub>       | Temperature Monitor Threshold                                                        | _                   | 125  | 150                  | °C   |       |

| T <sub>INT_HYST</sub>  | Temperature Monitor Hysteresis                                                       | _                   | 10   | —                    | °C   |       |

| LEDs                   |                                                                                      |                     |      |                      |      | 1     |

| V <sub>LED</sub>       | LED Permissible Voltage Range                                                        | -0.3                |      | V <sub>DD</sub> +0.3 |      |       |

| I <sub>LED_5MA</sub>   | LED Current 5.0 mA                                                                   | 4.5                 |      | 5.5                  |      |       |

| I <sub>LED_10MA</sub>  | ED_10MA LED Current 10 mA                                                            |                     | _    | 11                   |      |       |

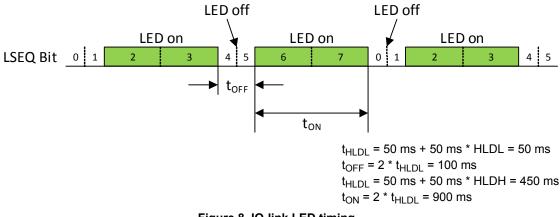

| BITS <sub>LED</sub>    | LED Sequence Bite, Configurable: see LHLD1/2 (0x2E/0x4E) on page                     |                     | 8.0  | _                    |      |       |

| t <sub>HLDL</sub>      | Bit High Hold Time, Configurable; see LHLD1/2 (0x2E/0x4E) on page 25                 | 50                  | _    | 800                  |      |       |

| t <sub>HLDH</sub>      | Bit Low Hold Time, Configurable; see LHLD1/2 (0x2E/0x4E) on page 25                  | 50                  | _    | 800                  |      |       |

# 5 Functional description

## 5.1 Clocking

The IC is clocked by connecting an external 14.7456 MHz quartz at the XTAL1 and XTAL2 pins. It is possible to daisy chain or directly connect multiple CM3120 chips to the CLK pin for clocking. The CLK pin is then connected to the XTAL1 pin of the other chip(s). Clock feed through is enabled by default and can be disabled by pulling the CLK\_EN pin high.

## 5.2 Operational modes

There are three possible operational modes for each CM3120 IO-Link Channels - Standard I/O, UART, and Frame Handler mode. The channel mode can be configured in the MODE register.

## 5.2.1 Standard I/O (SIO)

If a channel is configured in the Standard I/O mode, the mode of the output stage is freely configurable. The SIO register allows the user to choose between an N, P, or Push-Pull driving mode via the DRV bits. The TXEN and TXD bits of this register enable direct control over the output driver. The RXD bit in the MISO status nibble reflects the current state of the CQ pin.

In this mode, it is also possible to control and observe the channel using the TXEN, TXD, and RXD pins. The corresponding pin and register values get logically ORed. Therefore, either the unused pin or register values should be zero, to allow control via the desired interface. Since the sense of TXD to CQ is inverted, it is possible to connect a standard microcontroller UART interface with a high idle state to the TXD/RXD pins.

## 5.2.2 UART

If a channel is configured in UART mode, the output stage is set into Push-Pull mode and the output cannot be controlled via the SIO register or the external pins. It is required to define the used COM speed in the MODE register. By default, the channel listens for incoming UART transactions at the CQ pin. If a character is received, an interrupt is triggered and the data can be read back from the UART register. A transaction is started by writing the data to the UART register. The received UART data is not buffered. Receiving multiple characters, while not reading them back, causes data loss. This is indicated by the OFLW bit in the MISO status nibble.

## 5.2.3 Frame handler

The Frame Handler mode extends the UART interface. Like in UART mode, the output stage is set into Push-Pull mode and the output cannot be controlled via the SIO register or the external pins. It is required to define the used COM speed in the MODE register. It mostly automates the transaction of frames, defined by the IO-Link protocol. Therefore an automated CRC check for incoming and an automated CRC computation for outgoing messages is integrated. The frame handler also monitors the specified timing constraints and takes care to comply with them as well.

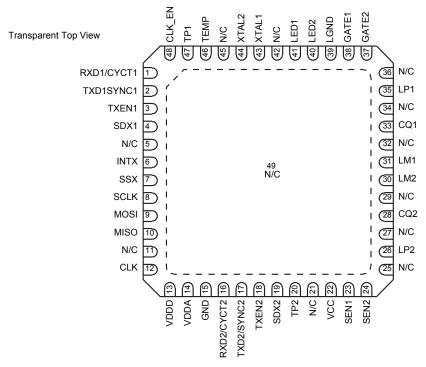

## 5.2.3.1 Device mode

Configured as a device, the frame handler listens for incoming master transactions and triggers an interrupt, if a part or the complete device message is received. The interrupt behavior can be modified using the IMSK and TRSH register. Parity or checksum errors during the transaction is indicated by the MISO status nibble. The received data can be read back via the FHD register by multiple SPI transactions or single/multiple bulk SPI transactions.

After successfully receiving an incoming master message, the frame handler waits for the user to write the complete message data into the frame buffer via the FHD register. This can be done by multiple SPI transactions or by a single bulk SPI transaction. The transaction always starts immediately after the first byte is written into the frame buffer.

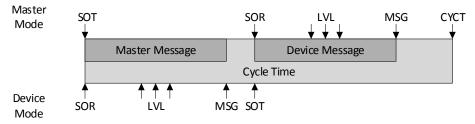

Figure 4. Device mode sequence

## 5.2.3.2 Skip and reset function

It is possible to reset the frame handler or skip an invalid frame from any state. This can be done by writing one to the RST or the SKIP bit of the FHC register. Skipping a frame causes the frame handler to ignore the rest of an incoming message, without triggering any additional interrupt. A soft reset is done after receiving the rest of invalid message or if a timeout was detected. Skipping a frame has no effect on the cycle timer. Resetting a frame immediately resets the frame handler into its idle state and also causes a reset of the cycle timer.

## 5.3 Interrupt handling

The chip utilizes two modes of interrupt handling. The active mode can be switched with the IMODE bit in the INT register. Interrupt mode 1 is active by default.

## 5.3.1 Mode 1

Interrupts are triggered on rising edges of the WURQ, RXRDY, TXRDY, or TOUT bits in the SPI Status. If CQ is configured as an input in SIO mode, interrupts are also triggered on any edge of the RXD bit. Changes of the STATE bits in the SPI Status also trigger interrupts, depending on the IMSK register settings. Trigger conditions can be the start of frame transmission or reception or reaching a defined fill level of the buffer. An interrupt is always triggered after a frame is completely received.

Another trigger condition is any change of values in the STAT register. This is why the microcontroller should always deal with an interrupt by reading back the STAT register. The interrupt is cleared while reading the status register.

## 5.3.2 Mode 2

The interrupt triggering conditions are the same as described in Interrupt mode 1. Mode 2 differs in how interrupts are handled. First, the interrupt origin can be determined by reading the INT register. The interrupt then needs to be actively cleared by the user. This is done by writing a one to the appropriate bit ISTAT, ICH1, or ICH2 in the INT register. The INTX pin remains in its active state until all interrupts are cleared.

## 5.3.3 Interrupt masking

To reduce the amount of triggered interrupts in frame handler mode, the user can deactivate the triggering of interrupts at certain conditions in the IMSK register. All frame handler interrupts are listed in the Table 5.

### Table 5. Frame handler interrupts

| Interrupt | Name                           | Description                                                    |

|-----------|--------------------------------|----------------------------------------------------------------|

| SOT       | Start of Transaction Interrupt | Triggers when the chip starts transmitting its message         |

| SOR       | Start of Reception Interrupt   | Triggers as soon as the chip starts receiving a message        |

| LVL       | Message Level Interrupt        | Triggers if a defined amount of buffered characters is reached |

| MSG       | End of Message Interrupt       | Triggers after the last character of a message was received    |

| CYCT      | Cycle Time Interrupt           | Triggers when the configured cycle time has passed             |

The MSG interrupt is always active. By default, all other interrupts are masked. If the LVL interrupt is active, an interrupt is triggered if the input buffer reaches a defined fill level. The current amount of buffered characters can be queried in the BLVL register. The threshold for buffered characters which triggers the LVL interrupt is configured in the TRSH register.

Figure 5. Interrupt Trigger Positions

It is also possible to mask the short detected (SD) interrupt of the STAT register. Otherwise an interrupt gets triggered as soon as a short is detected.

## 5.4 Protection features

The CM3120 IO-Link Master integrates various features to protect the IO-Link master and connected IO-Link devices. Different configuration options allow the user to take individual safety measures and to prevent damage.

## 5.4.1 Current sensing

## 5.4.1.1 Internal/external mode

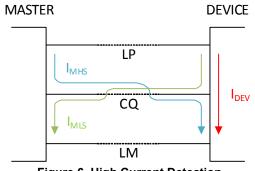

There are two possible methods implemented to detect a high load at the IO-Link supply voltage - an internal and an external current sensing mechanism. Both mechanisms cannot be active at the same time. The user has to choose, which one should be used for each channel. The current sensing mode is configured by the SDINT bit in the CFG register. The SD bit in the STAT register and the SDX pins always reflect the current sensing state.

The internal current sensing mechanism does not need any external circuitry to work, but has the limitation to only detect currents IMHS and IMLS at the CM3120 CQ pin with a fixed current threshold. High currents IDEV from a connected device cannot be detected. Therefore the short protection feature for devices is not feasible in this mode. The usage of an external NMOS transistor is still possible.

The external current sensing can detect high currents IMHS and IMLS at the CQ pin and IDEV of a connected device. External shunts with a typical resistance of 0.5  $\Omega$  needs to be applied for a current threshold of 400 mA. It is possible to adjust the high current detection threshold by changing the shunts resistance value. The voltage drop over the shunt is defined with 200 mV. Current sensing over a shunt and an external NMOS transistor allow the usage of the short protection feature.

### Figure 6. High Current Detection

## 5.4.1.2 Overload/short protection

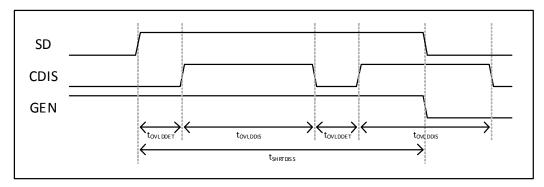

The Overload Protection protects master and device from high loads at the channel output CQ. The output driver of a channel is automatically disabled if high currents are detected for a time >  $t_{OVLDDET}$ . The channel stays disabled and gets re-enabled after a time  $t_{OVLDDIS}$ . If the high load at CQ still persists, the channel is disabled again. This high current polling reduces the power dissipation of the chip and reduces the risk of overheating. The feature can be used in conjunction with the internal and external current sensing. Timing is configured in the OVLD register. It is also possible to disable this feature.

The short protection feature detects shorted or defective devices and disables their power supply, if NMOS transistors are used for power supply switching. If a high current is detected for a time > t<sub>SHRTDIS</sub>, the gate driver gets disabled and the device is powered down. The gate driver stays disabled, but can be switched on again manually by the user. The feature can only be used in conjunction with the external current sensing. Timing is configured in the SHRT register.

Figure 7. Overload/short protection timing

The current state of the channel (CDIS) and the gate driver (GEN) is always reflected in the STAT register. The IO-Link specification allows high currents while powering on a device. To avoid automatic disabling of the gate driver during power-on, t<sub>SHRTDIS</sub> should be configured > 50 ms. Time can be reduced again after the power-on phase.

## 5.4.2 Voltage/temperature monitoring

The chip is equipped with a voltage monitor which observes the VCC supply voltage of the chip and a temperature monitor which observes the die temperature. By default, the chip is configured to automatically disable all channels if the die temperature is too high or the VCC supply voltage is out of range. The monitor states can be read back from the PROT register. The automatic protection feature is also controlled via the PROT register.

## 5.5 Additional IO-link features

## 5.5.1 Automated wake-up

The automated wake-up procedure is started, if the chip is configured in SIO mode and a one is written to the WURQ bit in the SIO register. If the procedure is active, the WURQ bit is set to one and can be aborted by writing a one to the WURQ bit. During the procedure, the chip is set into frame Handler mode and runs the wake-up procedure which complies to the IO-Link standard (CM3120 reference documents on page <u>36</u> - IO-Link Spec v1.1, 7.3.2.2). After the procedure is finished, an interrupt is triggered and the chip stays in IO-Link mode. If a timeout is indicated, the procedure failed. Otherwise the chip is configured and the detected COM mode can be read back using the CFG register.

## 5.5.2 Cycle timer

A cycle timer is available for channels configured as a frame handler in master mode. It enables the user to comply with the configured IO-Link cycle times without further effort. The cycle time is set up in the CYCT register. The format of this register resembles the defined structure in the IO-Link.

It is possible to configure cycle times that are shorter than 400 µs. Although this is not recommended, since the standard states 400 µs as minimum cycle time (CM3120 reference documents on page <u>36</u> - IO-Link Spec v1.1, A.3.7). If the register is zero, the cycle timer gets disabled.

When the cycle timer is active, a new master message transaction will not start until the configured cycle time has passed. If the cycle time is over and no new data is available to start the message transaction, the EOC bit in the MISO Status Nibble will indicate the end of a cycle.

It is possible to reset the frame handler without resetting the cycle timer by triggering a soft reset, using the SKIP bit in the FHC register. The cycle timer will be reset together with the frame handler when a hard reset is triggered using the RST bit in the FHC register.

## 5.5.3 Channel synchronization

The CM3120 provides a synchronization feature which can be enabled by the SYNC bit in the FHC register. If enabled, TXD (SYNC) and RXD (CYCT) pins are used for synchronization purposes and do not have their default behavior in frame handler mode. The CYCT pins indicate if the cycle time has passed with a high level. It is also possible to enable the cycle time interrupt for a channel over the CYCT bit in the IMSK register. If this interrupt is enabled the TOUT bit in the MISO status nibble is also used to indicate the end of a cycle.

The channels waits for the start of transmission until a configured cycle time has passed. The output buffer is filled and the SYNC pin is toggled or a synchronization request is triggered over the SYNC register. This requests can be broadcasted to different chips, specifically triggering different channels on each chip by using the SMSK register. This gives a fine granularity for synchronizing channels, even over multiple chips.

| Chip | MODE1/2     | FHC1/2 CYCT1/2 |             | SMSK |

|------|-------------|----------------|-------------|------|

| IC1  | 0h0A / 0h0A | 0h0E / 0h0E    | 0h14 / 0h00 | 0h09 |

| IC2  | 0h0A / 0h0A | 0h0E / 0h0E    | 0h14 / 0h00 | 0h09 |

| IC3  | 0h0A / 0h0A | 0h0E / 0h06    | 0h00 / 0h00 | 0h04 |

### Table 6. Sample configuration

As an example, there are three CM3120 chips with the configurations from Table 6. If a synchronization request is broadcast via the SPI by writing a one to the ST1 bit in the SYNC register, channel 1 from IC1 and IC2 start their transactions as soon as the configured cycle time has passed. If a one is written to the ST2 bit of the sync register, channel 2 of IC1 and IC2 and channel 1 of IC3 start their transactions immediately.

## 5.5.4 LED drivers

The chip integrates an LED driver for each of the two channels. The LEDs are controlled by the LSEQ and LHLD registers. There are various ways of influencing the timing of a blinking sequence. It is also possible to synchronize the LED blinking sequences over each channel or various chips. This is done by writing one to the SYNC registers PRE and LED bits. The user can choose between two driver strengths of 5.0 mA or 10 mA using the ILED bit in the CFG register.

As an example, writing LSEQ 0hCC and LHLD 0h80 resembles the specified blinking sequence for channels operating in IO-Link mode, starting with the "LED off" state (CM3120 reference documents on page <u>36</u> - IO-Link Spec v1.1, 10.9.3).

Figure 8. IO-link LED timing

## 5.6 Serial peripheral interface

## 5.6.1 Transaction format

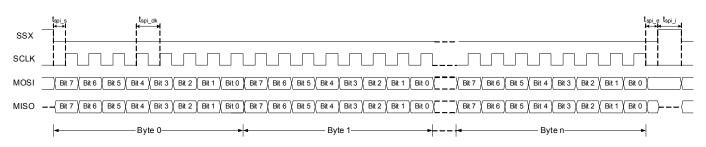

The CM3120 is configured as an SPI slave and uses the CPOL=0, CPHA=0 configuration. During each transaction, a minimum number of two bytes must be transferred. For bulk access to the frame handler buffers via the FHD1/2 registers, n bytes can be transferred. The first byte after a falling SSX edge reflects always the current state of the two channels. The format depends on the configured modes.

Figure 9. SPI timing diagram

## 5.6.2 MOSI format

### Table 7. Mosi Format

| Bit                  | 7 | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|----------------------|---|------|---|----|----|---|---|---|--|--|

| 1 <sup>st</sup> Byte |   | ADR  |   |    |    |   |   |   |  |  |

| 2 <sup>nd</sup> Byte |   | DATA |   |    |    |   |   |   |  |  |

|                      |   |      |   |    |    |   |   |   |  |  |

| n <sup>th</sup> Byte |   |      |   | DA | ТА |   |   |   |  |  |

| ADR  |           | Address for register access                                        |

|------|-----------|--------------------------------------------------------------------|

|      | 0x20-0x3F | Channel 1 registers                                                |

|      | 0x40-0x5F | Channel 2 registers                                                |

|      | 0x60-0x7F | Control registers                                                  |

| RW   |           | Register access type                                               |

|      | 0b0       | write to address                                                   |

|      | 0b1       | read from address                                                  |

| DATA |           | Value for write access                                             |

|      | 0x00-0xFF | $3^{rd}$ -n <sup>th</sup> byte is optional; ignored on read access |

## 5.6.3 MISO format

## Table 8. MISO Format

| Bit                  | 7           | 6    | 5 | 4 | 3 2 1 0 |  |  |  |  |

|----------------------|-------------|------|---|---|---------|--|--|--|--|

| 1 <sup>st</sup> Byte | STAT2 STAT1 |      |   |   |         |  |  |  |  |

| 2 <sup>nd</sup> Byte |             | DATA |   |   |         |  |  |  |  |

|                      |             |      |   |   |         |  |  |  |  |

| n <sup>th</sup> Byte |             | DATA |   |   |         |  |  |  |  |

| STAT1/2 |           | Status code for channel 1/2                                           |

|---------|-----------|-----------------------------------------------------------------------|

|         | 0x0-0xF   | Format is dependent on configured mode                                |

| DATA    |           | Current value on read access to register                              |

|         | 0x00-0xFF | $3^{rd}$ -n <sup>th</sup> byte is optional; not valid on write access |

## 5.6.4 MISO status nibble

### Table 9. MISO status nibble

| Name          | STAT Bit 3 | STAT Bit 2        | STAT Bit 1 | STAT Bit 0 |

|---------------|------------|-------------------|------------|------------|

| Standard I/O  | WURQ       | RXD               | TXEN       | TXD        |

| UART          | OFLW       | RXERR RXRDY TXRDY |            |            |

| Frame Handler | TOUT/EOC   | STATE             |            |            |

| TXD   |       | Current channel output value                             |

|-------|-------|----------------------------------------------------------|

|       | 0b0   | Channel is driven high                                   |

|       | 0b1   | Channel is driven low                                    |

| TXEN  |       | Current output enable state                              |

|       | 0b0   | Channel driver is disable                                |

|       | 0b1   | Channel driver is enabled                                |

| RXD   |       | Current channel input value                              |

|       | 0b0   | Channel input is driven high                             |

|       | 0b1   | Channel input is driven low                              |

| WURQ  |       | Wake-up pulse indicator                                  |

|       | 0b0   | No wake-up pulse is detected                             |

|       | 0b1   | Wake-up pulse is detected                                |

| TXRDY |       | UART transmit state indicator                            |

|       | 0b0   | TX is busy                                               |

|       | 0b1   | TX us ready for transmission                             |

| RXRDY |       | UART receive state indicator                             |

|       | 0b0   | RX is busy                                               |

|       | 0b1   | RX is ready for receiving                                |

| RXERR |       | UART RX parity error                                     |

|       | 0b0   | no parity error detected                                 |

|       | 0b1   | parity error detected                                    |

| OFLW  |       | UART RX overflow indicator                               |

|       | 0b0   | no data overflow detected                                |

|       | 0b1   | data overflow is detected, byte is lost                  |

| STATE |       | Reflects the current frame handler state                 |

|       | 0b000 | ldle                                                     |

|       | 0b001 | transmission output required                             |

|       | 0b010 | transmission active; no further output required          |

|       | 0b011 | transmission active; further output required             |

|       | 0b100 | receiving active                                         |

|       | 0b101 | receiving active; new input available                    |

|       | 0b110 | receiving active; message erroneous                      |

|       | 0b111 | receiving active; message erroneous; new input available |

|       |       |                                                          |

### Table 9. MISO status nibble (continued)

TOUT/EOC

|     | Frame timeout / End of cycle time           |

|-----|---------------------------------------------|

| 0b0 | no timeout detected / cycle time not passed |

| 0b1 | timeout detected / cycle time passed        |

## 5.7 Register description

## 5.7.1 Register overview

### Table 10. Register description

| Address   | Name  | Description                     | Access |

|-----------|-------|---------------------------------|--------|

| 0x00-0x1F | -     | Reserved                        | -      |

| 0x20      | MODE1 | Channel 1 – Mode                | R/W    |

| 0x21      | OVLD1 | Channel 1 – Overload Protection | R/W    |

| 0x22      | SHRT1 | Channel 1 – Short Protection    | R/W    |

| 0x23      | SIO1  | Channel 1 – SIO Control         | R/W    |

| 0x24      | UART1 | Channel 1 – UART Data           | R/W    |

| 0x25      | FHC1  | Channel 1 – FH Control          | R/W    |

| 0x26      | OD1   | Channel 1 – On-Request Length   | R/W    |

| 0x27      | MPD1  | Channel 1 – Master PD Length    | R/W    |

| 0x28      | DPD1  | Channel 1 – Device PD Length    | R/W    |

| 0x29      | CYCT1 | Channel 1 – Cycle Time          | R/W    |

| 0x2A      | FHD1  | Channel 1 – FH Data             | R/W    |

| 0x2B      | BLVL1 | Channel 1 – FH Buffer Level     | R      |

| 0x2C      | IMSK1 | Channel 1 – Interrupt Masking   | R/W    |

| 0x2D      | LSEQ1 | Channel 1 – LED Sequence        | R/W    |

| 0x2E      | LHLD1 | Channel 1 – LED Hold Times      | R/W    |

| 0x2F      | CFG1  | Channel 1 – Configuration       | R/W    |

| 0x30      | TRSH1 | Channel 1 – Threshold Level     | R/W    |

| 0x31-0x3F | -     | Reserved                        | -      |

| 0x40      | MODE2 | Channel 2 – Mode                | R/W    |

| 0x41      | OVLD2 | Channel 2 – Overload Protection | R/W    |

| 0x42      | SHRT2 | Channel 2 – Short Protection    | R/W    |

| 0x43      | SIO2  | Channel 2 – SIO Control         | R/W    |

| 0x44      | UART2 | Channel 2 – UART Data           | R/W    |

| 0x45      | FHC2  | Channel 2 – FH Control          | R/W    |

| 0x46      | OD2   | Channel 2 – On-Request Length   | R/W    |

| 0x47      | MPDL2 | Channel 2 – Master PD Length    | R/W    |

| 0x48      | DPDL2 | Channel 2 – Device PD Length    | R/W    |

| 0x49      | CYCT2 | Channel 2 – Cycle Time          | R/W    |

| 0x4A      | FHD2  | Channel 2 – FH Data             | R/W    |

#### Address Name Description Access BLVL2 0x4B Channel 2 – FH Buffer Level R 0x4C IMSK2 R/W Channel 2 - Interrupt Masking LSEQ2 0x4D Channel 2 – LED Sequence R/W 0x4E LHLD2 Channel 2 – LED Hold Times R/W CFG2 Channel 2 – Configuration R/W 0x4F R/W 0x50 TRSH2 Channel 2 - Threshold Level 0x51-0x5F reserved -IC Status 0x60 STAT R 0x61 SMSK **Channel Synchronization Masks** R/W Synchronization Triggers W 0x62 SYNC 0x63 PROT **Channel Protection** R/W 0x64 INT Interrupt Register R/W 0x65-0x6F Reserved --0x70 REV **Revision Code** R 0x71-0x7F Reserved --

### Table 10. Register description (continued)

## 5.7.2 MODE1/2 (0x20/0x40)

### Table 11. MODE1/2 (0x20/0x40)

| Bit    | 7        | 6 | 5 | 4 | 3     | 2 | 1  | 0  |

|--------|----------|---|---|---|-------|---|----|----|

| Name   | Reserved |   |   |   | COM M |   |    | DE |

| Access | -        |   |   |   | R/    | W | R/ | W  |

Default:0b0000000 MODE Selects the channel operation mode Standard I/O 0b00 0b01 UART 0b10 Frame Handler 0b11 reserved COM Selects the UART communication speed 0b00 Disabled 0b01 COM1 - 4.8 kBd 0b10 COM2 - 38.4 kBd 0b11 COM3 - 230.4 kBd

#### OVLD1/2 (0x21/0x41) 5.7.3

### Table 12. OVLD1/2 (0x21/0x41)

| Bit    | 7    | 6                 | 5                 | 4               | 3   | 2 | 1 | 0 |

|--------|------|-------------------|-------------------|-----------------|-----|---|---|---|

| Name   | A    | DIS               |                   | MULT            |     |   |   |   |

| Access | F    | R/W               |                   |                 | R/\ | N |   |   |

|        |      |                   | C                 | efault:0b100000 | 0   |   |   |   |

| ADIS   |      | Channel overlo    | ad protection mo  | ode             |     |   |   |   |

|        | 0b00 | Disabled          |                   |                 |     |   |   |   |

|        | 0b01 | Enabled; FACT     | ror=10            |                 |     |   |   |   |

|        | 0b10 | Enabled; FACT     | OR=100            |                 |     |   |   |   |

|        | 0b11 | Enabled; FACT     | OR=1000           |                 |     |   |   |   |

| MULT   |      | Multiplier for ov | verload detection | /disable time   |     |   |   |   |

|        | 0-63 | Multiplier value  | •                 |                 |     |   |   |   |

NOTE: disabling this feature may cause damage to master and/or device  $t_{OVLDDET}$  = 100 µs + 100 µs \* MULT  $t_{OVLDDIS}$  =  $t_{OVLDDET}$  \* FACTOR

#### SHRT1/2 (0x22/0x42) 5.7.4

### Table 13. SHRT1/2 (0x22/0x42)

| Bit    | 7    | 6                                   | 5                | 4                        | 3         | 2 | 1 | 0 |  |

|--------|------|-------------------------------------|------------------|--------------------------|-----------|---|---|---|--|

| Name   | BA   | ASE MULT                            |                  |                          |           |   |   |   |  |

| Access | R    | /W                                  |                  |                          | R/        | W |   |   |  |

|        |      |                                     | D                | efault:0b000001          | )1        |   |   |   |  |

| BASE   |      | Base/offset for                     | channel short de | tection time             |           |   |   |   |  |

|        | 0b00 | BASE is 100 µs                      | s; OFFSET is 100 | ) $\mu$ s; disabled if N | IULT is 0 |   |   |   |  |

|        | 0b01 | BASE is 400 µs                      | s; OFFSET is 6.8 | ms                       |           |   |   |   |  |

|        | 0b10 | BASE is 1.6 ms                      | s; OFFSET is 33. | 6 ms                     |           |   |   |   |  |

|        | 0b11 | BASE is 3.2 ms                      | s; OFFSET is 134 | 1.4 ms                   |           |   |   |   |  |

| MULT   |      | Multiplier for short detection time |                  |                          |           |   |   |   |  |

|        | 0-63 | Multiplier value                    | alue             |                          |           |   |   |   |  |

|        |      |                                     |                  |                          |           |   |   |   |  |

NOTE: disabling this feature may cause damage to master and/or device  $t_{SHRTDET}$  = OFFSET + BASE \* MULT

## 5.7.5 SIO1/2 (0x23/0x43)

### Table 14. SIO1/2 (0x23/0x43)

| Bit    | 7    | 6                     | 5                                                          | 4                  | 3               | 2  | 1    | 0   |  |

|--------|------|-----------------------|------------------------------------------------------------|--------------------|-----------------|----|------|-----|--|

| Name   | WURQ |                       | reserved                                                   |                    |                 | RV | TXEN | TXD |  |

| Access | R/W  |                       | -                                                          |                    | R               | /W | R/W  | R/W |  |

|        |      |                       | C                                                          | Default:0b000011   | 00              |    |      |     |  |

| TXD    |      | Driver output va      | alue                                                       |                    |                 |    |      |     |  |

|        | 0b0  | Drive CQ high         |                                                            |                    |                 |    |      |     |  |

|        | 0b1  | Drive CQ low          |                                                            |                    |                 |    |      |     |  |

| TXEN   |      | Driver output st      | Driver output state                                        |                    |                 |    |      |     |  |

|        | 0b0  | Disable output driver |                                                            |                    |                 |    |      |     |  |

|        | 0b1  | Enable output o       | lriver                                                     |                    |                 |    |      |     |  |

| DRV    |      | Driver output m       | ode                                                        |                    |                 |    |      |     |  |

|        | 0b00 | Multiplier value      |                                                            |                    |                 |    |      |     |  |

|        | 0b01 | N-mode                |                                                            |                    |                 |    |      |     |  |

|        | 0b10 | P-mode                |                                                            |                    |                 |    |      |     |  |

|        | 0b11 | Push-Pull             |                                                            |                    |                 |    |      |     |  |

| WURQ   |      | Start/abort auto      | mated wake-up                                              | procedure          |                 |    |      |     |  |

|        | 0b0  | Automated wak         | e-up is not runn                                           | ing; writing 0b1 s | tarts procedure |    |      |     |  |

|        | 0b1  | Automated wak         | Automated wake-up is running; writing 0b1 aborts procedure |                    |                 |    |      |     |  |

## 5.7.6 UART1/2 (0x24/0x44)

### Table 15. UART1/2 (0x24/0x44)

| Bit               | 7 6 5 4 3 2 1 |      |  |  |  |  |  |  |  |  |

|-------------------|---------------|------|--|--|--|--|--|--|--|--|

| Name              |               | DATA |  |  |  |  |  |  |  |  |

| Access            |               | R/W  |  |  |  |  |  |  |  |  |

| Default:0b0000000 |               |      |  |  |  |  |  |  |  |  |

Received/transmitted value over UART

0-255

DATA

. . . . . . . .

read returns received value, write transmits value

## 5.7.7 FHC1/2 (0x25/0x45)

### Table 16. FHC1/2 (0x25/0x45)

| Bit    | 7   | 6                | 5                  | 4                  | 3          | 2   | 1   | 0    |  |  |  |

|--------|-----|------------------|--------------------|--------------------|------------|-----|-----|------|--|--|--|

| Name   | RST | SKIP             | res                | erved              | SYNC       | MAS | CRC | TOUT |  |  |  |

| Access | W   | W                | -                  |                    | R/W        | R/W | R/W | R/W  |  |  |  |

| I      |     | •                | . [                | Default:0b00000    | 110        |     |     | 1    |  |  |  |

| TOUT   |     | Timeout behav    | ior                |                    |            |     |     |      |  |  |  |

|        | 0b0 | Strict timeout d | etection           |                    |            |     |     |      |  |  |  |

|        | 0b1 | Relaxed timeou   | ut detection (+ 3  | t <sub>BIT</sub> ) |            |     |     |      |  |  |  |

| CRC    |     | Automatic chec   | cksum calculation  | n                  |            |     |     |      |  |  |  |

|        | 0b0 | Disabled, send   | ing a master me    | ssage will start i | nmediately |     |     |      |  |  |  |

|        | 0b1 | Enabled          | Enabled            |                    |            |     |     |      |  |  |  |

| MAS    |     | Frame handler    | mode               |                    |            |     |     |      |  |  |  |

|        | 0b0 | Slave mode       |                    |                    |            |     |     |      |  |  |  |

|        | 0b1 | Master mode      |                    |                    |            |     |     |      |  |  |  |

| SYNC   |     | Channel synch    | ronization         |                    |            |     |     |      |  |  |  |

|        | 0b0 | Disabled         |                    |                    |            |     |     |      |  |  |  |

|        | 0b1 | Enabled; maste   | er mode only       |                    |            |     |     |      |  |  |  |

| SKIP   |     | Skip a frame     |                    |                    |            |     |     |      |  |  |  |

|        | 0b1 | Resets frame h   | nandler without re | esetting cycle tin | ne counter |     |     |      |  |  |  |

| RST    |     | Reset frame ha   | andler             |                    |            |     |     |      |  |  |  |

|        | 0b1 | Resets frame h   | andler and cycle   |                    |            |     |     |      |  |  |  |

## 5.7.8 OD1/2 (0x26/0x46)

1-32

### Table 17. OD1/2 (0x26/0x46)

| Bit    | 7 | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|---|------------------------|---|---|---|---|---|---|--|--|

| Name   |   | LEN                    |   |   |   |   |   |   |  |  |

| Access |   | R/W                    |   |   |   |   |   |   |  |  |

|        |   | Default:0b0000001      |   |   |   |   |   |   |  |  |

| LEN    |   | On-Request Data length |   |   |   |   |   |   |  |  |

ΕN

n-Request Data length

Data length in bytes; valid values according to IO-Link spec: 1, 2, 8, 32. See CM3120 reference documents on page 36

#### 5.7.9 MPD1/2 (0x27/0x47)

### Table 18. MPD1/2 (0x27/0x47)

| Bit               | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|---|-----|---|---|---|---|---|---|--|--|

| Name              |   | LEN |   |   |   |   |   |   |  |  |

| Access            |   | R/W |   |   |   |   |   |   |  |  |

| Default:0b0000000 |   |     |   |   |   |   |   |   |  |  |

LEN

Master Process Data length

0-32 Data length in bytes

## 5.7.10 DPD1/2 (0x28/0x48)

### Table 19. DPD1/2 (0x28/0x48)

| Bit    | 7                          | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|----------------------------|-------------------|---|---|---|---|---|---|--|--|

| Name   |                            | LEN               |   |   |   |   |   |   |  |  |

| Access |                            | R/W               |   |   |   |   |   |   |  |  |

|        |                            | Default:0b0000000 |   |   |   |   |   |   |  |  |

| LEN    | Device Process Data length |                   |   |   |   |   |   |   |  |  |

0-32 Data length in bytes

## 5.7.11 CYCT1/2 (0x29/0x49)

### Table 20. CYCT1/2 (0x29/0x49)

| Bit    | 7  | 6  | 5    | 4   | 3 | 2 | 1 | 0 |  |  |  |

|--------|----|----|------|-----|---|---|---|---|--|--|--|

| Name   | BA | SE | MULT |     |   |   |   |   |  |  |  |

| Access | R/ | W  |      | R/W |   |   |   |   |  |  |  |

Default:0b00000000

| BASE |      | Base/offset for cycle time                                   |

|------|------|--------------------------------------------------------------|

|      | 0b00 | BASE is 100 $\mu \text{s};$ no OFFSET; disabled if MULT is 0 |

|      | 0b01 | BASE is 400 μs; OFFSET is 6.4 ms                             |

|      | 0b10 | BASE is 1.6 ms; OFFSET is 32 ms                              |

|      | 0b11 | Reserved                                                     |

| MULT |      | Multiplier for cycle time                                    |

|      | 0-63 | Multiplier value                                             |

|      |      |                                                              |

$t_{CYC}$  = OFFSET + BASE \* MULT

## 5.7.12 FHD1/2 (0x2A/0x4A)

### Table 21. FHD1/2 (0x2A/0x4A)

| Bit               | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------|---|------|---|---|---|---|---|---|--|--|

| Name              |   | DATA |   |   |   |   |   |   |  |  |

| Access            |   | R/W  |   |   |   |   |   |   |  |  |

| Default:0b0000000 |   |      |   |   |   |   |   |   |  |  |

Received/transmitted value over frame handler

0-255

Read returns buffed input data, write buffers output data

## 5.7.13 BLVL1/2 (0x2B/0x4B)

0-64

### Table 22. BLVL1/2 (0x2B/0x4B)

| Bit    | 7   | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|-----|-------------------|---|---|---|---|---|---|--|--|

| Name   |     | FCNT              |   |   |   |   |   |   |  |  |

| Access | R/W |                   |   |   |   |   |   |   |  |  |

|        |     | Default:0b0000000 |   |   |   |   |   |   |  |  |

|        |     |                   |   |   |   |   |   |   |  |  |

FCNT

DATA

Fill count of frame handler input buffer

Current input buffer fill count

## 5.7.14 IMSK1/2 (0x2C/0x4C)

### Table 23. IMSK1/2 (0x2C/0x4C)

| Bit    | 7   | 6                                                                           | 5                                   | 4                   | 3                 | 2        | 1    | 0   |  |  |

|--------|-----|-----------------------------------------------------------------------------|-------------------------------------|---------------------|-------------------|----------|------|-----|--|--|

| Name   |     | reserved                                                                    |                                     | SD                  | SOR               | SOT      | CYCT | LVL |  |  |

| Access |     | -                                                                           |                                     | R/W                 | R/W               | R/W      | R/W  | R/W |  |  |

|        |     |                                                                             | D                                   | efault:0b000111     | 11                | •        |      |     |  |  |

| LVL    |     | Level interrupt                                                             |                                     |                     |                   |          |      |     |  |  |

|        | 0b0 | Enabled; interro                                                            | upt trigger level is                | defined in corre    | sponding TRSH r   | egisters |      |     |  |  |

|        | 0b1 | Disabled; no in                                                             | errupt is triggere                  | d                   |                   |          |      |     |  |  |

| CYCT   |     | Cycle time inter                                                            | rupt                                |                     |                   |          |      |     |  |  |

|        | 0b0 | 0b0 Enabled; interrupt is triggered after end of cycle, only in master mode |                                     |                     |                   |          |      |     |  |  |

|        | 0b1 | Disabled; no in                                                             | Disabled; no interrupt is triggered |                     |                   |          |      |     |  |  |

| SOT    |     | Start of transmi                                                            | ssion interrupt                     |                     |                   |          |      |     |  |  |

|        | 0b0 | Enabled; interro                                                            | upt is triggered or                 | n start of transmis | sion              |          |      |     |  |  |

|        | 0b1 | Disabled; no in                                                             | errupt is triggere                  | d                   |                   |          |      |     |  |  |

| SOR    |     | Start of reception                                                          | on interrupt                        |                     |                   |          |      |     |  |  |

|        | 0b0 | Enabled; interro                                                            | upt is triggered or                 | n start of receptio | n                 |          |      |     |  |  |

|        | 0b1 | Disabled; no in                                                             | errupt is triggere                  | d                   |                   |          |      |     |  |  |

| SD     |     | Short detection                                                             | interrupt                           |                     |                   |          |      |     |  |  |

|        | 0b0 | Enabled; interro                                                            | upt is directly trige               | gered when a sho    | ort gets detected |          |      |     |  |  |

|        | 0b1 | Disabled; no in                                                             | errupt is triggere                  | d                   |                   |          |      |     |  |  |

## 5.7.15 LSEQ1/2 (0x2D/0x4D)

### Table 24. LSEQ1/2 (0x2D/0x4D)

|        | -                     | ,   |   |                  |    |   |   |   |  |  |  |

|--------|-----------------------|-----|---|------------------|----|---|---|---|--|--|--|

| Bit    | 7                     | 6   | 5 | 4                | 3  | 2 | 1 | 0 |  |  |  |

| Name   |                       | SEQ |   |                  |    |   |   |   |  |  |  |

| Access | R/W                   |     |   |                  |    |   |   |   |  |  |  |

|        |                       |     | D | efault:0b0000000 | 00 |   |   |   |  |  |  |

| SEQ    | LED blinking sequence |     |   |                  |    |   |   |   |  |  |  |

|        |                       |     |   |                  |    |   |   |   |  |  |  |

0x00 Always off

0x01-0xFE Blinking; 0b0 represents off-state; 0b1 represents on-state; LSB processed first

0xFF Always on

## 5.7.16 LHLD1/2 (0x2E/0x4E)

### Table 25. LHLD1/2 (0x2E/0x4E)

| Bit    | 7                         | 6                                        | 5                 | 4         | 3    | 2 | 1 | 0 |  |  |

|--------|---------------------------|------------------------------------------|-------------------|-----------|------|---|---|---|--|--|

| Name   |                           | HL                                       | DH                |           | HLDL |   |   |   |  |  |

| Access |                           | R                                        | R                 | /W        |      |   |   |   |  |  |

|        | Default:0b0000000         |                                          |                   |           |      |   |   |   |  |  |

| HLDL   |                           | LED hold time                            | configuration for | off-state |      |   |   |   |  |  |

|        | 0-15 Base time multiplier |                                          |                   |           |      |   |   |   |  |  |

| HLDH   |                           | LED hold time configuration for on-state |                   |           |      |   |   |   |  |  |

t<sub>HLDL</sub> = 50 ms + 50 ms \* HLDL

t<sub>HLDH</sub> = 50 ms + 50 ms \* HLDH

## 5.7.17 CFG1/2 (0x2F/0x4F)

0-15

Base time multiplier

### Table 26. CFG1/2 (0x2F/0x4F)

| Bit    | 7   | 6                                | 5                                                                                                     | 4             | 3        | 2     | 1   | 0   |  |

|--------|-----|----------------------------------|-------------------------------------------------------------------------------------------------------|---------------|----------|-------|-----|-----|--|

| Name   | GEN |                                  | reserved                                                                                              |               | ILED     | SDINT | RAT | ICQ |  |

| Access | R/W |                                  | -                                                                                                     |               | R/W      | R/W   | R/W | R/W |  |

|        |     |                                  | De                                                                                                    | fault:0b00000 | 000      |       |     |     |  |

| ICQ    |     | Current sink                     | configuration f                                                                                       | for C/Q       |          |       |     |     |  |

|        | 0b0 | Current sink                     | disabled                                                                                              |               |          |       |     |     |  |

|        | 0b1 | 10 mA curre                      | nt sink enabled                                                                                       | d             |          |       |     |     |  |

| RAT    |     | Input thresho                    | old configuration                                                                                     | on for C/Q    |          |       |     |     |  |

|        | 0b0 | Static input t<br>page <u>36</u> | Static input threshold according to IO-Link specification. See CM3120 reference docume page <u>36</u> |               |          |       |     |     |  |

|        | 0b1 | Ratiometric i                    | nput threshold                                                                                        | for lower LP  | voltages |       |     |     |  |

| SDINT  |     | Short detecti                    | ion mode                                                                                              |               |          |       |     |     |  |

|        | 0b0 | External sho                     | rt detection; sh                                                                                      | nunt required |          |       |     |     |  |

|        | 0b1 | Internal shor                    | t detection; no                                                                                       | shunt require | d        |       |     |     |  |

| ILED   |     | LED driving                      | current                                                                                               |               |          |       |     |     |  |

|        | 0b0 | 5.0 mA drivir                    | ng current                                                                                            |               |          |       |     |     |  |

|        | 0b1 | 10 mA drivin                     | 10 mA driving current                                                                                 |               |          |       |     |     |  |

| GEN    |     | Gate driver e                    | Gate driver enable                                                                                    |               |          |       |     |     |  |

|        | 0b0 | Disabled                         |                                                                                                       |               |          |       |     |     |  |

|        | 0b1 | Enabled                          |                                                                                                       |               |          |       |     |     |  |

## 5.7.18 TRSH1/2 (0x30/0x50)

0-63

### Table 27. TRSH1/2 (0x30/0x50)

| Bit    | 7   | 6    | 5 4 3 2 |  |  |  | 1 | 0 |  |  |  |

|--------|-----|------|---------|--|--|--|---|---|--|--|--|

| Name   |     | TLVL |         |  |  |  |   |   |  |  |  |

| Access | R/W |      |         |  |  |  |   |   |  |  |  |

|        |     |      |         |  |  |  |   |   |  |  |  |

Default:0b00000000

TLVL

Input buffer threshold level

Trigger interrupt after TLVL received characters; activate in IMSK register

## 5.7.19 STAT (0x60)

### Table 28. STAT (0x60)

| Bit     | 7    | 6                                                        | 5                                                                                           | 4                                | 3   | 2     | 1     | 0   |  |  |  |  |

|---------|------|----------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------|-----|-------|-------|-----|--|--|--|--|