### **General Description**

The MAX13055E-MAX13058E 8-channel, bidirectional level translators provide the level shifting necessary for 100Mbps data transfer in multivoltage systems. The MAX13055E-MAX13058E are ideal for level translation in systems with 8 channels. Externally applied voltages, VCC and VI, set the logic levels on either side of the device. Logic-high signals presented on the VL side of the device appear as a logic-high signal on the VCC side of the device and vice versa.

The MAX13055E-MAX13058E operate at full speed with external drivers that source as little as 4mA output current or larger. Each input/output (I/O) channel is pulled up to VCC or VL by an internal 40µA current source, allowing the MAX13055E-MAX13058E to be driven by either push-pull or open-drain drivers.

The MAX13055E-MAX13058E feature an enable (EN) input to place the device into a low-power shutdown mode when driven low. In addition, the MAX13055E-MAX13058E feature an automatic shutdown mode that disables the part when V<sub>CC</sub> is less than V<sub>L</sub>. Each device has a different I/O  $V_{L_a}$  and I/O  $V_{CC_a}$  state during shutdown mode (see the Ordering Information/Selector Guide).

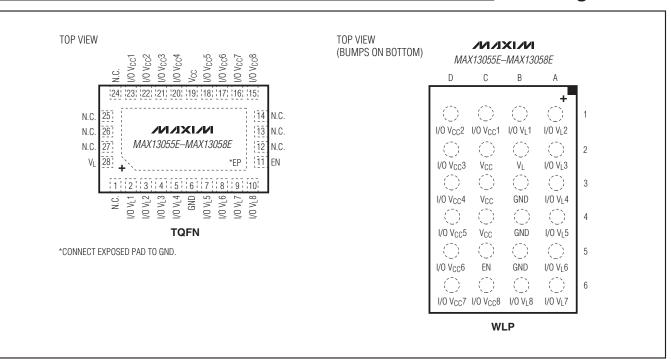

The MAX13055E-MAX13058E operate with VCC voltages from +2.2V to +3.6V and V<sub>I</sub> voltages from +1.62V to +3.2V, making them ideal for data transfer between lowvoltage ASIC/PLDs and higher voltage systems. The MAX13055E-MAX13058E are available in 0.4mm pitch, 24-bump WLP and 28-pin TQFN (3.5mm x 5.5mm) packages. The MAX13055E-MAX13058E operate over the extended -40°C to +85°C temperature range.

### **Applications**

Portable Communication Low-Voltage ASIC Level

Translation **Devices Smart Card Readers** Cell Phones

Camera Modules **GPS**

Portable POS Systems Telecomm Equipment

### **Features**

- ♦ Compatible with 4mA Input Drivers or Larger

- ◆ 100Mbps Guaranteed Data Rate

- ♦ 8 Bidirectional Channels

- ♦  $+1.62V \le V_L \le +3.2V$  and  $+2.2V \le V_{CC} \le +3.6V$ **Supply Voltage Range**

- ♦ 24-Bump WLP (0.4mm Pitch) Lead-Free Package

- ♦ 28-Pin TQFN (3.5mm x 5.5mm) Lead-Free Package

- ♦ Extended ESD Protection on I/O Vcc Lines ±15kV per Human Body Model ±15kV IEC 61000-4-2 Air Discharge ±8kV IEC 61000-4-2 Contact Discharge

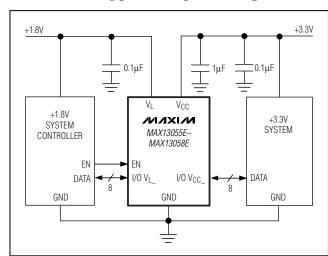

### **Typical Operating Circuit**

Pin Configurations appear at end of data sheet.

## Ordering Information/Selector Guide

| PART          | I/O V <sub>L_</sub> STATE<br>DURING SHUTDOWN | I/O V <sub>CC</sub> _ STATE<br>DURING SHUTDOWN | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------------------------------------|------------------------------------------------|----------------|-------------|

| MAX13055EEWG+ | Open Drain                                   | Open Drain                                     | -40°C to +85°C | 24 WLP      |

| MAX13055EETI+ | Open Drain                                   | Open Drain                                     | -40°C to +85°C | 28 TQFN-EP* |

Ordering Information/Selector Guide continued at end of data sheet.

+Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)                         |                                | Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) (N | Note 1)        |

|-------------------------------------------------------|--------------------------------|-----------------------------------------------------------|----------------|

| V <sub>CC</sub> , V <sub>L</sub>                      | 0.3V to +4.0V                  | 28-Pin TQFN                                               |                |

| EN                                                    | 0.3V to +4.0V                  | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub>   | () (Note 1)    |

| I/O V <sub>CC</sub> 0.3                               | $SV$ to ( $V_{CC} + 0.3V$ )    | 24-Bump WLP                                               | 97°C/W         |

| I/O V                                                 | $.3V \text{ to } (V_L + 0.3V)$ | 28-Pin TQFN                                               | 35°C/W         |

| Short-Circuit Duration                                |                                | Operating Temperature Range                               | 40°C to +85°C  |

| I/O to GND                                            | Continuous                     | Junction Temperature                                      | +150°C         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                                | Storage Temperature Range                                 | 65°C to +150°C |

| 28-Pin TQFN (derate 28.6mW/°C above +70               | 0°C)2286mW                     | Lead Temperature (soldering, 10s)                         | +300°C         |

|                                                       |                                |                                                           |                |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.2V \text{ to } +3.6V, V_L = +1.62V \text{ to } +3.2V, EN = V_L, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3V, V_L = +1.8V, \text{ and } T_A = +25^{\circ}\text{C}.)$  (Notes 2, 3)

| PARAMETER                                                    | SYMBOL             | CONDITIONS                                                         | MIN  | TYP               | MAX | UNITS |

|--------------------------------------------------------------|--------------------|--------------------------------------------------------------------|------|-------------------|-----|-------|

| V <sub>L</sub> Supply Range                                  | VL                 |                                                                    | 1.62 |                   | 3.2 | V     |

| V <sub>CC</sub> Supply Range                                 | Vcc                |                                                                    | 2.2  |                   | 3.6 | V     |

| Supply Current from V <sub>CC</sub>                          | lavcc              | $I/O V_{CC} = V_{CC}$ , $I/O V_{L} = V_{L}$                        |      |                   | 40  | μΑ    |

| Supply Current from V <sub>L</sub>                           | IQVL               | $I/O V_{CC} = V_{CC}$ , $I/O V_{L} = V_{L}$                        |      |                   | 10  | μΑ    |

| V <sub>CC</sub> Shutdown Supply Current                      | ISHDN-VCC          | $T_A = +25$ °C, EN = GND                                           |      | 0.1               | 2   | μΑ    |

| V <sub>L</sub> Shutdown Mode Supply                          | ISHDN-VL           | T <sub>A</sub> = +25°C, EN = GND                                   |      | 0.1               | 1   | μA    |

| Current                                                      |                    | T <sub>A</sub> = +25°C, EN = V <sub>L</sub> , V <sub>CC</sub> = 0V |      | 0.1               | 4   |       |

| I/O Three-State Leakage Current                              | ILEAK              | $T_A = +25^{\circ}C$ , EN = GND                                    |      | 0.1               | 2   | μΑ    |

| EN Input Leakage Current                                     | ILEAK_EN           | $T_A = +25^{\circ}C$                                               |      |                   | 1   | μΑ    |

| $V_L$ - $V_{CC}$ Shutdown Threshold High                     | V <sub>TH</sub> _H | V <sub>CC</sub> rising                                             | 0    | $0.1 \times V_L$  | 8.0 | V     |

| V <sub>L</sub> - V <sub>CC</sub> Shutdown Threshold Low      | V <sub>TH_L</sub>  | V <sub>CC</sub> falling                                            | 0    | $0.12 \times V_L$ | 8.0 | V     |

| I/O V <sub>CC</sub> _ Pulldown Resistance<br>During Shutdown | Rvcc_pd_sd         | MAX13056E/MAX13058E                                                | 10   | 16.5              | 23  | kΩ    |

| I/O VL_ Pulldown Resistance During Shutdown                  | Rvl_pd_sd          | MAX13057E/MAX13058E                                                | 10   | 16.5              | 23  | kΩ    |

| I/O VL_ Pullup Current<br>(Normal Mode)                      | lvl_pu_            | I/O V <sub>L</sub> = GND, I/O V <sub>CC</sub> = GND                | 20   |                   | 65  | μΑ    |

| I/O V <sub>CC</sub> _Pullup Current<br>(Normal Mode)         | lvcc_pu_           | I/O V <sub>CC</sub> _ = GND, I/O V <sub>L</sub> _ = GND            | 20   |                   | 65  | μΑ    |

| I/O V <sub>L</sub> to I/O V <sub>CC</sub> DC Resistance      | RIOVL_IOVCC        |                                                                    |      | 3                 |     | kΩ    |

| ESD PROTECTION                                               |                    |                                                                    |      |                   |     |       |

| All Ports                                                    |                    | Human Body Model                                                   |      | <u>+</u> 2        |     | kV    |

|                                                              |                    | Human Body Model                                                   |      | <u>+</u> 15       |     |       |

| I/O V <sub>CC</sub> _ Only                                   |                    | IEC 61000-4-2 Air-Gap Discharge, C <sub>VCC</sub> = 1µF            |      | <u>+</u> 15       |     | kV    |

|                                                              |                    | IEC 61000-4-2 Contact Discharge, C <sub>VCC</sub> = 1µF            |      | <u>+</u> 8        |     | 1     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.2V \text{ to } +3.6V, V_L = +1.62V \text{ to } +3.2V, EN = V_L, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3V, V_L = +1.8V, \text{ and } T_A = +25^{\circ}\text{C}.)$  (Notes 2, 3)

| PARAMETER                                              | SYMBOL           | CONDITIONS                                                             | MIN                    | TYP | MAX                | UNITS |

|--------------------------------------------------------|------------------|------------------------------------------------------------------------|------------------------|-----|--------------------|-------|

| LOGIC LEVELS                                           | •                | •                                                                      |                        |     |                    | •     |

| I/O V <sub>L_</sub> Input-Voltage High                 | VIHL             | (Note 4)                                                               | V <sub>L</sub> - 0.2   |     |                    | V     |

| I/O V <sub>L</sub> Input-Voltage Low                   | V <sub>ILL</sub> | (Note 4)                                                               |                        |     | 0.15               | V     |

| I/O V <sub>CC</sub> _ Input-Voltage High               | VIHC             | (Note 4)                                                               | V <sub>C</sub> C - 0.4 |     |                    | V     |

| I/O V <sub>CC</sub> _ Input-Voltage Low                | VILC             | (Note 4)                                                               |                        |     | 0.2                | V     |

| EN Input-Voltage High                                  | VIH              |                                                                        | V <sub>L</sub> - 0.4   |     |                    | V     |

| EN Input-Voltage Low                                   | V <sub>IL</sub>  |                                                                        |                        |     | 0.4                | V     |

| I/O V <sub>L_</sub> Output-Voltage High                | Vohl             | I/O V <sub>L</sub> source current = 10µA                               | 4/5 VL                 |     |                    | V     |

| I/O V <sub>L_</sub> Output-Voltage Low                 | Voll             | I/O V <sub>L</sub> sink current = 20µA, I/O V <sub>CC</sub> < 0.1V     |                        |     | 1/5 V <sub>L</sub> | V     |

| I/O V <sub>CC</sub> Output-Voltage High                | Vонс             | I/O V <sub>CC</sub> source current = 10μA                              | 4/5<br>VCC             |     |                    | V     |

| I/O V <sub>CC</sub> _ Output-Voltage Low               | Volc             | I/O V <sub>CC</sub> _ sink current = 20µA, I/O V <sub>L</sub> _ < 0.1V |                        |     | 1/5                | V     |

| RISE/FALL TIME ACCELERATO                              | OR STAGE         |                                                                        | 1                      |     |                    | •     |

| A                                                      |                  | On falling edge                                                        | 3.5                    |     |                    |       |

| Accelerator Pulse Duration                             |                  | On rising edge                                                         |                        |     | ns                 |       |

| V <sub>L</sub> Output Accelerator Source<br>Impedance  |                  | V <sub>L</sub> = 1.62V                                                 |                        | 24  |                    | Ω     |

| V <sub>CC</sub> Output Accelerator Source<br>Impedance |                  | V <sub>CC</sub> = 2.2V                                                 |                        | 13  |                    | Ω     |

| V <sub>L</sub> Output Accelerator Source<br>Impedance  |                  | V <sub>L</sub> = 3.2V                                                  |                        | 11  |                    | Ω     |

| V <sub>CC</sub> Output Accelerator Source Impedance    |                  | V <sub>CC</sub> = 3.6V                                                 |                        | 9   |                    | Ω     |

| V <sub>L</sub> Output Accelerator Sink<br>Impedance    |                  | V <sub>L</sub> = 1.62V                                                 |                        | 14  |                    | Ω     |

| V <sub>CC</sub> Output Accelerator Sink<br>Impedance   |                  | V <sub>CC</sub> = 2.2V                                                 |                        | 11  |                    | Ω     |

| V <sub>L</sub> Output Accelerator Sink<br>Impedance    |                  | V <sub>L</sub> = 3.2V                                                  |                        | 10  |                    | Ω     |

| V <sub>CC</sub> Output Accelerator Sink<br>Impedance   |                  | V <sub>CC</sub> = 3.6V                                                 |                        | 9   |                    | Ω     |

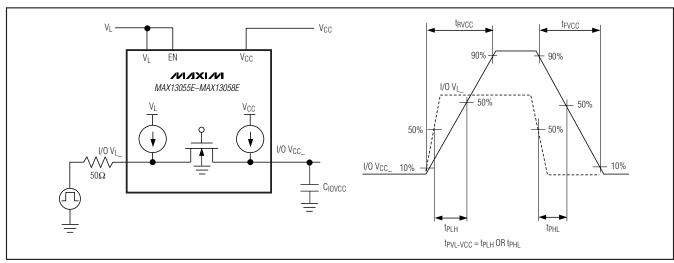

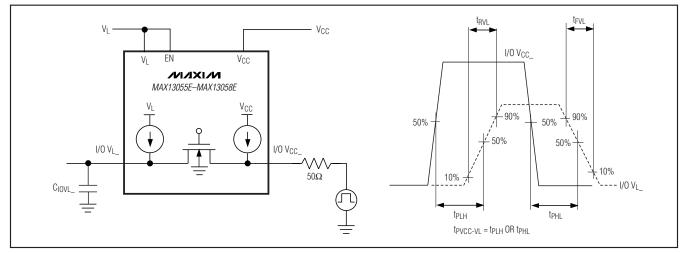

### **TIMING CHARACTERISTICS**

$(+2.2V \leq V_{CC} \leq 3.6V, \ +1.62V \leq V_{L} \leq +3.2V; \ C_{I/OVL} \leq 15 pF, \ C_{I/OVCC} \leq 10 pF; \ R_{SOURCE} < 150\Omega, \ EN = V_{L}, \ T_{A} = -40 ^{\circ}C \ to \ +85 ^{\circ}C, \ unless otherwise noted. Typical values are at V_{CC} = +3.3V, V_{L} = +1.8V, \ and \ T_{A} = +25 ^{\circ}C.) \ (Notes 2, 3)$

| PARAMETER                                                                 | SYMBOL              | CONDITIONS          | MIN | TYP | MAX | UNITS |

|---------------------------------------------------------------------------|---------------------|---------------------|-----|-----|-----|-------|

| I/O V <sub>CC</sub> _ Rise Time                                           | tRVCC               | Figure 2            |     |     | 2.5 | ns    |

| I/O V <sub>CC</sub> _Fall Time                                            | tFVCC               | Figure 2            |     |     | 2.5 | ns    |

| I/O V <sub>L_</sub> Rise Time                                             | t <sub>RVL</sub>    | Figure 1            |     |     | 2.5 | ns    |

| I/O V <sub>L_</sub> Fall Time                                             | t <sub>FVL</sub>    | Figure 1            |     |     | 2.5 | ns    |

| Propagation Delay<br>(Driving I/O V <sub>L</sub> )                        | tpvL-vcc            | Figure 2            | 1   |     | 6.5 | ns    |

| Propagation Delay<br>(Driving I/O V <sub>CC</sub> _)                      | tpvcc-vl            | Figure 1            | 1   |     | 6.5 | ns    |

| Channel-to-Channel Skew                                                   | tskew               |                     |     |     | 2   | ns    |

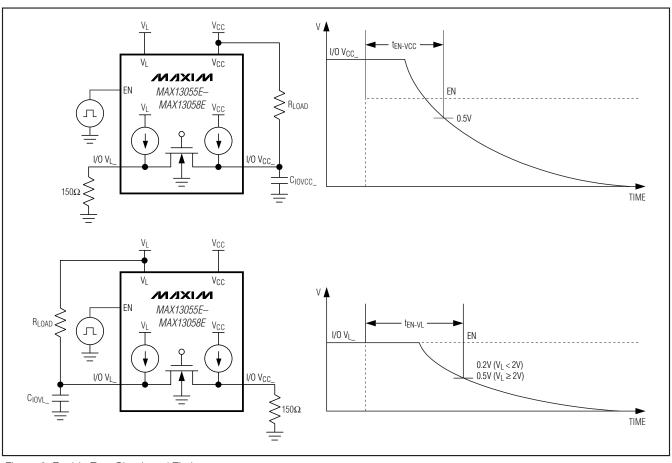

| Propagation Delay from I/O $V_{L_{-}}$ to I/O $V_{CC_{-}}$ After EN       | t <sub>EN-VCC</sub> | Figure 3            |     | 5   |     | μs    |

| Propagation Delay from I/O V <sub>CC</sub> to I/O V <sub>L</sub> After EN | t <sub>EN-VL</sub>  | Figure 3            |     | 5   |     | μs    |

| Maximum Data Data                                                         |                     | Push-pull operation | 100 |     |     | Mhna  |

| Maximum Data Rate                                                         |                     | Open drain          | 1   |     |     | Mbps  |

- **Note 2:** All units are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design and not production tested.

- Note 3: V<sub>L</sub> must be less than or equal to V<sub>CC</sub> during normal operation. However, V<sub>L</sub> can be greater than V<sub>CC</sub> during startup and shutdown conditions. It will not latch up.

- Note 4: For input thresholds, see the rise/fall time accelerator circuit in Figure 4.

## Test Circuits/Timing Diagrams

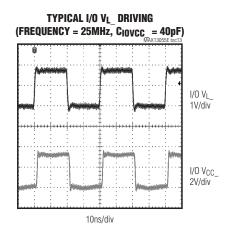

Figure 1. Push-Pull Driving I/O V<sub>L</sub> Test Circuit and Timing

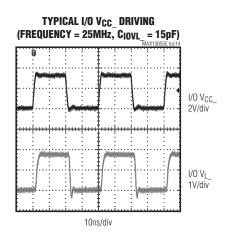

Figure 2. Push-Pull Driving I/O V<sub>CC</sub>\_ Test Circuit and Timing

## Test Circuits/Timing Diagrams (continued)

Figure 3. Enable Test Circuit and Timing

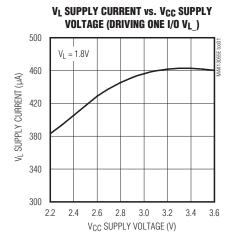

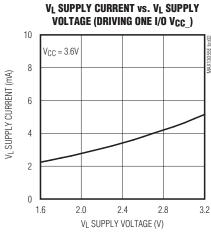

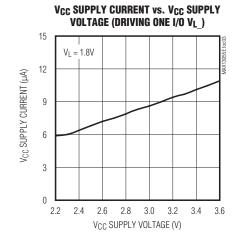

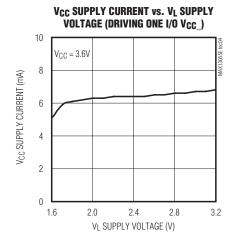

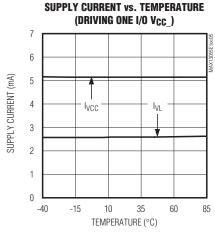

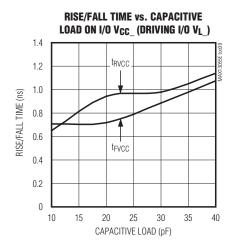

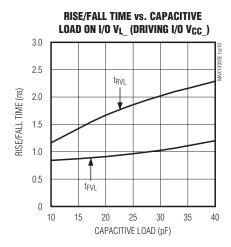

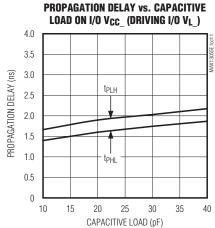

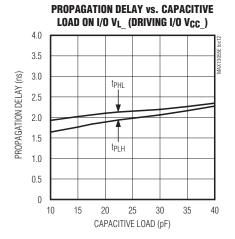

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, V_L = +1.8V, C_{I/OVCC} = 10pF, C_{I/OVL} = 15pF, R_{SOURCE} = 50\Omega, data rate = 100Mbps, push-pull driver, T_A = +25°C, unless otherwise noted.)$

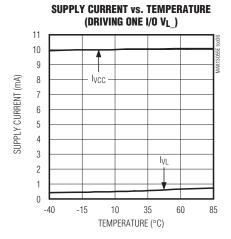

### \_Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, V_L = +1.8V, C_{I/OVCC} = 10pF, C_{I/OVL} = 15pF, R_{SOURCE} = 50\Omega, data rate = 100Mbps, push-pull driver, T_A = +25°C, unless otherwise noted.)$

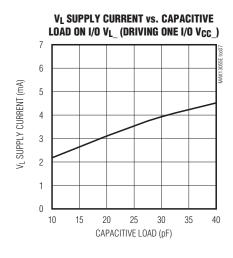

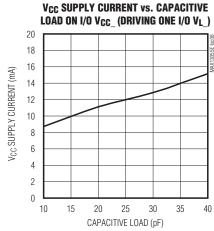

## Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, V_L = +1.8V, C_{I/OVCC} = 10pF, C_{I/OVL} = 15pF, R_{SOURCE} = 50\Omega, data rate = 100Mbps, push-pull driver, T_A = +25°C, unless otherwise noted.)$

## **Pin Description**

| PIN                              |            | NAME                  | FUNCTION                                                                                                                                      |  |

|----------------------------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFN-EP                          | WLP        | NAME                  | FUNCTION                                                                                                                                      |  |

| 1, 12, 13, 14,<br>24, 25, 26, 27 | _          | N.C.                  | No Connection. N.C. is not internally connected.                                                                                              |  |

| 2                                | B1         | I/O V <sub>L</sub> 1  | Input/Output 1 Referenced to V <sub>L</sub>                                                                                                   |  |

| 3                                | A1         | I/O V <sub>L</sub> 2  | Input/Output 2 Referenced to V <sub>L</sub>                                                                                                   |  |

| 4                                | A2         | I/O VL3               | Input/Output 3 Referenced to V <sub>L</sub>                                                                                                   |  |

| 5                                | A3         | I/O VL4               | Input/Output 4 Referenced to V <sub>L</sub>                                                                                                   |  |

| 6                                | B3, B4, B5 | GND                   | Ground                                                                                                                                        |  |

| 7                                | A4         | I/O V <sub>L</sub> 5  | Input/Output 5 Referenced to V <sub>L</sub>                                                                                                   |  |

| 8                                | A5         | I/O VL6               | Input/Output 6 Referenced to VL                                                                                                               |  |

| 9                                | A6         | I/O V <sub>L</sub> 7  | Input/Output 7 Referenced to V <sub>L</sub>                                                                                                   |  |

| 10                               | В6         | I/O VL8               | Input/Output 8 Referenced to V <sub>L</sub>                                                                                                   |  |

| 11                               | C5         | EN                    | Enable Control Input. Drive EN high for normal operation. Drive EN low for shutdown mode.                                                     |  |

| 15                               | C6         | I/O V <sub>CC</sub> 8 | Input/Output 8 Referenced to V <sub>CC</sub>                                                                                                  |  |

| 16                               | D6         | I/O V <sub>CC</sub> 7 | Input/Output 7 Referenced to V <sub>CC</sub>                                                                                                  |  |

| 17                               | D5         | I/O V <sub>CC</sub> 6 | Input/Output 6 Referenced to V <sub>CC</sub>                                                                                                  |  |

| 18                               | D4         | I/O V <sub>CC</sub> 5 | Input/Output 5 Referenced to V <sub>CC</sub>                                                                                                  |  |

| 19                               | C2, C3, C4 | Vcc                   | +2.2V to +3.6V Power-Supply Voltage. Bypass V <sub>CC</sub> with 1µF and 0.1µF ceramic capacitors located as close to the device as possible. |  |

| 20                               | D3         | I/O V <sub>CC</sub> 4 | Input/Output 4 Referenced to VCC                                                                                                              |  |

## Pin Description (continued)

| PI      | N   | NAME                                                               | FUNCTION                                                                                                                               |

|---------|-----|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-EP | WLP | NAME                                                               | FUNCTION                                                                                                                               |

| 21      | D2  | I/O V <sub>CC</sub> 3                                              | Input/Output 3 Referenced to V <sub>CC</sub>                                                                                           |

| 22      | D1  | I/O V <sub>CC</sub> 2 Input/Output 2 Referenced to V <sub>CC</sub> |                                                                                                                                        |

| 23      | C1  | I/O V <sub>CC</sub> 1                                              | Input/Output 1 Referenced to V <sub>CC</sub>                                                                                           |

| 28      | B2  | VL                                                                 | +1.62V to +3.2V Logic-Supply Voltage. Bypass V <sub>L</sub> with a 0.1µF ceramic capacitor located as close to the device as possible. |

| _       | _   | EP                                                                 | Exposed Pad. Connect EP to GND.                                                                                                        |

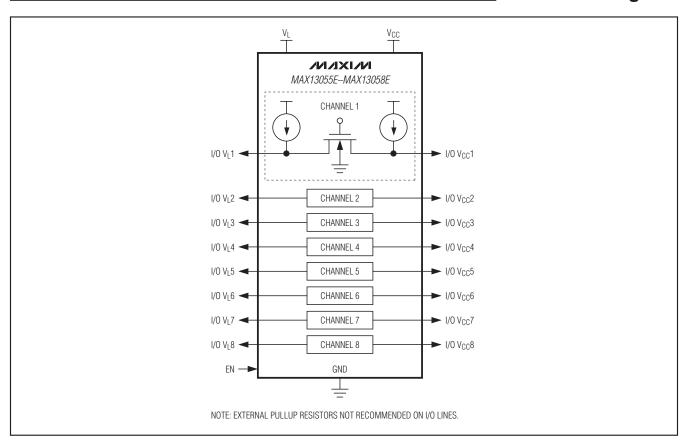

### **Functional Diagram**

### **Detailed Description**

The MAX13055E–MAX13058E 8-channel, bidirectional level translators provide the level shifting necessary for 100Mbps data transfer in multivoltage systems. The MAX13055E–MAX13058E are ideally suited for level translation in systems with 8 channels. Externally applied voltages,  $V_{\rm CC}$  and  $V_{\rm L}$ , set the logic levels on either side of the device. Logic-high signals presented on the  $V_{\rm L}$  side of the device appear as a logic-high signal on the  $V_{\rm CC}$  side of the device and vice versa.

The MAX13055E-MAX13058E operate at full speed with external drivers that source as little as 4mA output current. Each I/O channel is pulled up to VCC or  $V_L$  by an internal 40 $\mu$ A current source, allowing the MAX13055E-MAX13058E to be driven by either pushpull or open-drain drivers.

The MAX13055E–MAX13058E feature an enable (EN) input that places the devices into a low-power shutdown mode when driven low. The MAX13055E–MAX13058E feature an automatic shutdown mode that disables the part when  $V_{\rm CC}$  is less than  $V_{\rm L}$ . The state of I/O  $V_{\rm CC}$  and I/O  $V_{\rm L}$  during shutdown is chosen by selecting the appropriate part version (see the *Ordering Information/Selector Guide*).

The MAX13055E–MAX13058E operate with V<sub>CC</sub> voltages from +2.2V to +3.6V and V<sub>L</sub> voltages from +1.62V to +3.2V.

#### **Level Translation**

For proper operation, ensure that  $+2.2V \le V_{CC} \le +3.6V$ ,  $+1.62V \le V_{L} \le V_{CC}$  - 0.2V. When power is supplied to

$V_L$  while  $V_{CC}$  is missing or less than  $V_L$ , the MAX13055E-MAX13058E automatically enter a low-power mode. The devices also enters shutdown mode when  $V_{EN} = 0V$ . This allows  $V_{CC}$  to be disconnected and still have a known state on I/O  $V_{L-}$ . The maximum data rate depends heavily on the load capacitance (see the Rise/Fall Time vs. Capacitive Load graphs in the *Typical Operating Characteristics*), output impedance of the driver, and the operating voltage range.

#### **Input Requirements**

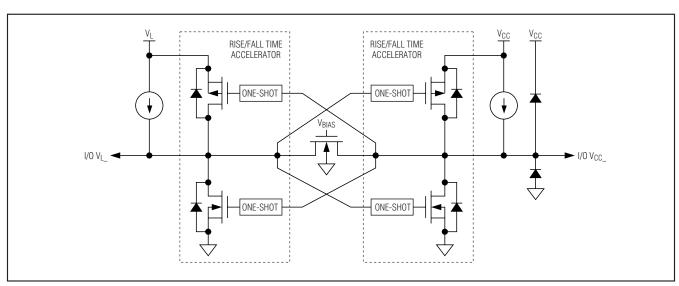

The MAX13055E–MAX13058E architecture is based on an nMOS pass gate and rise/fall time accelerator stages (Figure 4). The accelerators are active only when there is a rising/falling edge on a given I/O. A short pulse is then generated where the output accelerator stages become active and charges/discharges the capacitance at the I/Os. Due to its architecture, both input stages become active during the one-shot pulse. This can lead to current feeding into the external source that is driving the translator. However, this behavior helps to speed up the transition on the driven side.

The MAX13055E–MAX13058E have internal current sources capable of sourcing 40µA to pull up the I/O lines. These internal pullup current sources allow the inputs to be driven with open-drain drivers as well as push-pull drivers. It is not recommended to use external pullup resistors on the I/O lines. The architecture of the MAX13055E–MAX13058E permits either side to be driven with a minimum of 4mA drivers or larger.

Figure 4. Simplified Functional Diagram for One I/O Line

#### **Output Load Requirements**

The MAX13055E–MAX13058E I/O are designed to drive CMOS inputs. Do not load the I/O lines with a resistive load less than  $25k\Omega.$  Do not place an RC circuit at the input of these devices to slow down the edges. If a slower rise/fall time is required, refer to the MAX3000E/MAX3001E logic-level translator data sheet.

#### **Shutdown Mode**

The MAX13055E–MAX13058E feature an enable (EN) input that places the devices into a low-power shutdown mode when driven low. The MAX13055E–MAX13058E feature an automatic shutdown mode that disables the part when V<sub>CC</sub> is unconnected or less than V<sub>L</sub>.

### **Applications Information**

### **Layout Recommendations**

Use standard high-speed layout practices when laying out a board with the MAX13055E-MAX13058E. For example, to minimize line coupling, place all other signal lines not connected to the MAX13055E-MAX13058E at least 1x the substrate height of the PCB away from the input and output lines of the MAX13055E-MAX13058E.

#### **Power-Supply Decoupling**

To reduce ripple and the chance of introducing data errors, bypass  $V_L$  and  $V_{CC}$  to ground with  $0.1\mu F$  ceramic capacitors. Place all capacitors as close to the power-supply inputs as possible. For full ESD protection, bypass  $V_{CC}$  with a  $1\mu F$  ceramic capacitor located as close to the  $V_{CC}$  input as possible.

#### Unidirectional vs. Bidirectional Level Translator

The MAX13055E–MAX13058E bidirectional level translators can operate as a unidirectional device to translate signals without inversion. These devices provide a small solution for unidirectional level translation without inversion.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

### Use with External Pullup/ Pulldown Resistors

Due to the architecture of the MAX13055E-MAX13058E, it is not recommended to use external pullup or pulldown resistors on the bus. In certain applications, the use of external pullup or pulldown resistors is desired to have a known bus state when there is no active driver on the bus. The MAX13055E-MAX13058E include internal pullup current sources that set the bus

state when the device is enabled. In shutdown mode, the state of I/O  $V_{CC}$  and I/O  $V_{L}$  is dependent on the selected part version (see the *Ordering Information/Selector Guide*).

#### **Open-Drain Signaling**

The MAX13055E–MAX13058E are designed to pass open-drain as well as CMOS push-pull signals. When used with open-drain signaling, the rise time is dominated by the interaction of the internal pullup current source and the parasitic load capacitance. The MAX13055E–MAX13058E include internal rise-time accelerators to speed up transitions, eliminating any need for external pullup resistors. For applications such as I<sup>2</sup>C or 1-Wire® that require an external pullup resistor, refer to the MAX3378E and MAX3396E data sheets.

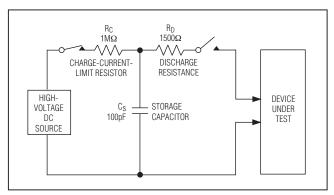

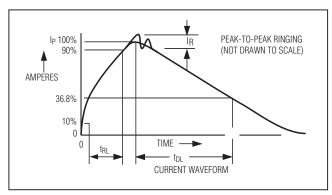

#### **Human Body Model**

Figure 5a shows the Human Body Model and Figure 5b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

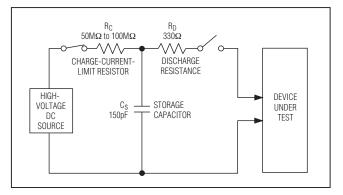

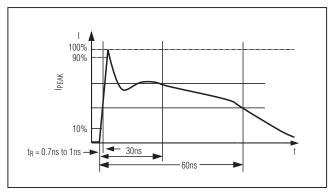

#### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifically refer to integrated circuits. The MAX13055E–MAX13058E help in designing equipment that meets level 4 (the highest level) of IEC 61000-4-2, without the need for additional ESD-protection components. The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2, because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 6a shows the IEC 61000-4-2 model and Figure 6b shows the current waveform for the ±8kV, IEC 61000-4-2, level 4, ESD Contact Discharge Method.

The Air Gap Method involves approaching the device with a charged probe. The Contact Discharge Method connects the probe to the device before the probe is energized.

**Chip Information**

PROCESS: CMOS

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

Figure 5a. Human Body ESD Test Model

Figure 5b. Human Body Current Waveform

Figure 6a. IEC 61000-4-2 ESD Test Model

Figure 6b. IEC 61000-4-2 ESD Generator Current Waveform

### **Ordering Information/Selector Guide (continued)**

| PART            | I/O V∟ STATE<br>DURING SHUTDOWN | I/O V <sub>CC</sub> _ STATE<br>DURING SHUTDOWN | TEMP RANGE     | PIN-PACKAGE |

|-----------------|---------------------------------|------------------------------------------------|----------------|-------------|

| MAX13056EEWG+** | Open Drain                      | 10k $\Omega$ to GND                            | -40°C to +85°C | 24 WLP      |

| MAX13056EETI+** | Open Drain                      | 10k $\Omega$ to GND                            | -40°C to +85°C | 28 TQFN-EP* |

| MAX13057EEWG+** | 10k $\Omega$ to GND             | Open Drain                                     | -40°C to +85°C | 24 WLP      |

| MAX13057EETI+** | 10k $\Omega$ to GND             | Open Drain                                     | -40°C to +85°C | 28 TQFN-EP* |

| MAX13058EEWG+   | 10k $\Omega$ to GND             | 10k $\Omega$ to GND                            | -40°C to +85°C | 24 WLP      |

| MAX13058EETI+   | 10k $\Omega$ to GND             | 10k $\Omega$ to GND                            | -40°C to +85°C | 28 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed pad.

<sup>\*\*</sup>Future product—contact factory for availability.

### **Pin Configurations**

### Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 24 WLP       | W241B2-1     | <u>21-0219</u> |

| 28 TQFN      | T283555-1    | <u>21-0184</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.