# IBM

# IBM PowerPC 970MP RISC Microprocessor User's Manual

Version 2.3

© Copyright International Business Machines Corporation 2005, 2008

All Rights Reserved Printed in the United States of America March 2008

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both:

IBM POWER PowerPC

IBM Logo Power Architecture PowerPC Architecture

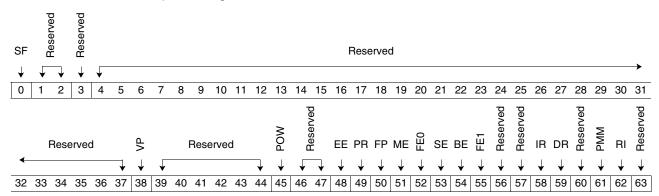

ibm.com

Java and all Java-based trademarks are trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**®

The IBM Semiconductor solutions home page can be found at **ibm.com**/chips

Version 2.3 March 7, 2008

# **Contents**

| List of Figures                                                                     | 13   |

|-------------------------------------------------------------------------------------|------|

| List of Tables                                                                      | 15   |

| Revision Log                                                                        | 19   |

| About This Book                                                                     | 21   |

| Audience                                                                            | . 21 |

| Organization                                                                        | . 21 |

| Related Documents                                                                   | . 22 |

| Companion Manuals                                                                   | . 22 |

| Additional Documentation                                                            |      |

| General PowerPC Documentation                                                       |      |

| Conventions                                                                         | . 25 |

| Acronyms and Abbreviations                                                          | . 26 |

| Terminology Conventions                                                             | . 31 |

| 1. PowerPC 970MP Overview                                                           | 33   |

| 1.1 PowerPC 970MP Microprocessor Overview                                           | 33   |

| 1.2 PowerPC 970MP Functional Units                                                  |      |

| 1.2.1 Introduction                                                                  |      |

| 1.2.1.1 Key Design Fundamentals of the Microprocessor Core                          | 36   |

| 1.2.1.2 Detailed Features of the Microprocessor Core                                |      |

| 1.3 970MP Dual-Core Module                                                          | . 41 |

| 2. Programming Model                                                                | 43   |

| 2.1 970MP Processor Register Set                                                    | . 43 |

| 2.1.1 Architected Registers in the 970MP Implementation                             |      |

| 2.1.1.1 MSR Register (MSR)                                                          | . 49 |

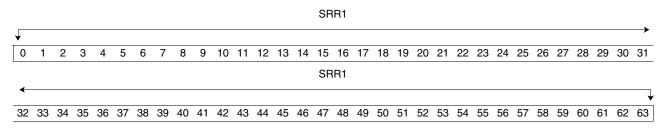

| 2.1.1.2 Machine Status Save/Restore Register (SRR1)                                 | . 49 |

| 2.1.1.3 Time Base and Decrementer (TB, DEC)                                         | . 50 |

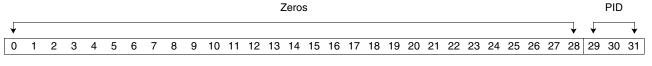

| 2.1.1.4 Processor ID Register (PIR)                                                 |      |

| 2.1.2 PowerPC 970MP-Specific Registers                                              |      |

| 2.1.2.1 Move To and Move From System Register Instructions                          |      |

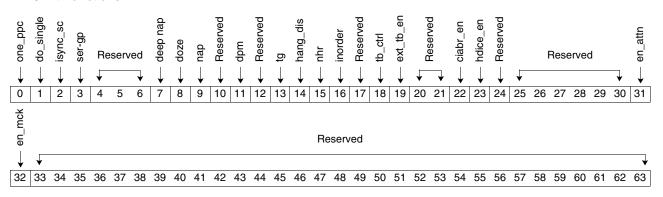

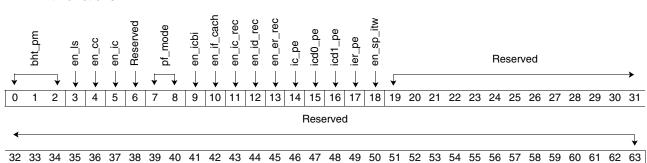

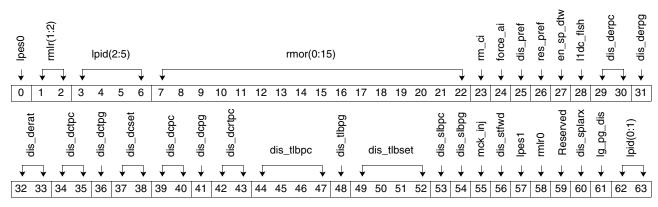

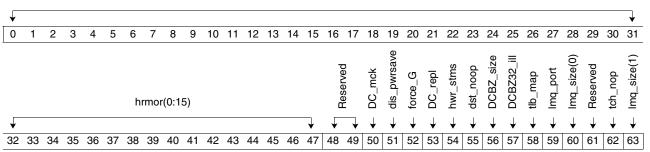

| 2.1.2.2 HID Registers (HID0, HID1, HID4, and HID5)                                  |      |

| 2.1.2.3 Data Address Breakpoint Register (DABR)                                     |      |

| 2.1.2.4 Instruction Address Breakpoint Register (IABR)                              |      |

| 2.1.2.5 Instruction Match CAM Array Access Register (IMC)                           |      |

| 2.1.2.6 Performance Monitor Registers (MMCR0, MMCR1, MMCRA, PMC1-8)                 |      |

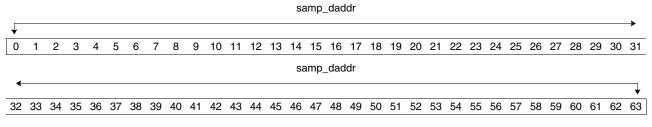

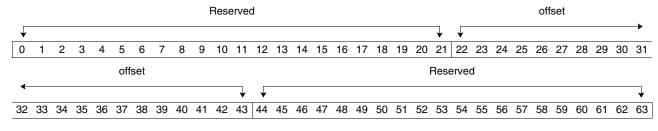

| 2.1.2.7 Sampled Instruction Address and Sampled Data Address Registers (SIAR, SDAR) |      |

| 2.1.2.8 Scan Communication Registers (SCOMC and SCOMD)                              |      |

| 2.1.2.9 Hypervisor Decrementer Interrupt Register (HDEC)                            |      |

| 2.1.2.10 Hypervisor Save/Restore Register (HSRR0, HSRR1)                            |      |

| 2.1.2.11 Hypervisor SPRGs (HSPRG0, HSPRG1)                                          | . 65 |

| 2.1.2.12 Trigger Registers (TRIG0, TRIG1, TRIG2)                                    |    |

|-------------------------------------------------------------------------------------|----|

| 2.1.2.13 Hardware Interrupt Offset Register (HIOR)                                  |    |

| 2.2 Instruction Set Summary                                                         |    |

| 2.2.1 Classes of Instructions                                                       |    |

| 2.2.1.1 Definition of Boundedly Undefined                                           |    |

| 2.2.1.2 Defined Instructions                                                        |    |

| 2.2.1.3 Illegal Instructions                                                        |    |

| 2.2.1.4 Reserved Instructions                                                       |    |

| 2.2.2 Instruction Set Overview                                                      |    |

| 2.2.3 Fixed-Point Processor                                                         |    |

| 2.2.3.1 Fixed-Point Arithmetic and Compare Instructions                             |    |

| 2.2.3.2 Fixed-Point Logical, Rotate, and Shift Instructions                         |    |

| 2.2.3.3 Move to and Move from System Register Instructions                          |    |

| 2.2.3.4 Move to and Move from Machine State Register                                |    |

| 2.2.3.5 Fixed-Point Invalid Forms and Undefined Conditions                          |    |

| 2.2.4 Floating-Point Processor                                                      |    |

| 2.2.4.1 Floating-Point Arithmetic Instructions                                      |    |

| 2.2.4.2 Floating-Point Invalid Forms and Undefined Conditions                       |    |

| 2.2.5 Vector Processor                                                              |    |

| 2.2.6 Load Store Processor                                                          |    |

| 2.2.6.1 Floating-Point Load-and-Store Instructions                                  |    |

| 2.2.6.2 Fixed-Point Load Instructions                                               |    |

| 2.2.6.3 Fixed-Point Store Instructions                                              |    |

| 2.2.6.4 Fixed-Point Load-and-Store Multiple Instructions                            |    |

| 2.2.6.5 Fixed-Point Load-and-Store String Instructions                              |    |

| 2.2.6.6 Load/Store Invalid Forms and Undefined Conditions                           |    |

| 2.2.7 Branch Processor                                                              |    |

| 2.2.7.1 Branch Processor Instructions                                               |    |

| 2.2.7.2 Branch Processor Instructions with Undefined Results                        |    |

| 2.2.7.3 Move To Condition Register Fields Instruction                               |    |

| 2.2.8 Storage Control Instructions                                                  |    |

| 2.2.8.1 Key Aspects of Storage Control Instructions                                 |    |

| 2.2.8.2 Instruction Cache Block Invalidate ( <b>icbi</b> )                          |    |

| 2.2.8.4 Data Cache Block Touch ( <b>dcbt</b> and <b>dcbtst</b> )                    |    |

| 2.2.8.5 Data Cache Block Zero ( <b>dcbt</b> and <b>dcbtst</b> )                     |    |

| 2.2.8.6 Data Cache Block Store ( <b>dcbst</b> )                                     |    |

| 2.2.8.7 Data Cache Block Store ( <b>dcbst</b> )                                     |    |

| 2.2.8.8 Load and Reserve and Store Conditional Instructions (Iwarx/Idarx, stwcx/ste |    |

| 2.2.9 Memory Synchronization Instructions                                           | ,  |

| 2.2.10 Recommended Simplified Mnemonics                                             |    |

| 2.2.10 Neconineraed oimplined whemonics                                             | 01 |

| 3. Storage Subsystem                                                                | 83 |

| 3.1 Storage Hierarchy                                                               | 83 |

| 3.2 Caches                                                                          | 84 |

| 3.2.1 Store Gathering                                                               |    |

| 3.3 Storage Model                                                                   |    |

| 3.3.1 Atomicity                                                                     |    |

| 3.3.2 Storage Access Ordering                                                       |    |

| 3.3.2.1 Storage Access Alignment Support                                            |    |

|    | 3.3.3 Atomic Updates and Reservations               | 86    |

|----|-----------------------------------------------------|-------|

|    | 3.4 Cache Management                                | 87    |

|    | 3.4.1 Flushing the L1 I-Cache                       |       |

|    | 3.4.2 Flushing the L1 D-Cache                       | 87    |

|    | 3.4.3 L2 Cache Disabling and Enabling               | 87    |

|    | 3.4.4 L2 Cache Flushing                             | 87    |

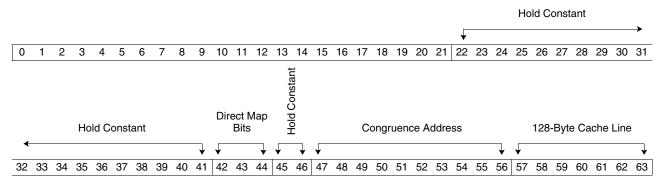

|    | 3.4.4.1 L2 Cache Flush in Direct-Mapped Mode        | 87    |

|    | 3.4.5 L2 Cache Flush Algorithm                      | 88    |

|    | 3.5 Functional Units                                |       |

|    | 3.5.1 Core Interface Unit                           | 91    |

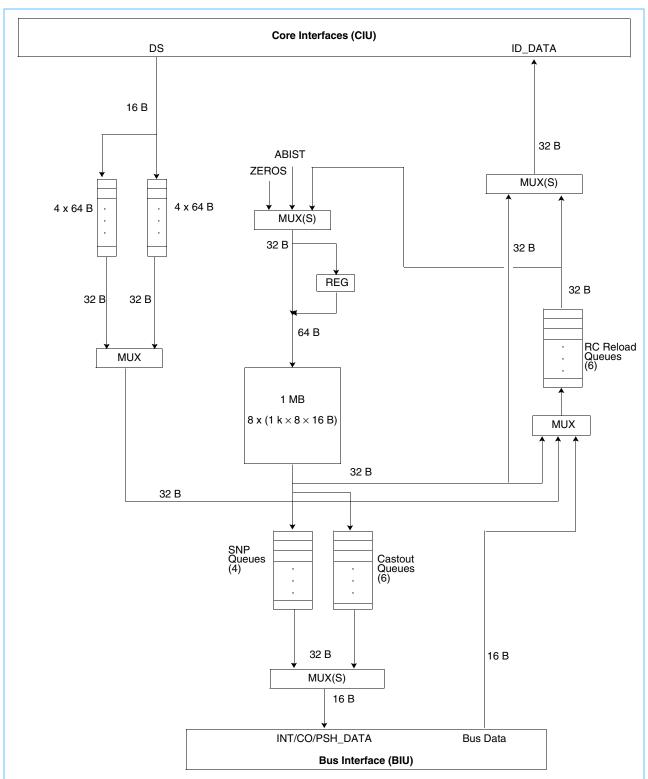

|    | 3.5.2 L2 Cache Controller                           | 91    |

|    | 3.5.2.1 Cache Coherency                             | 93    |

|    | 3.5.2.2 Cache-Coherency Paradoxes                   |       |

|    | 3.5.2.3 Cache State Transition Tables               |       |

|    | 3.5.3 Data Prefetch                                 |       |

|    | 3.5.3.1 Optional dcbt Variant                       |       |

|    | 3.5.3.2 Enhanced <b>dcbt</b> Variant                |       |

|    |                                                     |       |

| 4  | Exceptions                                          | 99    |

| ٠. | 4.1 970MP Microprocessor Exceptions                 |       |

|    | · · · · · · · · · · · · · · · · · · ·               |       |

|    | 4.2 Exception Recognition and Priorities            |       |

|    | 4.2.1 Exception Priorities                          |       |

|    | 4.3 Exception Processing                            |       |

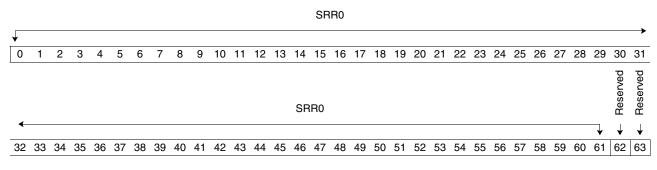

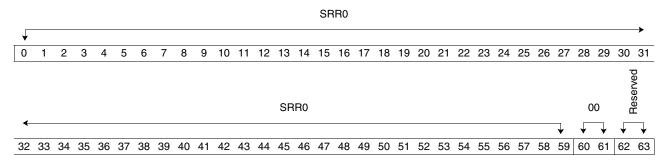

|    | 4.3.1 Machine Status Save/Restore Register 0 (SRR0) |       |

|    | 4.3.2 Machine Status Save/Restore Register 1 (SRR1) |       |

|    | 4.3.3 Machine State Register (MSR)                  |       |

|    | 4.3.4 Enabling and Disabling Exceptions             |       |

|    | 4.3.5 Exception Processing Steps                    |       |

|    | 4.3.6 Setting the Recoverable Exception in the MSR  |       |

|    | 4.3.7 Returning from an Exception Handler           |       |

|    | 4.4 Process Switching                               |       |

|    | 4.5 Exception Definitions                           |       |

|    | 4.5.1 System Reset Exception                        |       |

|    | 4.5.2 Machine Check Exceptions                      |       |

|    | 4.5.3 Data Storage Exception                        |       |

|    | 4.5.4 Data Segment Exception                        |       |

|    | 4.5.5 Instruction Storage Exception                 |       |

|    | 4.5.6 Instruction Segment Exception                 |       |

|    | 4.5.7 External Interrupt Exception                  |       |

|    | 4.5.8 Alignment Exception                           |       |

|    | 4.5.9 Program Exception                             |       |

|    | 4.5.10 Floating-Point Unavailable Exception         |       |

|    | 4.5.11 Decrementer Exception                        |       |

|    | 4.5.12 System Call Exception                        |       |

|    | 4.5.13 Trace Exception                              |       |

|    | 4.5.14 Performance Monitor Exception                |       |

|    | 4.5.15 VPU Unavailable Exception                    |       |

|    | 4.5.16 Instruction Address Breakpoint Exception     | . 11/ |

| 4.5.17 Maintenance Exception                                                            | 117 |

|-----------------------------------------------------------------------------------------|-----|

| 4.5.18 VPU Assist Exception                                                             |     |

| ·                                                                                       |     |

| 5. Memory Management                                                                    | 119 |

| 5.1 MMU Overview                                                                        | 119 |

| 5.1.1 Speculative Storage Accesses                                                      | 120 |

| 5.1.2 Storage Protection                                                                | 121 |

| 5.1.3 Storage Access Modes                                                              | 121 |

| 5.1.4 Support for 32-Bit Operating Systems                                              |     |

| 5.2 Real Addressing Mode                                                                | 122 |

| 6. Software Optimization Guidelines                                                     | 123 |

| 6.1 Design Characteristics                                                              |     |

| 6.2 Software Considerations for the 970MP Microprocessor                                |     |

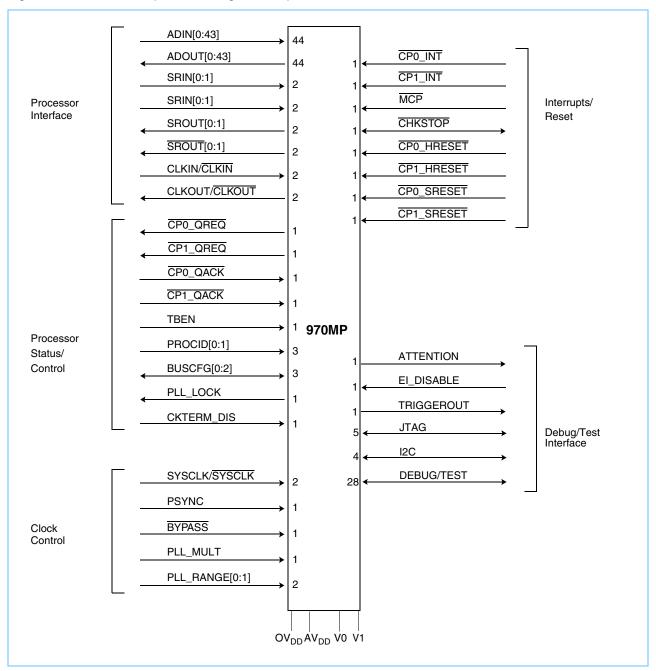

| 7. Signal Description                                                                   | 120 |

| 7.1 Signal Configuration                                                                |     |

| 7.2 Signal Descriptions                                                                 |     |

| 7.2.1 Processor Interface                                                               |     |

| 7.2.1.1 Address/Data In (ADIN[0:43])–Input                                              |     |

| 7.2.1.1 Address/Data in (ADIN[0.43])—Input                                              |     |

| 7.2.1.2 Shoop Response in (Shinto.1), Shinto.1)—input                                   |     |

| 7.2.1.4 Address Data Out (ADOUT[0:43])-Output                                           |     |

| 7.2.1.5 Snoop Response Out (SROUT[0:1], SROUT[0:1])–Output                              | 199 |

| 7.2.1.6 Clock Out (CLKOUT/CLKOUT)-Output                                                | 133 |

| 7.2.2 Processor Status and Control                                                      |     |

| 7.2.2.1 Quiescent Request (CP0_QREQ and CP1_QREQ)—Output                                |     |

| 7.2.2.2 Quiescent Acknowledgment (CP0_QACK and CP1_QACK)-Input                          |     |

| 7.2.2.2 Quiescent Acknowledgment (CFO_QACK and GFT_QACK)-input                          |     |

| 7.2.2.4 Processor ID (PROCID[0:1])–Input                                                |     |

| 7.2.2.5 Bus Configuration Select (BUSCFG[0:2])-Input                                    |     |

| 7.2.2.6 PLL Locked (PLL_LOCK)–Output                                                    |     |

| 7.2.2.7 Clock Receiver Termination (CKTERM_DIS)-Input                                   |     |

| 7.2.3 Clock Control                                                                     |     |

| 7.2.3.1 System Clock (SYSCLK/SYSCLK)-Input                                              |     |

| 7.2.3.2 Phase Synchronization (psync)–Input                                             |     |

| 7.2.3.3 PLL Bypass (BYPASS)—Input                                                       |     |

| 7.2.3.4 PLL Multiplier (PLL_MULT)-Input                                                 |     |

| 7.2.3.5 PLL Range Select (PLL_RANGE[0:1])–Input                                         |     |

| 7.2.4 Interrupts and Resets                                                             |     |

| 7.2.4 Interrupts and resets                                                             |     |

| 7.2.4.2 Machine Check Interrupt (MCP)-Input                                             |     |

| 7.2.4.2 Machine Check interrupt (MCF)—Input  7.2.4.3 Checkstop (CHKSTOP) —Bidirectional |     |

| 7.2.4.4 Hard Reset (CP0_HRESET and CP1_HRESET)-Input                                    |     |

| 7.2.4.5 Soft Reset (CP0_SRESET and CP1_SRESET)-Input                                    |     |

| , – , ,                                                                                 |     |

| 7.2.5 Debug/Test Interface                                                              |     |

| 7.2.5.1 Attention (ATTENTION)-Output                                                    |     |

| · · · · · · · · · · · · · · · · · · ·                                                   |     |

| 7.2.5.3 Trigger Out (TRIGGEROUT)-Output                                                 | 13/ |

|    | 7.2.5.4 JTAG Signals                                            | . 137 |

|----|-----------------------------------------------------------------|-------|

|    | 7.2.5.5 I <sup>2</sup> C Signals                                |       |

|    | 7.2.6 Voltage and Ground                                        |       |

| R  | Processor Interconnect Bus                                      | 139   |

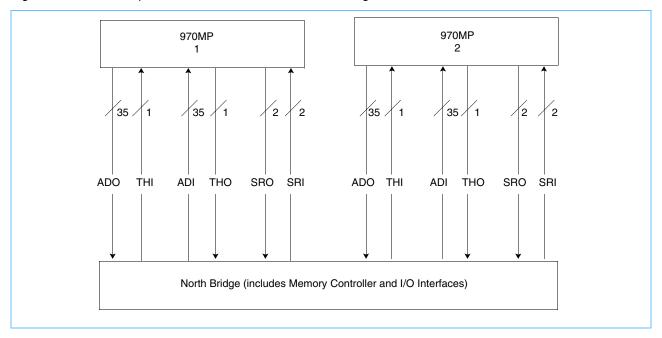

| ٠. | 8.1 Overview                                                    |       |

|    | 8.1.1 Packets                                                   |       |

|    | 8.1.2 Bus Segments                                              |       |

|    | 8.1.2.1 Address/Data Bus Segment                                |       |

|    | 8.1.2.2 Transfer-Handshake Bus Segment                          |       |

|    | 8.1.2.3 Snoop-Response Bus Segment                              |       |

|    | 8.1.3 Transactions                                              |       |

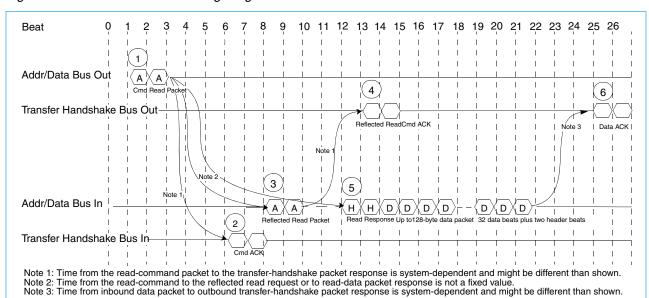

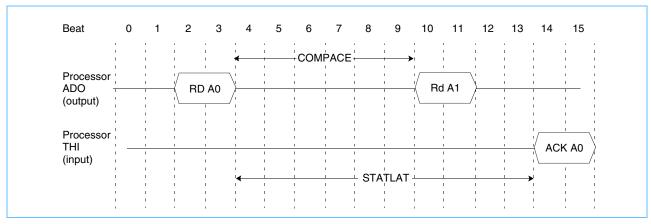

|    | 8.1.3.1 Read Transaction                                        |       |

|    |                                                                 |       |

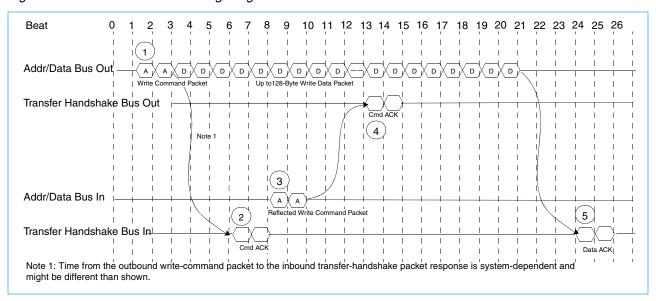

|    | 8.1.3.2 Write Transaction                                       |       |

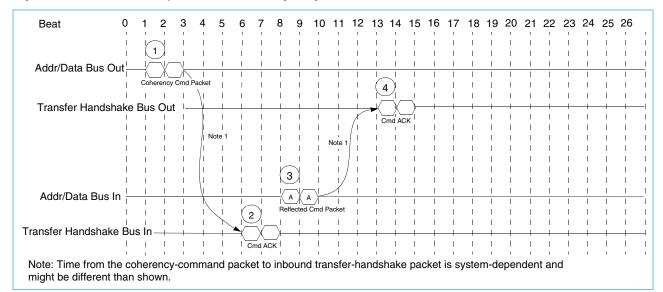

|    | 8.1.3.3 Command-Only Transaction                                |       |

|    | 8.1.4 Memory and Cache Coherency                                |       |

|    | 8.1.4.1 Physical Memory Size                                    |       |

|    | 8.1.4.2 Coherency Protocol                                      |       |

|    | 8.1.4.3 Coherency Block Size                                    |       |

|    | 8.2 Packet Transfer Protocol                                    |       |

|    | 8.2.1 Command Packet Definition                                 |       |

|    | 8.2.1.1 Address Modifiers                                       |       |

|    | 8.2.1.2 Transfer Type Field                                     |       |

|    | 8.2.1.3 Tag Definition                                          |       |

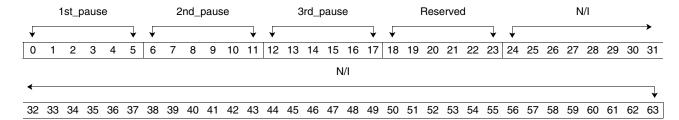

|    | 8.2.1.4 Command Pacing                                          |       |

|    | 8.2.2 Data Packet Definition                                    |       |

|    | 8.2.2.1 Two-Beat Transfers                                      | . 153 |

|    | 8.2.2.2 Multi-Beat Transfers                                    |       |

|    | 8.2.3 Transfer-Handshake Packets                                | . 155 |

|    | 8.2.3.1 Null Transfer Handshake                                 | . 156 |

|    | 8.2.3.2 Transfer-Handshake Acknowledgment                       | . 156 |

|    | 8.2.3.3 Transfer-Handshake Retry                                | . 157 |

|    | 8.2.3.4 Transfer-Handshake Parity Error                         | . 158 |

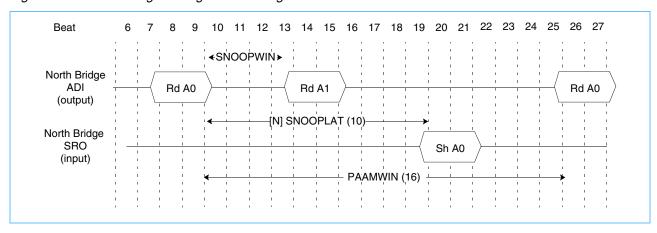

|    | 8.3 Snoop Responses                                             | . 158 |

|    | 8.3.1 Snoop-Response Bus Implementation                         |       |

|    | 8.3.2 Snoop-Response Descriptions                               |       |

|    | 8.3.2.1 SResp Retry Response Code (Priority 1 - highest)        |       |

|    | 8.3.2.2 SResp Modified-Intervention Response Code (Priority 2)  |       |

|    | 8.3.2.3 SResp Shared-Intervention Response Code (Priority 3)    |       |

|    | 8.3.2.4 SResp Modified Response Code (Priority 4)               |       |

|    | 8.3.2.5 SResp Shared Response Code (Priority 5)                 |       |

|    | 8.3.2.6 SResp Null or Clean Response Code (Priority 6 - lowest) |       |

|    | 8.4 Bus Transactions                                            |       |

|    | 8.4.1 Terms                                                     |       |

|    |                                                                 |       |

|    | 8.4.2 Memory Read Transactions (General)                        |       |

|    | 8.4.2.1 Read Transaction                                        |       |

|    | 8.4.2.2 Read with No Intent to Cache Transaction                |       |

|    | 8.4.2.3 Read with Intent to Modify Burst Transaction            |       |

|    | 8.4.2.4 LARX-Reserve Transaction                                | . 166 |

|    | 8.4.3 Memory Write Transactions (General)                  | 167 |

|----|------------------------------------------------------------|-----|

|    | 8.4.3.1 Write-With-Kill Transaction                        |     |

|    | 8.4.3.2 Write-With-Clean Transaction                       | 168 |

|    | 8.4.3.3 Write-With-Flush Transaction                       | 168 |

|    | 8.4.4 Command-Only Transactions                            | 168 |

|    | 8.4.4.1 DCLAIM Transaction (Invalidate Others)             | 168 |

|    | 8.4.4.2 Flush Transaction                                  | 169 |

|    | 8.4.4.3 Clean Transaction                                  | 169 |

|    | 8.4.4.4 IKill Transaction                                  | 169 |

|    | 8.4.4.5 TLBIE Transaction                                  |     |

|    | 8.4.4.6 TLBSYNC Transaction                                |     |

|    | 8.4.4.7 SYNC Transaction                                   |     |

|    | 8.4.4.8 EIEIO Transaction                                  | 171 |

|    | 8.4.4.9 Null Transaction                                   | 171 |

| 9. | . Power and Thermal Management                             | 173 |

|    | 9.1 Definitions                                            |     |

|    | 9.1.1 Full Power Mode                                      |     |

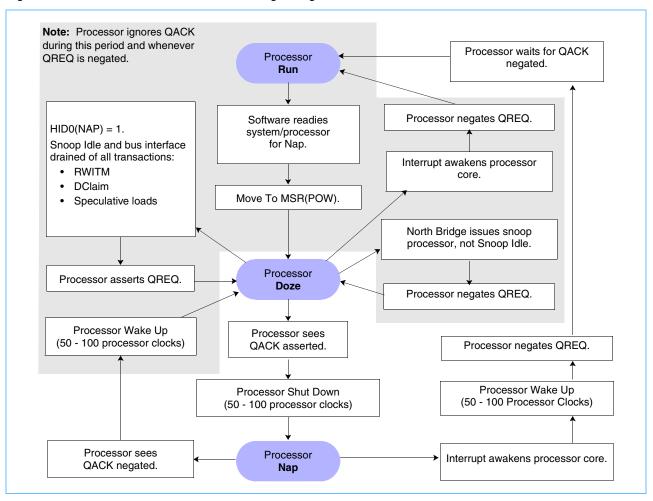

|    | 9.1.2 Doze Mode                                            |     |

|    | 9.1.3 Nap Mode                                             |     |

|    | 9.1.4 Deep Nap Mode                                        |     |

|    | 9.1.5 Dynamic Power Management                             |     |

|    | 9.2 Power-Management Support                               |     |

|    | 9.2.1 Power-Management Control Bits                        |     |

|    | 9.2.2 Interrupts                                           |     |

|    | 9.2.3 Bus Snooping                                         |     |

|    | 9.2.3.1 Delay Calculation                                  | 178 |

|    | 9.2.4 Thermal Diodes                                       |     |

|    | 9.2.5 Bus States while in Power Saving Modes               | 179 |

|    | 9.3 Software Considerations for Power Management           | 180 |

|    | 9.3.1 Entering Power Saving Mode                           |     |

|    | 9.3.2 External Interrupt Enable                            | 180 |

|    | 9.4 Power Tuning Facility Overview                         | 181 |

|    | 9.4.1 Power Tuning Facility Definitions                    |     |

|    | 9.4.2 Power Modes                                          | 183 |

|    | 9.4.3 Power Transition Latencies                           | 186 |

|    | 9.4.3.1 Idle to Run Transitions                            | 187 |

|    | 9.4.3.2 Exiting Deep Nap Using a Decrementer Interrupt     | 188 |

|    | 9.4.3.3 Frequency Transitions in the Power Tuning Facility | 188 |

|    | 9.5 PLL Design                                             | 189 |

|    | 9.6 Time-Base and Decrementer Registers                    |     |

|    | 9.7 I <sup>2</sup> C Bus Interface                         |     |

|    | 9.8 Frequency and Voltage Scaling                          |     |

|    | 9.8.1 Frequency Scaling                                    |     |

|    | 9.8.1.1 Initiating a Frequency Change                      |     |

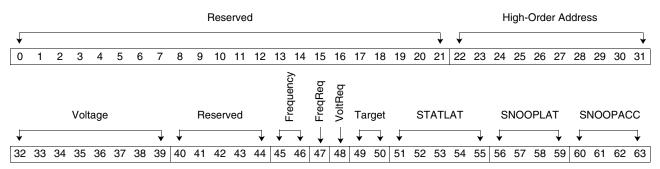

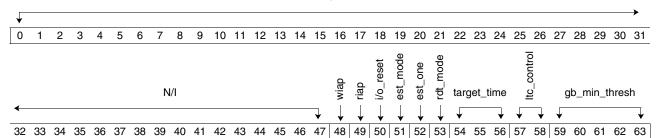

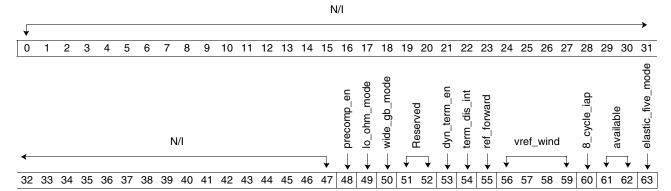

|    | 9.8.1.2 Power Control Register                             |     |

|    | 9.8.1.3 Power Control Register High (PCRH)                 |     |

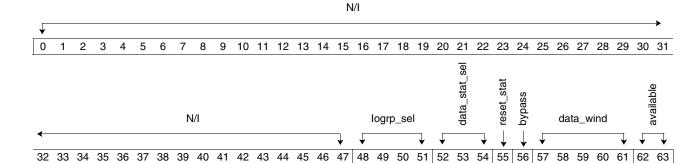

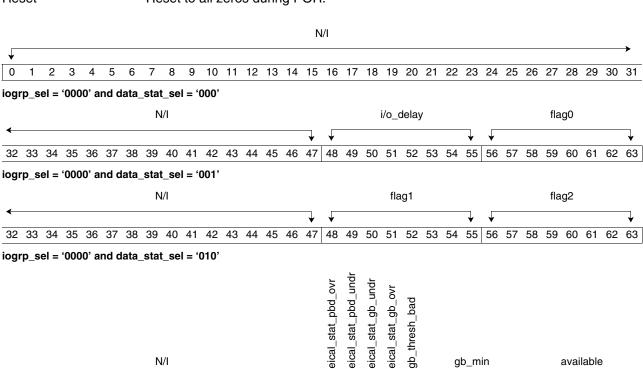

|    | 9.8.1.4 Power Status Register                              |     |

|    | 9.8.2 Power Adjustment Bus Transaction                     |     |

|    |                                                            |     |

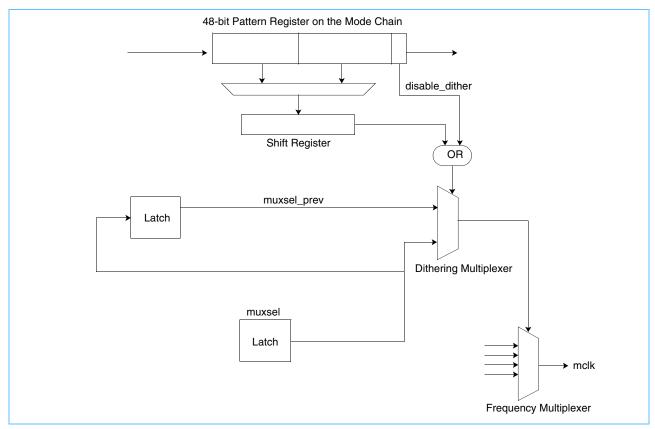

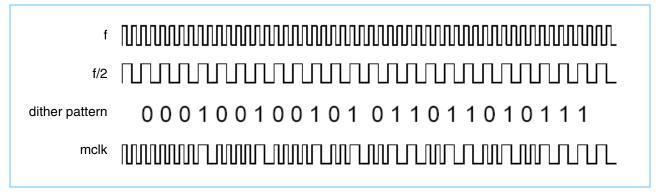

|     | 9.8.3 Clock Dithering                                                                       | 200 |

|-----|---------------------------------------------------------------------------------------------|-----|

|     | 9.8.4 Voltage Scaling                                                                       |     |

|     | 9.8.5 Frequency and Voltage Scaling Latencies                                               | 202 |

|     | 9.9 Reducing Clock Mesh Power                                                               | 203 |

|     | 9.9.1 Power Saving in Deep Nap                                                              | 203 |

|     | 9.10 Additional Dynamic Power Management                                                    | 204 |

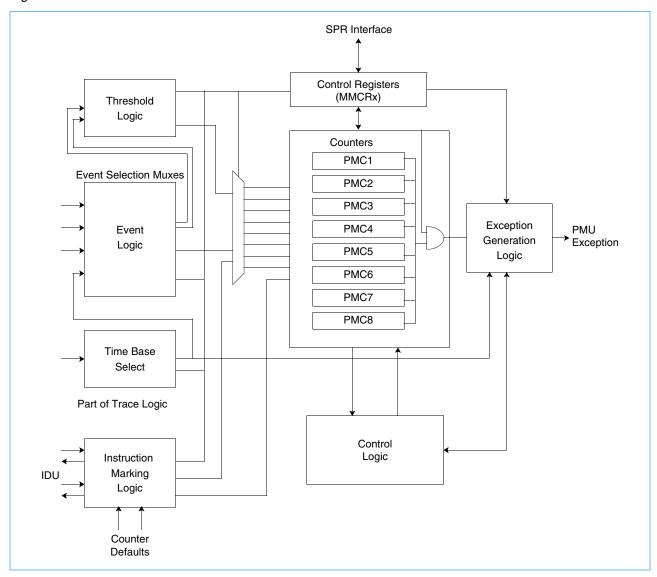

| 10  | . 970MP Performance Monitor                                                                 | 205 |

| 10. |                                                                                             |     |

|     | 10.1 Instrumentation Facilities Overview                                                    |     |

|     | 10.1.1 Performance Monitor Facilities                                                       |     |

|     |                                                                                             |     |

|     | 10.1.3 Machine States and Enabling the Performance Monitor Counters                         |     |

|     | 10.1.4 Trigger Events and Enabling the Performance Monitor Counters                         |     |

|     | 10.1.5 Performance Monitor Exceptions                                                       |     |

|     | 10.1.6 Sampling                                                                             |     |

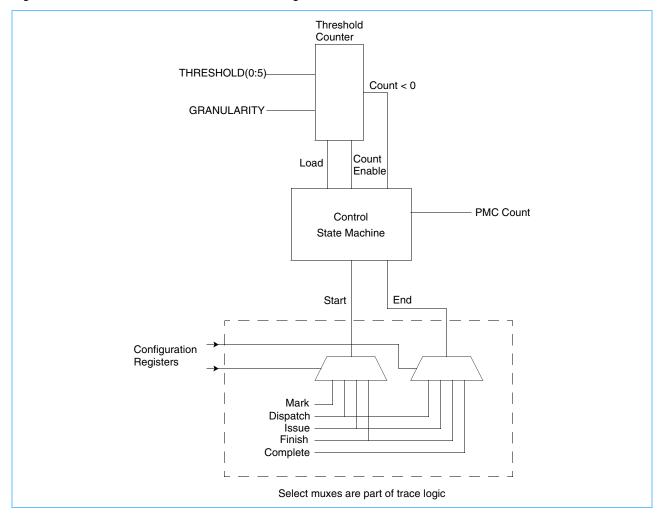

|     | 10.1.7 Thresholding                                                                         |     |

|     | 10.1.8 Trace Support Facilities                                                             |     |

|     | 10.2 Instruction Sampling Facilities                                                        |     |

|     | 10.2.1 Special Purpose Registers and Fields Associated with Instrumentation                 |     |

|     | 10.3 Performance Monitor Components                                                         |     |

|     | 10.4 Performance Monitor Control Registers                                                  |     |

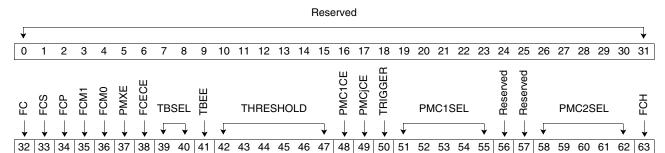

|     | 10.4.1 Performance Monitor Control Register MMCR0                                           |     |

|     | 10.4.2 Performance Monitor Control Register MMCR1                                           |     |

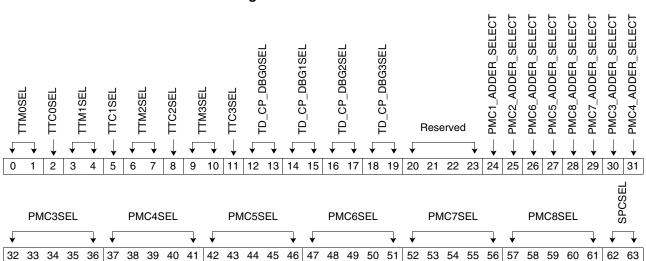

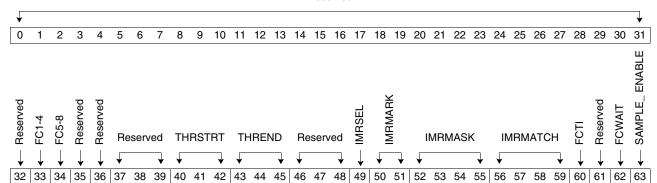

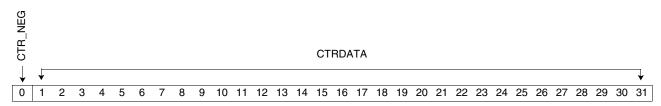

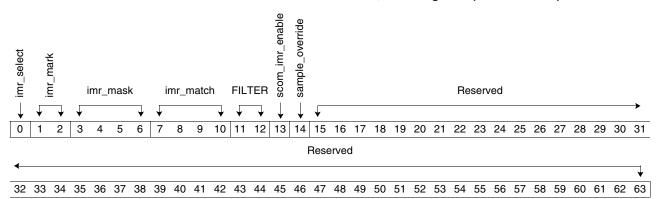

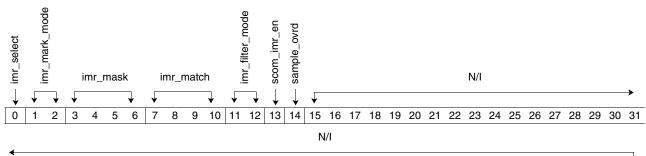

|     | 10.4.3 Performance Monitor Control Register MMCRA                                           |     |

|     | 10.4.4 Performance Monitor Count Registers PMC1 - 8                                         |     |

|     | 10.4.5 Performance Monitor and Trace Related Bits in the Machine State Register (MSR)       | 220 |

|     | 10.4.6 Performance Monitor Related Bits in Hardware Implementation-Dependent                |     |

|     | Register 0 (HID0)                                                                           |     |

|     | 10.4.7 Performance Monitor Related Bits in the Control Register (CTRL)                      |     |

|     | 10.4.8 Performance Monitor Related Bits in the SCOM0240, 1240 Register (SCOM x'240')        |     |

|     | 10.4.9 Performance Monitor Related Bits in the SCOM0360,1360 Register (SCOM x'360')         |     |

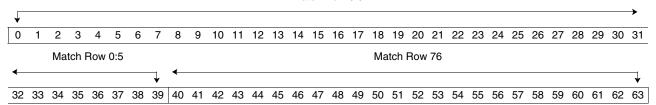

|     | 10.4.10 Performance Monitor Related Bits in the IMC Array (IMC)                             |     |

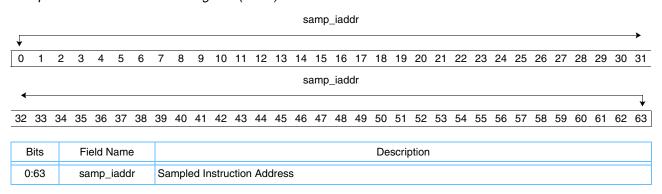

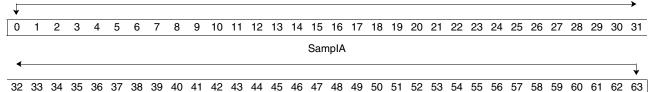

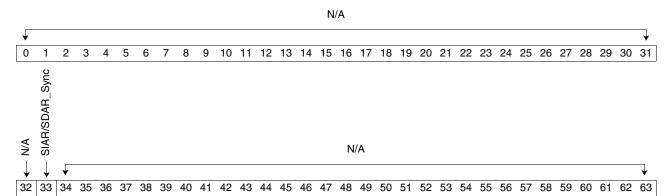

|     | 10.4.11 Performance Monitor Related Bits in the Sampled Instruction Address Register (SIAR) |     |

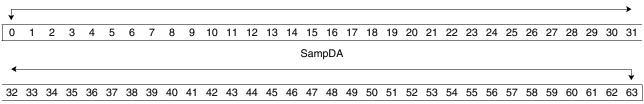

|     | 10.4.12 Performance Monitor Related Bits in the Sampled Data Address Register (SDAR)        |     |

|     | 10.4.13 Performance Monitor Related Bits in the SRR1 (SRR1)                                 |     |

|     | 10.4.14 Performance Monitor Related Bits in the Time-Base Register (TB)                     |     |

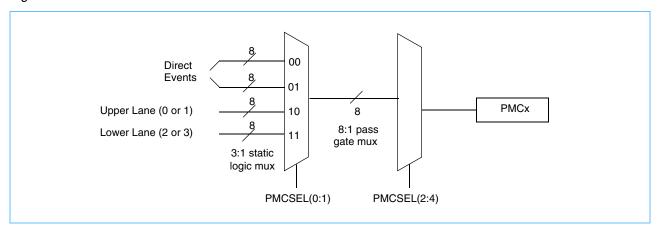

|     | 10.5 Performance Monitor Event Selection                                                    |     |

|     | 10.5.1 Direct Events                                                                        |     |

|     | 10.5.1.1 Combined Events                                                                    |     |

|     | 10.5.1.2 Source-Encoded Events                                                              |     |

|     | 10.5.1.3 Instruction Counts                                                                 |     |

|     | 10.5.2 Over 32-Bit Count                                                                    |     |

|     | 10.5.2.1 Examples of Over Bit Count                                                         |     |

|     | 10.5.3 Speculative Count                                                                    |     |

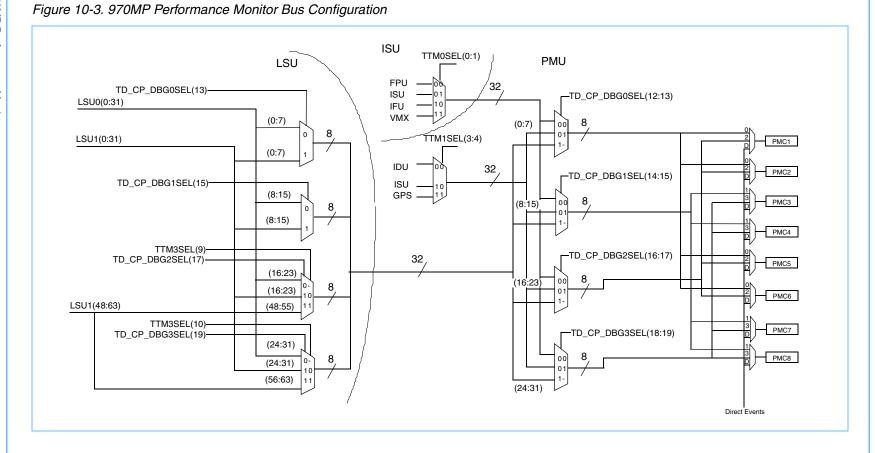

|     | 10.6 Configuring the Performance Monitor Bus                                                | 233 |

|     | 10.7 Enabling the Performance Monitor Counters                                              |     |

|     | 10.7.1 Machine States                                                                       | 243 |

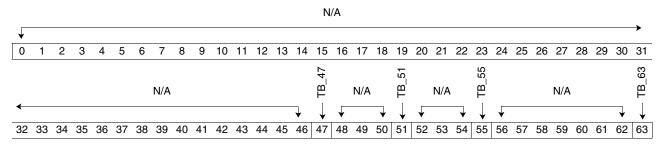

| 10.7.2 Trigger Events                                                     | 244 |

|---------------------------------------------------------------------------|-----|

| 10.7.2.1 Time-Base Transition Events                                      |     |

| 10.7.2.2 PMC1 Counter Negative Condition Events                           | 245 |

| 10.7.2.3 PMCj ( $2 \le j \le 8$ ) Counter Negative Condition Events       |     |

| 10.7.3 Method for Enabling or Disabling Performance Monitor Counting      |     |

| 10.8 Performance Monitor Exceptions                                       |     |

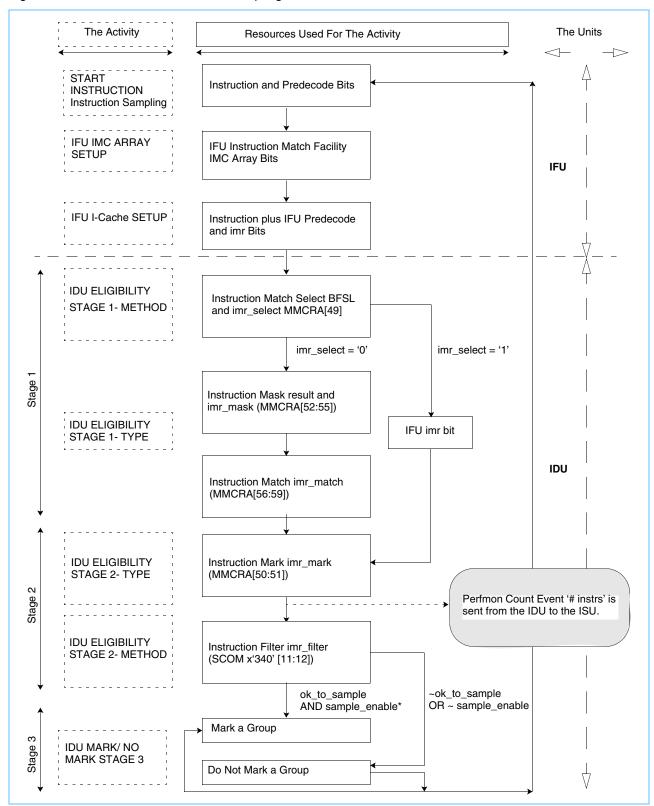

| 10.9 Instruction Matching and Sampling                                    |     |

| 10.9.1 Stage 1 Eligibility                                                |     |

| 10.9.2 Stage 2 Eligibility                                                |     |

| 10.9.3 Stage 3 Eligibility                                                |     |

| 10.10 IFU Instruction Matching Facility                                   |     |

| 10.10.1 Overview of the IFU Instruction Matching Facility                 |     |

| 10.10.2 IMC Array                                                         |     |

| 10.10.3 Reading the IMC SPR with the <b>mfimc</b> Instruction             |     |

| 10.10.4 Writing the IMC SPR With the <b>mtimc</b> Instruction             |     |

| 10.10.5 The v0 and v1 Mask Criteria                                       |     |

| 10.10.6 Instruction Matching Examples                                     |     |

| 10.11 IDU Instruction Sampling Facility                                   |     |

| 10.11.1 Overview of the IDU Instruction Sampling Facility                 |     |

| 10.11.2 Stage 1 Eligibility                                               |     |

| 10.11.3 Stage 2 Eligibility                                               |     |

| 10.11.4 Stage 3 Mark/No Mark                                              |     |

| 10.11.5 Complete Masking, Matching, and Marking Cycle                     |     |

| 10.11.6 Examples of Instruction Sampling Scenarios                        |     |

| 10.11.7 Enabling and Disabling Marking                                    |     |

| 10.12 SIAR and SDAR Registers                                             |     |

| 10.12.1 Instruction Sampling                                              |     |

| 10.12.1.1 Performance Monitor Exceptions                                  |     |

| 10.12.2 Single Step and Branch Trace Marking Mode                         |     |

| 10.12.2.1 Single Step Trace Mode                                          |     |

| 10.12.2.2 Branch Trace Mode                                               |     |

| 10.12.3 Comparison to Previous PowerPC Processors                         | 267 |

| 10.13 Thresholding                                                        |     |

| 10.14 Detailed Event Information                                          |     |

| TOTAL BOTALION EVOLUTION MICHIGARY                                        |     |

| 11. System Design                                                         | 270 |

|                                                                           |     |

| 11.1 I <sup>2</sup> C Interface                                           |     |

| 11.2 Bus Initialization, Configuration, Power Management, and Test        |     |

| 11.2.1 Bus Initialization                                                 |     |

| 11.2.2 Configurable Parameters                                            |     |

| 11.2.3 Configuration Interface                                            |     |

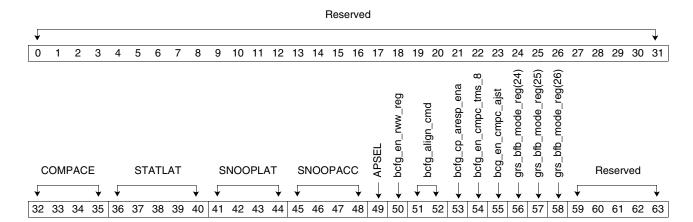

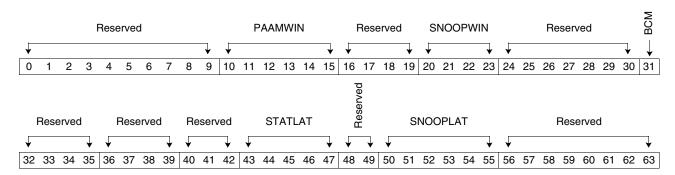

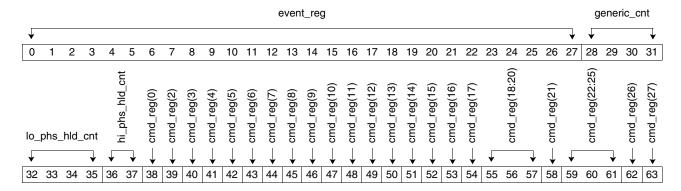

| 11.2.3.1 Processor Configurable Timing Delay Parameter Register (BUSCONF) |     |

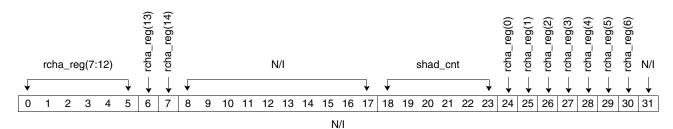

| 11.2.3.2 North Bridge Configurable Timing Delay Parameter Register        |     |

| 11.2.4 Power Management                                                   |     |

| 11.2.5 Reliability, Availability, and Serviceability (RAS) Requirement    |     |

| 11.3 Processor Interconnect Electrical Interface                          |     |

| 11.3.1 Initialization at Power-On Reset                                   |     |

| 11.3.2 Target Cycle                                                       | ∠8೪ |

|    | 11.4 Processor Interconnect Bus Error Detection and Correction         |     |

|----|------------------------------------------------------------------------|-----|

|    | 11.4.1 Error Detection for Balanced Encoding                           |     |

|    | 11.4.2 Error Detection for Alternative Encodings                       |     |

|    | 11.4.2.1 Single-Error and Double-Error Detection                       |     |

|    | 11.4.2.2 Single-Error Correct, Double-Error Detection                  | 292 |

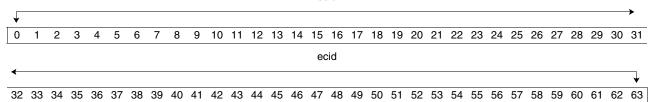

| 12 | . SCOM Interface and Registers                                         | 295 |

|    | 12.1 Processor Core SCOM SPR Access                                    |     |

|    | 12.1.1 Operating System Protocol to Access SCOM SPRs                   |     |

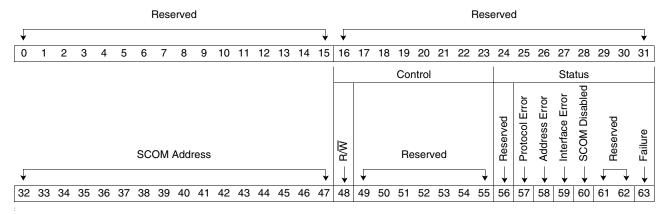

|    | 12.1.2 SCOMD Format                                                    |     |

|    | 12.1.3 SCOMC Format                                                    |     |

|    | 12.2 SCOM Address Allocation                                           | 299 |

|    | 12.2.1 Register Description Conventions                                |     |

|    | 12.2.2 SCOM Error Handling                                             |     |

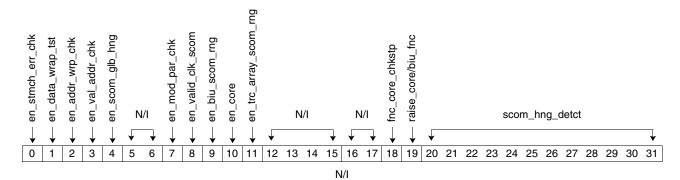

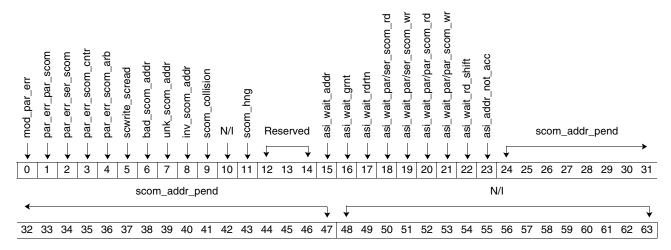

|    | 12.2.3 Access Status Register                                          | 304 |

|    | 12.3 Core Pervasive SCOM Register Definitions                          | 305 |

|    | 12.3.1 Processor CoreRAS Facilities (x'02[1:4]XXX')                    | 305 |

|    | 12.3.2 Processor Core SPR SCOM Access (x'023XXX')                      |     |

|    | 12.3.3 Processor Core Performance Monitor Sampling Control (x'02400X') |     |

|    | 12.3.4 Processor Core FIR Facilities (x'03[0:5]XXX')                   |     |

|    | 12.3.5 Instruction Mark Configuration (x'03600X')                      |     |

|    | 12.4 Storage Subsystem SCOM Register Definition                        |     |

|    | 12.4.1 L2 SCOM Register Definition                                     |     |

|    | 12.4.2 BIU SCOM Register Definition                                    |     |

|    | 12.4.3 Processor Interconnect Registers                                |     |

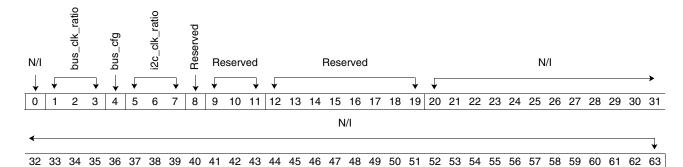

|    | 12.5 Chip Pervasive SCOM Register Definition                           |     |

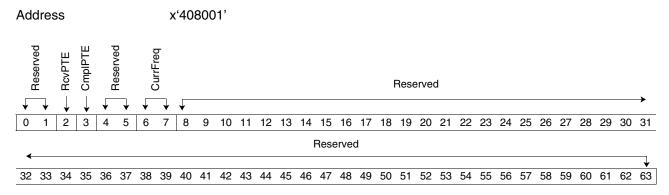

|    | 12.5.1 Power-On Reset Registers (x'40XXXX')                            |     |

|    | 12.5.2 Chip Free-Running Clock Section Control/Status (x'50[0:4]XXX')  |     |

|    | 12.5.3 Chip Parallel SCOM Control (x'6XXXXX')                          |     |

|    | 12.5.4 Chip Clock/Scan Control (x'8[0:4]XXXX')                         | 381 |

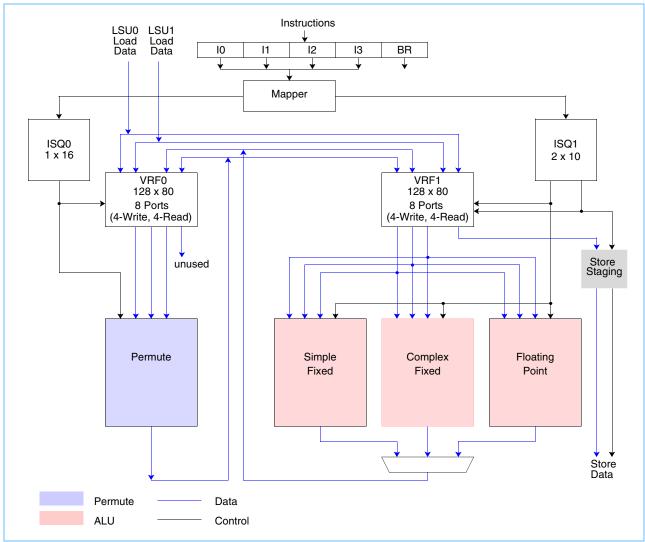

| 13 | . Vector Processing Unit                                               | 401 |

|    | 13.1 970MP Vector and SIMD Multimedia Overview                         | 401 |

|    | 13.1.1 VPU Implementation                                              | 401 |

|    | 13.1.2 Vector ALU                                                      | 402 |

|    | 13.2 Vector Registers                                                  | 403 |

|    | 13.2.1 VRSAVE Register                                                 | 403 |

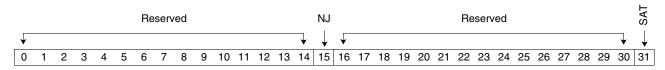

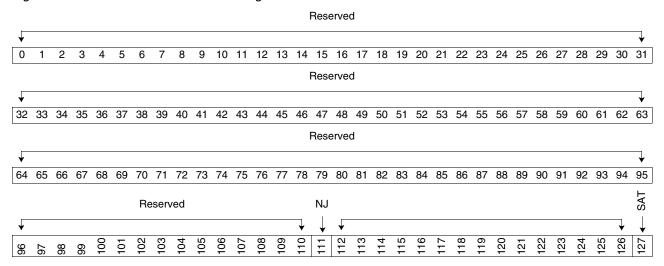

|    | 13.2.2 Vector Status and Control Register (VSCR)                       | 403 |

|    | 13.3 Effects on Existing PowerPC Facilities                            | 405 |

|    | 13.3.1 Control Flow                                                    | 405 |

|    | 13.3.1.1 Condition Register                                            | 405 |

|    | 13.3.1.2 Machine State Register                                        |     |

|    | 13.3.1.3 Machine Status Save/Restore Registers (SRR0, SRR1)            |     |

|    | 13.4 Exceptions                                                        |     |

|    | 13.4.1 VPU Unavailable Exception                                       |     |

|    | 13.4.2 VPU Assist Exception                                            |     |

|    | 13.4.3 Data Storage Exception                                          | 407 |

| 13.5 Optional Instructions                           | 408 |

|------------------------------------------------------|-----|

| 13.5.1 Java Mode Instruction Handling Implementation |     |

| 13.5.2 Least Recently Used Instructions              | 408 |

| 13.5.3 Data Stream Instructions                      |     |

| 13.6 Vector Instruction Set                          | 409 |

# **List of Figures**

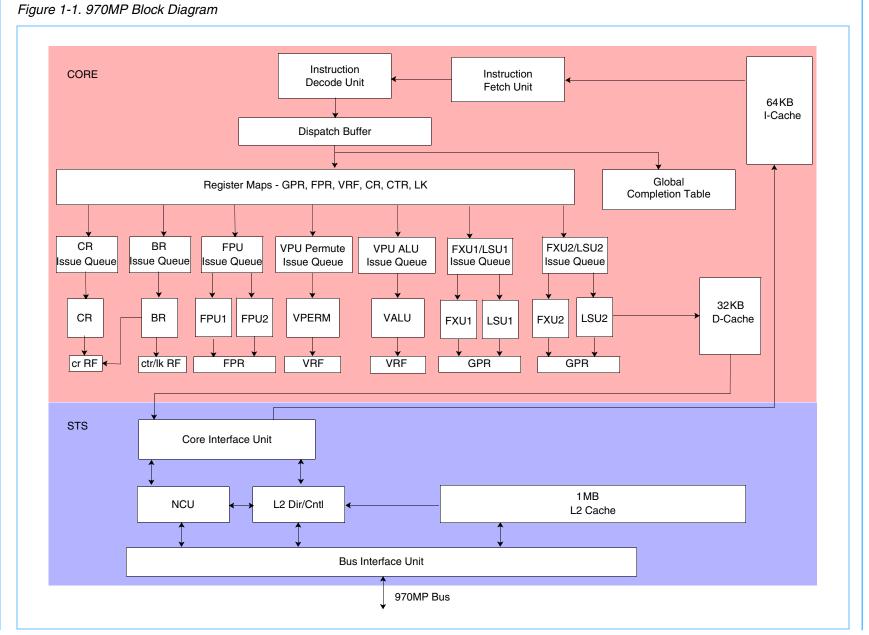

| Figure 1-1.  | 970MP Block Diagram                                                         | 34  |

|--------------|-----------------------------------------------------------------------------|-----|

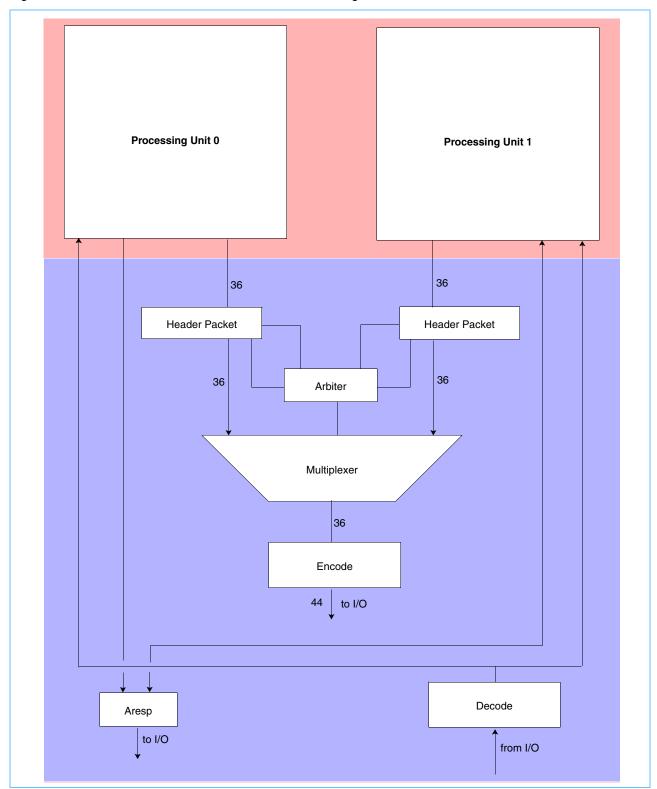

| Figure 1-2.  | 970MP Dual Core with Common Arbitration Logic                               | 35  |

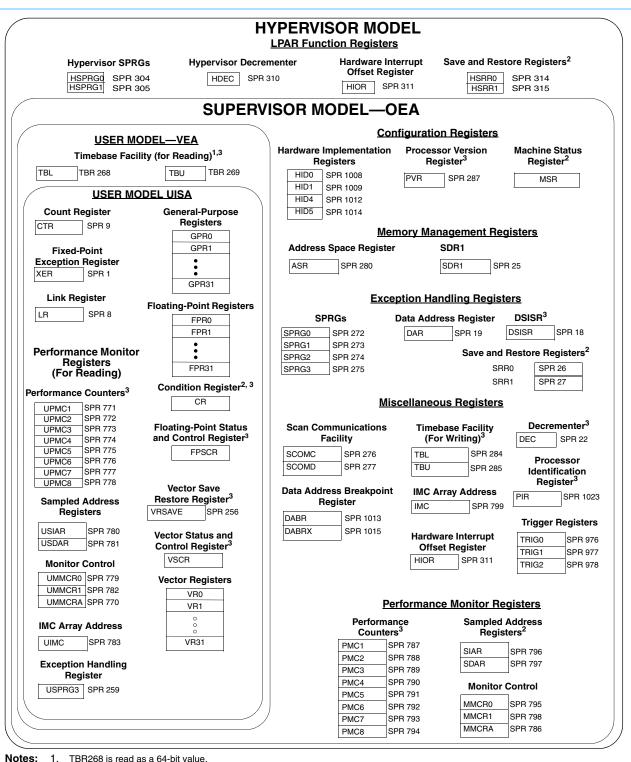

| Figure 2-1.  | 970MP Programming Model—Registers                                           | 44  |

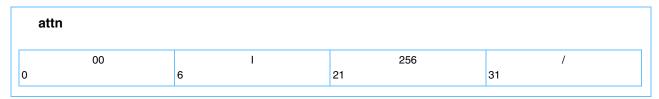

| Figure 2-2.  | Processor Attention Instruction                                             | 76  |

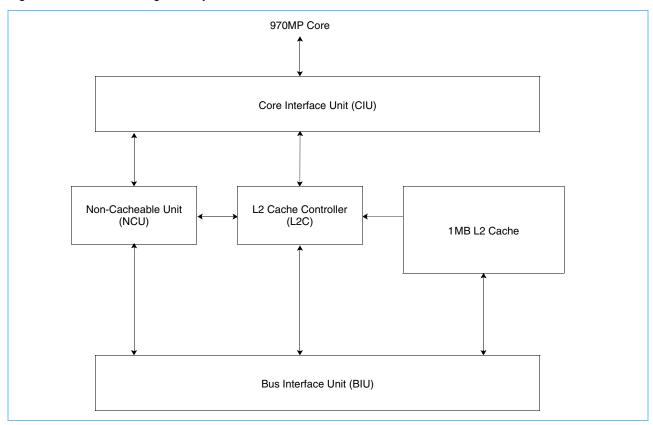

| Figure 3-1.  | 970MP Storage Subsystem                                                     | 90  |

| Figure 3-2.  | Data Flow in the 1MB L2 Cache                                               | 92  |

| Figure 3-3.  | Data Cache Block Touch X-Form (Optional Variant)                            | 96  |

| Figure 3-4.  | Data Cache Block Touch X-Form (Enhanced Variant)                            | 97  |

| Figure 7-1.  | 970MP Microprocessor Signal Groups                                          | 130 |

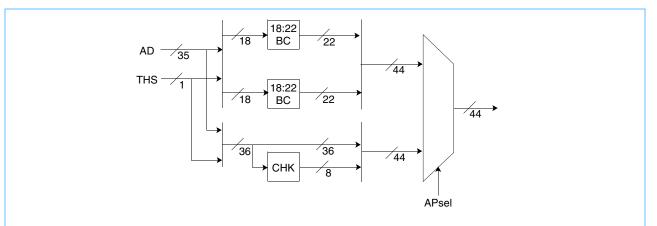

| Figure 7-2.  | Encoding and Selection Logic for the Drive Side of a 970MP Interconnect SSB | 132 |

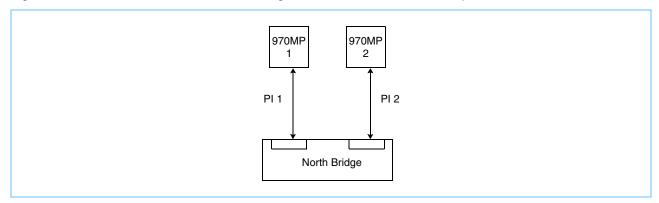

| Figure 8-1.  | Processor Interconnect Bus Configuration with Two 970MP Microprocessors     | 139 |

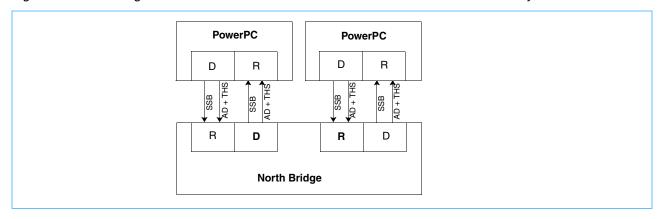

| Figure 8-2.  | Two Microprocessors Connected to a North Bridge                             | 140 |

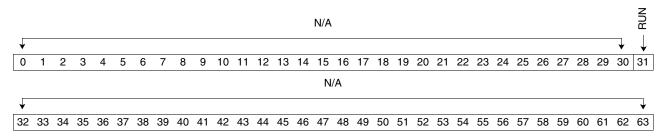

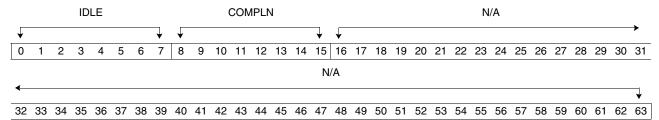

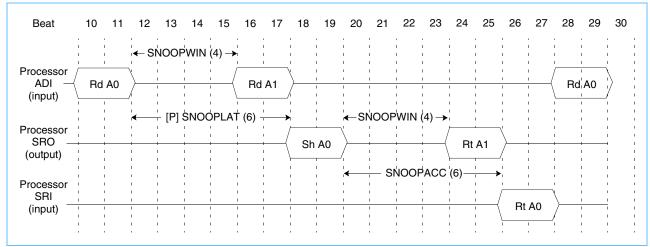

| Figure 8-3.  | Read Transaction Timing Diagram                                             |     |

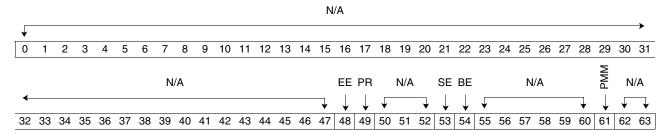

| Figure 8-4.  | Write Transaction Timing Diagram                                            | 144 |

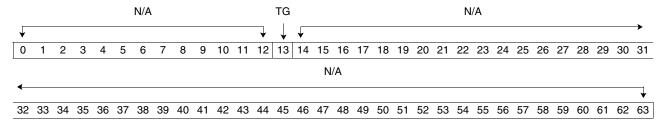

| Figure 8-5.  | Command-Only Transaction Timing Diagram                                     | 145 |

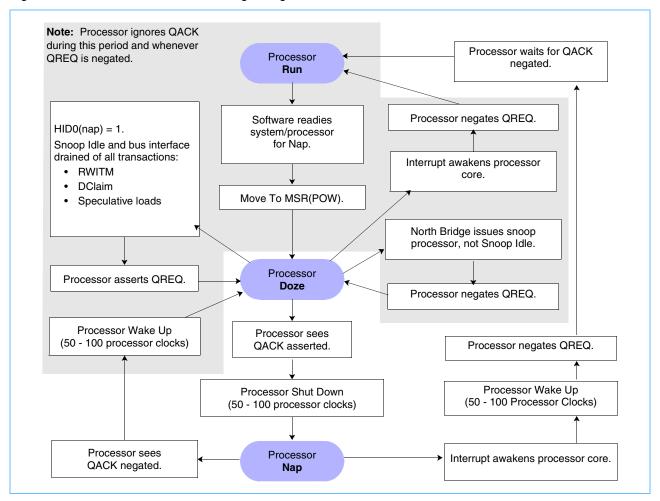

| Figure 9-1.  | Processor QREQ/QACK Signalling                                              | 176 |

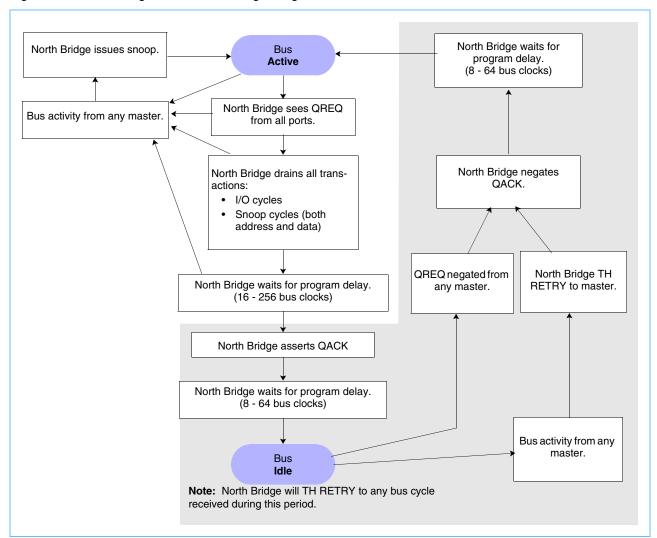

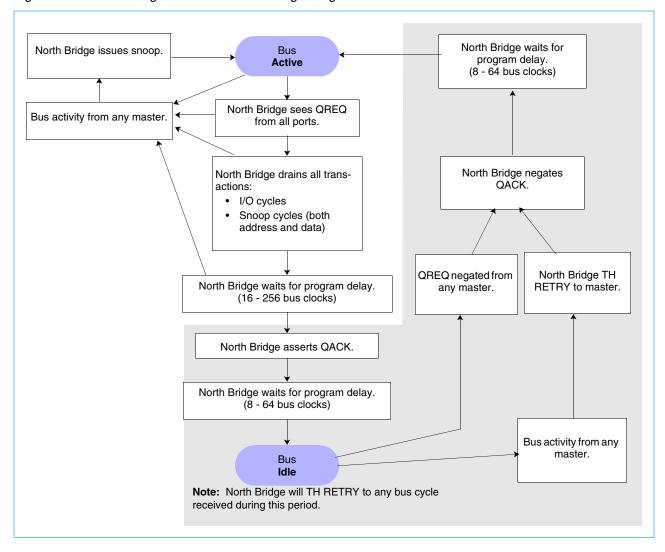

| Figure 9-2.  | North Bridge QREQ/QACK Signalling                                           | 177 |

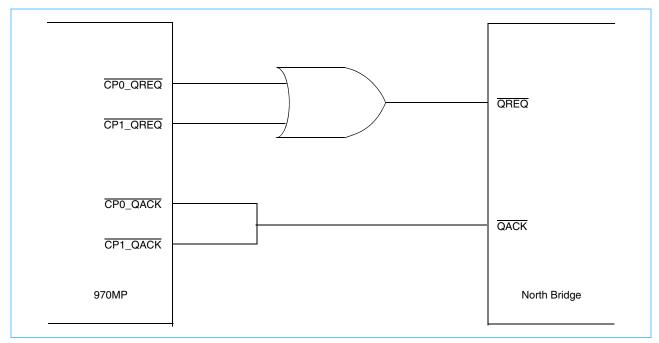

| Figure 9-3.  | Using a 970MP Microprocessor with a Single QREQ/QACK Pair                   | 178 |

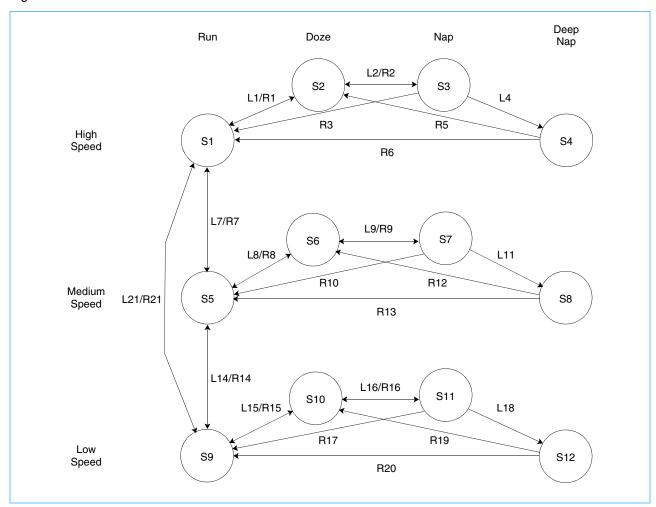

| Figure 9-4.  | 970MP Power Mode States                                                     | 183 |

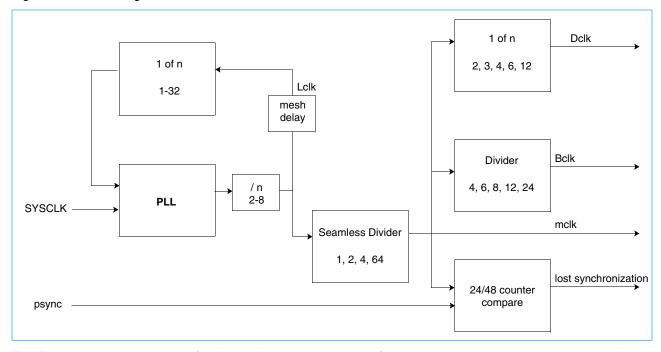

| Figure 9-5.  | PLL Design                                                                  | 190 |

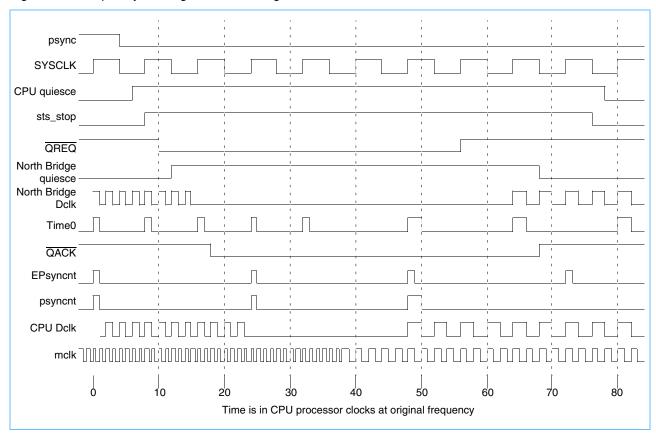

| Figure 9-6.  | Frequency Scaling Event Ordering                                            | 193 |

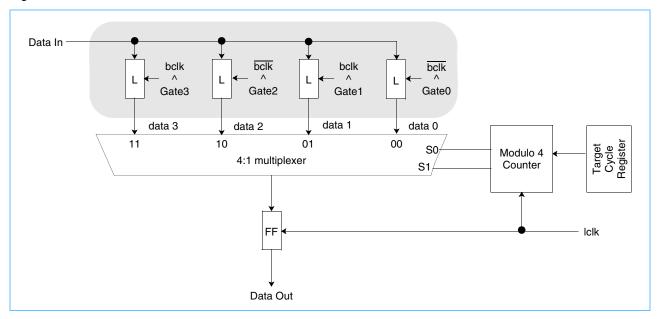

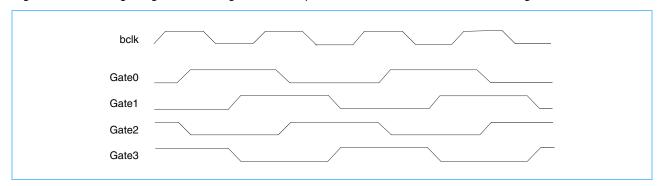

| Figure 9-7.  | Clock Dithering Block Diagram                                               | 200 |

| Figure 9-8.  | Sample Shift Pattern                                                        | 201 |

| Figure 10-1. | Performance Monitor Architecture                                            | 210 |

| Figure 10-2. | Event Selection                                                             | 227 |

| Figure 10-3. | 970MP Performance Monitor Bus Configuration                                 | 234 |

| Figure 10-4. | Patch Map                                                                   | 251 |

| Figure 10-5. | IFU and IDU Instruction Sampling Flow                                       | 259 |

| Figure 10-6. | Performance Monitor Threshold Logic                                         | 268 |

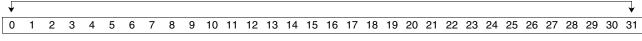

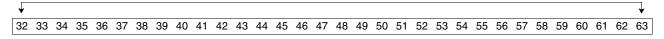

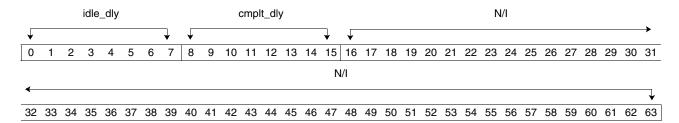

| Figure 11-1. | Configurable Timing Parameters                                              | 280 |

| Figure 11-2. | North Bridge Configurable Timing Parameters                                 | 280 |

| Figure 11-3. | Processor Configurable Timing Parameters                                    | 281 |

| Figure 11-4. | Processor QREQ and QACK Signalling                                          | 286 |

| Figure 11-5. | North Bridge QREQ and QACK Signalling                                       | 287 |

| Figure 11-6. | Bus Diagram of a Dual-Processor 970MP Processor Interconnect-Based System   | 288 |

| Figure 11-7. | Receive-Side FIFO Circuit                                                   | 290 |

| Figure 11-8. | Timing Diagram Showing Relationship Between Bclk and the Four Gate Signals  | 290 |

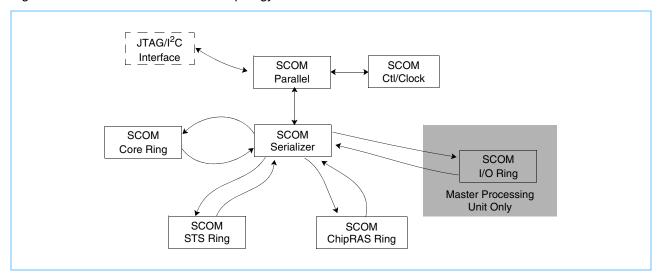

| Figure 12-1. | Processor Unit SCOM Topology                                                | 295 |

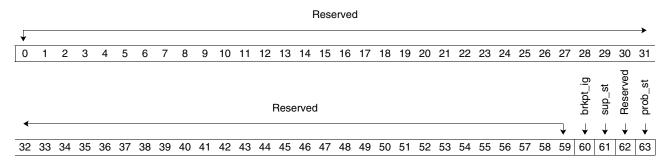

| Figure 12-2. | SCOMC SPR Format                               | .297 |

|--------------|------------------------------------------------|------|

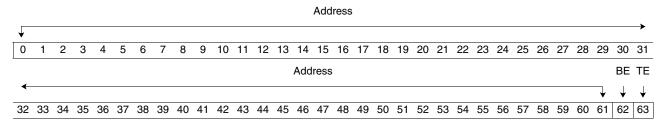

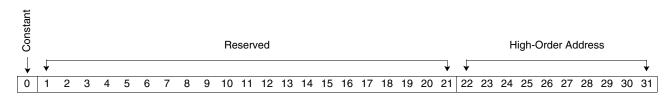

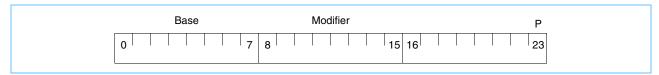

| Figure 12-3. | Format of an SCOM Address                      | .299 |

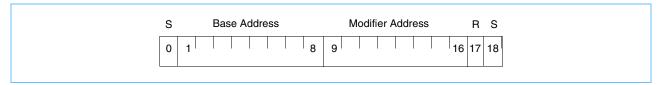

| Figure 12-4. | Format of an SCOM Address within the BIU       | .299 |

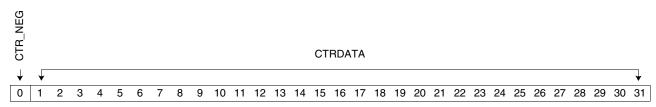

| Figure 12-5. | Format of an SCOM Data Bus                     | .299 |

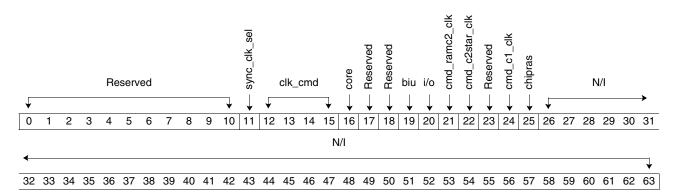

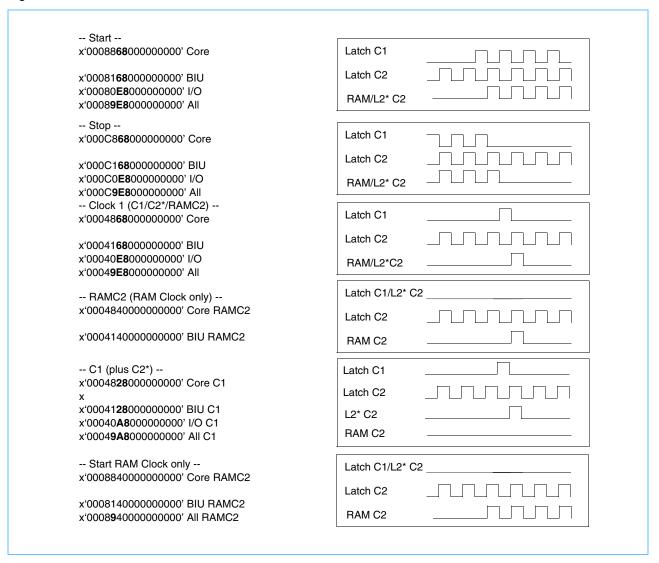

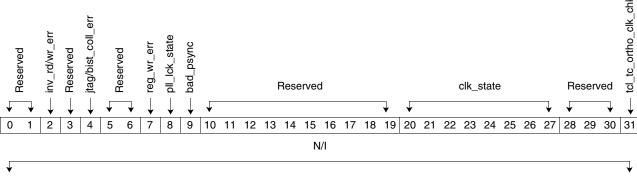

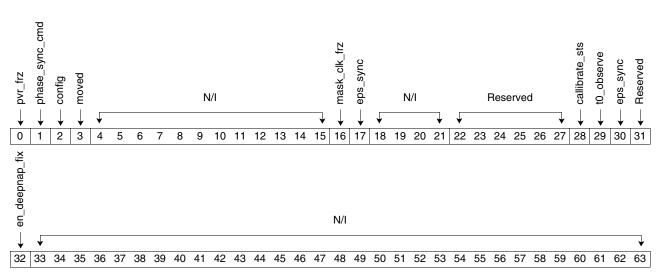

| Figure 12-6. | Common Clock Commands                          | .382 |

| Figure 12-7. | Example of LBIST Commands using the EPS Engine | .390 |

| Figure 13-1. | VPU Block Diagram                              | .402 |

| Figure 13-2. | VSCR Format                                    | .403 |

| Figure 13-3. | VSCR Moved to a Vector Register                | .404 |

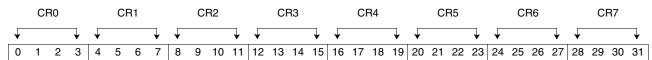

| Figure 13-4. | Condition Register (CR)                        | .405 |

# **List of Tables**

| Table i.    | Acronyms and Abbreviated Terms                                         | 26  |

|-------------|------------------------------------------------------------------------|-----|

| Table ii.   | Terminology Conventions                                                | 31  |

| Table iii.  | Instruction Field Conventions                                          | 31  |

| Table 2-1.  | MSR Bits                                                               | 49  |

| Table 2-2.  | Additional SRR1 Bit                                                    | 49  |

| Table 2-3.  | Implementation-Specific SPRs                                           | 51  |

| Table 2-4.  | Move To/Move From SPR Behavior                                         | 53  |

| Table 2-5.  | Storage Control Instructions                                           | 77  |

| Table 2-6.  | dcbz Actions                                                           | 79  |

| Table 3-1.  | Storage Hierarchy Characteristics                                      | 83  |

| Table 3-2.  | Simple Address Decode                                                  | 87  |

| Table 3-3.  | Storage Subsystem Functional Units                                     | 90  |

| Table 3-4.  | Cache-Coherency Protocol                                               | 93  |

| Table 3-5.  | 970MP L2 Cache State Transitions Due to Processor Instructions         | 93  |

| Table 3-6.  | 970MP L2 Cache State Transitions Due to Bus Operations                 | 94  |

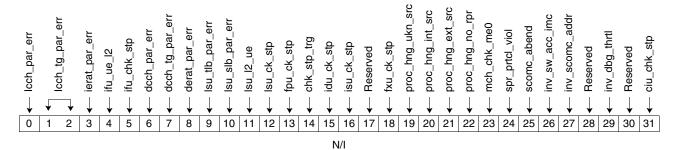

| Table 4-1.  | 970MP Microprocessor Exception Classifications                         | 100 |

| Table 4-2.  | Exceptions and Conditions                                              | 101 |

| Table 4-3.  | IEEE Floating-Point Exception Mode Bits                                | 108 |

| Table 4-4.  | Register Settings for Machine Check Exception                          | 112 |

| Table 4-5.  | Register Settings for Alignment Exception                              | 114 |

| Table 4-6.  | Register Settings for Trace Exception                                  | 115 |

| Table 4-7.  | Register Settings for the Performance Monitor Exception                | 116 |

| Table 4-8.  | Register Settings for VPU Unavailable Interrupt                        | 117 |

| Table 4-9.  | Register Settings for Maintenance Exception                            | 117 |

| Table 4-10. | Register Settings for VPU Assist Exception                             | 118 |

| Table 5-1.  | MMU Feature Summary                                                    | 120 |

| Table 5-2.  | Treatment of WIMG Bits in the 970MP                                    | 121 |

| Table 8-1.  | Processor Interconnect Signal Description                              | 141 |

| Table 8-2.  | Command Packet Description                                             | 147 |

| Table 8-3.  | Transfer Type Encoding                                                 | 149 |

| Table 8-4.  | Transfer Size Encoding                                                 | 150 |

| Table 8-5.  | Tag Definition                                                         | 151 |

| Table 8-6.  | Read-Data Packet Header Description                                    | 152 |

| Table 8-7.  | Data Beat Description                                                  | 152 |

| Table 8-8.  | Two-Beat Data Transfers                                                | 153 |

| Table 8-9.  | Packet Ordering for 128-Byte Interleaved Packets on 32-Byte Boundaries | 154 |

| Table 8-10. | Packet Ordering for 32-Byte Interleaved Packets                        | 154 |

| Table 8-11. | Transfer-Handshake Definition                                          | 155 |

| Table 8-12.  | Snoop-Response Bit Definition                                                |     |

|--------------|------------------------------------------------------------------------------|-----|

| Table 8-13.  | Allowed Snoop Responses                                                      |     |

| Table 8-14.  | Write-With-Kill Types Supported                                              |     |

| Table 9-1.   | Power-Management Control Bits                                                |     |

| Table 9-2.   | Minimum QAckIdleDelay requirement in bus clocks for 970MP                    | 179 |

| Table 9-3.   | Minimum (QAckIdleDelay + QAckMinLowTime) requirement in bus clocks for 970MP | 179 |

| Table 9-4.   | Power-Management Modes                                                       | 181 |

| Table 9-5.   | Power Mode States                                                            | 184 |

| Table 9-6.   | Transitions between Power Modes                                              | 185 |

| Table 9-7.   | Valid Combinations of Power Modes                                            | 186 |

| Table 9-8.   | Latency of Deep-Nap-to-Run Transitions in Full Frequency Cycles              | 188 |

| Table 9-9.   | Power Adjustment Transaction                                                 | 198 |

| Table 10-1.  | 970MP Performance Monitor and Trace-Related Special Purpose Registers        | 209 |

| Table 10-2.  | Performance Monitor Internal Multiplexer PMCxSEL[0:4] Bit Values             | 227 |

| Table 10-3.  | Event Data Source Encodings                                                  | 228 |

| Table 10-4.  | Event Instruction Source Encodings                                           | 229 |

| Table 10-5.  | Direct Events                                                                | 230 |

| Table 10-6.  | Speculative Count Events                                                     | 233 |

| Table 10-7.  | Performance Monitor Bus Assignments                                          | 235 |

| Table 10-8.  | Examples of Event Counter Enabling States                                    | 244 |

| Table 10-9.  | Partial Match Rows in the IMC Array                                          | 250 |

| Table 10-10. | Complete Match Rows in the IMC Array                                         | 250 |

| Table 10-11. | IMC SPR Patch Map Sample Results                                             | 252 |

| Table 10-12. | IMC SPR for a 17-Bit Match                                                   | 253 |

| Table 10-13. | IMC SPR Used when Writing the Second mtimc Instruction for a 32-Bit Match    | 253 |

| Table 10-14. | Encoding Bits v0 and v1 of the IMC Array Mask                                | 254 |

| Table 10-15. | IFU BSFL Predecode Bit Definitions                                           | 256 |

| Table 10-16. | Start and End Event Select Bits and the Performance Monitor Threshold Logic  | 269 |

| Table 10-17. | Detailed Event Descriptions                                                  | 270 |

| Table 11-1.  | Programmable Delay Parameters                                                | 281 |

| Table 11-2.  | I <sup>2</sup> C Interface Signals                                           | 282 |

| Table 11-3.  | I <sup>2</sup> C Registers Used by the 970MP Processor Interconnect          | 282 |

| Table 11-4.  | Bit Error Position Identifier                                                | 293 |

| Table 12-1.  | Operating System Code to Access SCOM                                         | 296 |

| Table 12-2.  | SCOM Base Addresses                                                          |     |

| Table 12-3.  | SCOM Modifier Addresses                                                      | 300 |

| Table 12-4.  | EPS Engine Description                                                       |     |

| Table 13-1.  | VSCR Field Descriptions                                                      |     |

| Table 13-2.  | CR6 Field Bit Settings for Vector Compare Instructions                       |     |

|              | -                                                                            |     |

| Table 13-3. | MSR Bit Settings Affecting the VPU | 406 |

|-------------|------------------------------------|-----|

| Table 13-4. | Supported Vector Instructions      | 409 |

# **Revision Log**

Each release of this document supersedes all previously released versions. The revision log lists all significant changes made to the document since its initial release. In the rest of the document, change bars in the margin indicate that the adjacent text was modified from the previous release of this document.

| Revision Date  | Page     | Description                                                                                                                  |

|----------------|----------|------------------------------------------------------------------------------------------------------------------------------|

|                |          | Version 2.3                                                                                                                  |

|                | 90       | Revised description in Section 3.5 Functional Units.                                                                         |

|                | 123      | Added a new section on software optimization (see Section 6 Software Optimization Guidelines).                               |

|                |          | Removed Section 2.2.1.3 Invalid Forms.                                                                                       |

| March 7, 2008  |          | Removed Section 3.5.3 Non-Cacheable Unit.                                                                                    |

| ,              |          | Removed Section 3.5.4.1 Overview of the Hardware-Controlled Data Prefetch.                                                   |

|                |          | Removed Section 3.5.4.2 Hardware Prefetch Engine Implementation.                                                             |

|                |          | Removed Section 3.5.4.4 Vector Prefetch Instruction Support.                                                                 |

|                |          | Removed Section 3.5.4.5 Programmability.                                                                                     |

|                |          | Removed Section 5.3 Memory Segment Model.                                                                                    |

|                |          | Version 2.2                                                                                                                  |

|                | 61       | Added DABRX bit description table to Section 2.1.2.3 Data Address Breakpoint<br>Register (DABR).                             |

|                | 112      | Modified DSISR[6] bit setting in <i>Table 4-4 Register Settings for Machine Check Exception</i> .                            |

| March 21, 2007 | 114      | <ul> <li>Modified DSISR[6] bit setting in Table 4-5 Register Settings for Alignment<br/>Exception.</li> </ul>                |

|                | 228      | Edited Table 10-3 Event Data Source Encodings.                                                                               |

|                | 284      | <ul> <li>Defined bit [31] as BCM in Table 11.2.3.2 North Bridge Configurable Timing<br/>Delay Parameter Register.</li> </ul> |

|                | 345      | Defined "g" as guarded access in the BIU Mode Register section.                                                              |

|                | 297      | Edited SCOMC bit description table in Section 12.1.3 SCOMC Format.                                                           |

|                |          | Version 2.1                                                                                                                  |

|                | 44       | Added SPRG3 to User Model — USIA block in Figure 2-1 970MP Programming Model—Registers and added a description.              |

| June 2, 2006   | 194, 196 | Corrected the SCOM address of the Power Control Register (PCR).                                                              |

|                | 295      | Added commonly used SCOM registers and their descriptions (Section 12 SCOM Interface and Registers).                         |

|                | 178      | Added Section 9.2.3.1 Delay Calculation                                                                                      |

| Revision Date    | Page       | Description                                                                                                                                                                                                |  |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  |            | Version 2.0                                                                                                                                                                                                |  |

|                  | 50         | Clarified the explanation of illegal instructions.                                                                                                                                                         |  |

|                  | 75         | Rewrote the description of the Load with Update instructions.                                                                                                                                              |  |

| June 28, 2005    | 153        | <ul> <li>Updated Table 8-8 Two-Beat Data Transfers, the description of the data transfer<br/>format, and Table 8-9 Packet Ordering for 128-Byte Interleaved Packets on 32-<br/>Byte Boundaries.</li> </ul> |  |

|                  | 173<br>174 | Expanded the description of Doze mode and how it relates to power management.                                                                                                                              |  |

|                  | 281        | <ul> <li>Corrected the programmable delay parameters for SNOOPLAT and<br/>SNOOPACC.</li> </ul>                                                                                                             |  |

| January 17, 2005 |            | Version 1.0 (Initial release)                                                                                                                                                                              |  |

## **About This Book**

The primary objective of the *IBM PowerPC*<sup>®</sup> *970MP RISC Microprocessor User's Manual* is to define the functionality of the PowerPC 970MP microprocessor for software and hardware developers.

The information in this book is subject to change without notice, as described in the disclaimers on the title page. As with any technical documentation, it is the readers' responsibility to be sure they are using the most recent version of the documentation. To locate any published errata or updates for this document, go to **ibm.com**/chips/techlib.

**Note:** Soft copies of many of the latest versions of the manuals and documents referred to in this manual that are produced by IBM can be accessed on the Web at **ibm.com**/chips/techlib.

#### **Audience**

This manual is intended for system software and hardware developers and application programmers who want to develop products for the 970MP microprocessor. It is assumed that the reader understands operating systems, microprocessor system design, basic principles of reduced instruction set computer (RISC) processing, and details of the PowerPC Architecture<sup>™</sup>.

# Organization

For ease in reference, the arrangement of topics in this book is similar to that of the *PowerPC Microprocessor Family: The Programming Environments Manual for 64-Bit Microprocessors* and the *PowerPC Microprocessor Family: Vector/SIMD Multimedia Extension Technology Programming Environments Manual* (see *Related Documents* on page 22). Topics build upon one another, beginning with a description and summary of 970MP-specific registers and instructions and progressing to more specialized topics such as 970MP-specific details regarding the cache, exception, memory management models, and power management. Thus, chapters might include information from multiple levels of the architecture. For example, the discussion of the cache model uses information from both the virtual environment architecture (VEA) and the operating environment architecture (OEA).

A summary and a brief description of the major sections of this manual follows:

- Chapter 1 PowerPC 970MP Overview is useful for readers who want a general understanding of the features and functions of the PowerPC Architecture and the 970MP processor. This chapter describes the flexible nature of the PowerPC Architecture definition, and provides an overview of how the PowerPC Architecture defines the register set, operand conventions, addressing modes, instruction set, cache model, exception model, and memory management model.

- Chapter 2 Programming Model is useful for software engineers who need to understand the 970MP-specific registers, operand conventions, and details regarding how the PowerPC instructions are implemented on the 970MP microprocessor. Instructions are organized by function.

- Chapter 3 Storage Subsystem discusses the storage subsystem as implemented on the 970MP microprocessor. The storage subsystem includes the core interface logic, the non-cacheable unit, the L2 cache and controls, and the bus interface unit.

- Chapter 4 Exceptions describes the exception model defined in the PowerPC OEA and the specific exception model implemented on the 970MP microprocessor.

- Chapter 5 Memory Management describes the 970MP implementation of the memory management unit specifications provided by the PowerPC OEA for PowerPC processors.

- Chapter 6 Software Optimization Guidelines describes key design characteristics of the 970MP microprocessor.

- Chapter 7 Signal Description describes the individual signals of the 970MP microprocessor.

- Chapter 8 Processor Interconnect Bus describes the processor interface (PI), which is a bus architecture providing high-speed, high-performance interconnections for processors, I/O devices, memory subsystems, and bridge chips.

- Chapter 9 Power and Thermal Management provides information about power saving and thermal management modes for the 970MP microprocessor.

- Chapter 10 970MP Performance Monitor describes the operation of the performance monitor diagnostic tool incorporated in the 970MP microprocessor and provides detailed event information.

- Chapter 11 System Design describes system-related features such as power-on reset and reliability, availability, and serviceability (RAS) considerations.

- Chapter 12 SCOM Interface and Registers describes the scan communication (SCOM) facility that is

used to access processor debug and diagnostic facilities.

- Chapter 13 Vector Processing Unit provides a general understanding of the features and functions of the vector processing unit (VPU) used on the 970MP microprocessor.

#### **Related Documents**

#### **Companion Manuals**

This manual is intended as a companion to the following reference manuals:

PowerPC Architecture<sup>1</sup> books:

**Note:** The PowerPC Architecture books supersede the *PowerPC Programming Environments Manual* for the 970MP implementation. However, not all features available in the PowerPC Architecture are supported in the 970MP microprocessor (such as, logical partitioning).

- PowerPC User Set Architecture (Book I, Version 2.01). Covers the base user instruction set architecture (UISA), user-level registers, data types, memory conventions, memory and programming models, and related facilities available to the application programmer.

- PowerPC Virtual Environment Architecture (Book II, Version 2.01). Defines the storage model and related instructions and facilities available to the programmer, and the time-keeping facilities available to the application programmer. The VEA, which is the smallest component of the PowerPC Architecture, defines additional user-level functionality that falls outside typical user-level software requirements. The VEA describes the memory model for an environment in which multiple processors or other devices can access external memory and define aspects of the cache model and cache control instructions from a user-level perspective. The resources defined by the VEA are particularly useful for optimizing memory accesses and for managing resources in an environment in which other processors and other devices can access external memory.

<sup>1.</sup> PowerPC Architecture refers to the instructions and facilities described in Books I, II, and III.

Implementations that conform to the PowerPC VEA also conform to the PowerPC UISA, but might not necessarily adhere to the operating environment architecture (OEA).

PowerPC Operating Environment Architecture (Book III, Version 2.01). Defines the system (privileged) instructions and related facilities. The OEA defines supervisor-level resources typically required by an operating system. The OEA defines the PowerPC memory management model, supervisor-level registers, and the exception model.

Implementations that conform to the PowerPC OEA also conform to the PowerPC UISA and VEA.

- PowerPC Microprocessor Family: Programming Environments Manual for 64-Bit Microprocessors

(referred to as the Programming Environments Manual). Provides information about resources defined by

the PowerPC Architecture that are common to PowerPC processors. This manual describes the functionality of the 64-bit architecture model.

- PowerPC Microprocessor Family: Vector/SIMD Multimedia Extension Technology Programming Environments Manual. Describes how the vector/SIMD technology relates to both the 64-bit and the 32-bit portions of the PowerPC Architecture.

- The PowerPC Architecture: A Specification for a New Family of RISC Processors by C. May, E. Silha, R. Simpson, and H. Warren, Morgan Kaufman, May 1994. Defines the architecture from the perspective of the three programming environments and remains the defining document for the PowerPC Architecture.

Because the PowerPC Architecture is designed to be flexible in order to support a broad range of processors, these documents provide a general description of features that are common to PowerPC processors and indicate those features that are optional or that might be implemented differently in the design of each processor.

It is important to note that some resources are defined more generally at one level in the architecture and more specifically at another. For example, conditions that cause a floating-point unavailable exception are defined by the UISA, while the exception mechanism itself is defined by the OEA.

#### **Additional Documentation**

Some additional PowerPC documentation is available at **ibm.com**/chips/techlib through IBM Customer Connect at http://ibm.com/technologyconnect.

- IBM PowerPC 970MP RISC Microprocessor Datasheet. This datasheet provides specific data about bus timing, signal behavior, and ac, dc, and thermal characteristics, as well as other design considerations for the 970MP implementation.

- PowerPC 970MP Power On Reset Application Note. This document contains information about required power-on-reset design and initialization.

- PowerPC Microprocessor Family: The Programmer's Reference Guide (MPRPPCPRG-01). This is a concise reference that includes the register summary, memory control model, exception vectors, and the PowerPC instruction set.

- Application notes. These short documents contain information about specific design issues useful to programmers and engineers working with PowerPC processors.

### **General PowerPC Documentation**

The following documentation provides useful information about the PowerPC Architecture and computer architecture in general:

Ferraiolo, F., E. Cordero, D. Dreps, M. Floyd, "Power4: Synchronous Wave-Pipelined Interface." *Hot Chips* 1999, Stanford, CA.

Hennessy, John L. and David A. Patterson. Computer Architecture: A Quantitative Approach. 2nd ed.

<sup>2</sup>C-Bus Specification. Version 2.1. Philips Semiconductors, 2000.

IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Std. 1149.1a-1993.

McClanahan, Kip. PowerPC Programming for Intel Programmers. Foster City, CA: IDG Books Worldwide, Inc.

Shanley, Tom. PowerPC System Architecture. Richardson, TX: Mindshare, Inc.

#### **Conventions**

This document uses the following notational conventions:

& AND logical operator.

l OR logical operator.

'0' Binary values in text are either spelled out (zero and one) or appear in single quotation

marks. For example: '10101'. In tables, these quotation marks are omitted.

$\neg$  NOT logical operator.

**crf**D Instruction syntax used to identify a destination CR field.

crfS Instruction syntax used to identify a source Condition Register (CR) field.

frA, frB, frC Instruction syntax used to identify a source Floating-Point Register (FPR).

**fr**D Instruction syntax used to identify a destination FPR.

italics Italics indicate variable command parameters. For example, **bcctr**x. Book titles in text are

set in italics.

**mnemonics** Instruction mnemonics are shown in lowercase bold.

*n* Used to express an undefined numeric value.

overbar Overbars designate active-low (non-differential) signals.

rA, rB Instruction syntax used to identify a source General-Purpose Register (GPR).

**r**D Instruction syntax used to identify a destination GPR.

REG[FIELD] Abbreviations or acronyms for registers are shown in uppercase text. Specific bits, fields,

or ranges appear in brackets. For example, MSR[POW] refers to the Power-Management

bit in the Machine State Register.

Reserved Indicates reserved bits or bit fields in a register. Although these bits can be written to as

either ones or zeros, they are always read as zeros.

vA, vB, vC Instruction syntax used to identify a source Vector Register (VR).

**v**D Instruction syntax used to identify a destination VR.

x In certain contexts, such as a signal encoding, this indicates a don't care.

x'0' A lowercase x precedes hexadecimal values. For example, x'0B00'.

# **Acronyms and Abbreviations**

Table i contains acronyms and abbreviations that are used in this document.

Table i. Acronyms and Abbreviated Terms (Page 1 of 5)

| Term    | Meaning                                                                                           |

|---------|---------------------------------------------------------------------------------------------------|

| ALU     | arithmetic logic unit                                                                             |

| AS      | application system                                                                                |

| ASR     | Address Space Register                                                                            |

| BAT     | block address translation                                                                         |

| BCM     | balanced coding method                                                                            |

| ВНТ     | branch history table                                                                              |

| BIST    | built-in self test                                                                                |

| BIU     | bus interface unit                                                                                |

| BPU     | branch processing unit                                                                            |

| BSDL    | boundary-scan description language                                                                |

| CAM     | content-addressable memory                                                                        |

| CDF     | critical data forward                                                                             |

| CIU     | core interface unit                                                                               |

| CMOS    | complementary metal-oxide semiconductor                                                           |

| COP     | common on-chip processor                                                                          |

| CQ      | completion queue                                                                                  |

| CR      | Condition Register                                                                                |

| CRA     | custom register array                                                                             |

| CTR     | Count Register                                                                                    |

| DABR    | Data Address Breakpoint Register                                                                  |

| DAR     | Data Address Register                                                                             |

| D-cache | data cache                                                                                        |

| DCMP    | data translation lookaside buffer (TLB) compare                                                   |

| DEC     | Decrementer Register                                                                              |

| DMISS   | data TLB miss address                                                                             |

| DPM     | dynamic power management                                                                          |

| DSI     | data storage interrupt                                                                            |

| DSISR   | Data Storage Interrupt Status Register. Register used to determine the source of a DSI exception. |

| DTLB    | data translation lookaside buffer                                                                 |

| EA      | effective address                                                                                 |

| EAR     | External Access Register                                                                          |

| ECC     | error checking and correction                                                                     |

| eCR     | emulation CR                                                                                      |

| eFPR    | emulation FPR                                                                                     |

# Table i. Acronyms and Abbreviated Terms (Page 2 of 5)