# **Signetics**

# 74LS1801 Bit Stream Manager

Encoder/Decoder

Product Specification

#### **Logic Products**

#### DESCRIPTION

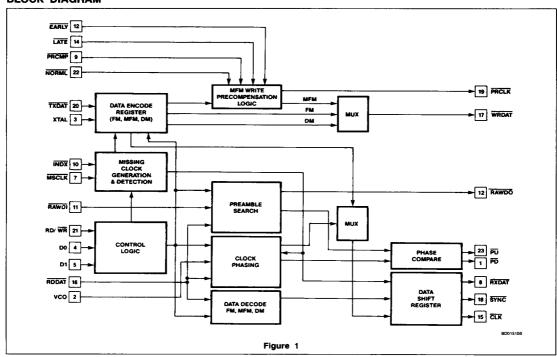

The 74LS1801 Encoder/Decoder (Figure 1) supports disk drive and data communications devices that require fast and reliable data separation capabilities. Although ideally suited for use with the 74LS1802 Serializer/Deserializer, the 74LS1801 is a flexible device which can be implemented in a variety of design applications.

Encoding is possible in FM, MFM, or Differential Manchester formats, making the 74LS1801 invaluable in designs requiring single density disk recording, or in data communications applications. Included on-chip is a phase-comparator which can be bypassed; this feature is particularly useful in applications that use a complete external phase lock loop.

#### **FEATURES**

- Data rates up to 10MHz

- FM, MFM, and Differential Manchester encoding/decoding

- Precompensation in MFM write mode

- Built-in phase comparator

- Single 5V power supply

- Selectable encoding violation generation/detection formats

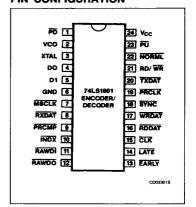

#### PIN CONFIGURATION

#### **BLOCK DIAGRAM**

August 13, 1985 7-18 853-0121 80031

74LS1801

### PIN CONFIGURATION

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |                                                                                           | PIN NO. | IDENTIFIER      | DESCRIPTION                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | VCO [2] XTAL [3] DO [4] DO [4] DO [5] GND [6] FACINF [7] FACINF [9] FACINF [9 |                                  | 24 Vcc<br>23 PU                                                                           | 10      | INDX            | INDeX – an input that designates the missing clock pattern to be generated during the write mode; in the read mode, determines which data/clock pattern must be recognized as an address mark (Table 2, 3). |

|         | DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | · 🗖                              | 22 NORML<br>21 RD/ WR<br>20 TXDAT                                                         | 11      | RAWDI           | RAW Data In - a shaped data pulse derived from RAWDO. RAWDO is normally tied directly to RAWDI.                                                                                                             |

|         | MSCLK<br>RXDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ENCODER/<br>DECODER              | 19 PRCLK 18 SYNC 17 WRDAT 16 RDDAT                                                        | 12      | RAWDO           | RAW Data Out - a shaped data pulse derived from RDDAT that can be processed through an external phase lock loop. RAW-DO is normally tied directly to RAWDI.                                                 |

|         | RAWDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TT.                              | 15 CLK 14 LATE 13 EARLY                                                                   | 13      | EARLY           | Modifies clock rate with respect to crystal reference when early precompensation is desired.                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  | <del></del>                                                                               | 14      | LATE            | Modifies clock rate with respect to crystal reference when late pre-compensation is desired.                                                                                                                |

|         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | T                                |                                                                                           | 15      | CLK             | CLocK - Clock input equal to the frequency of NRZ data.                                                                                                                                                     |

| PIN NO. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pump Down - a                    | In output from the phase indicates the frequency of                                       | 16      | RDDAT           | ReaD DATa - an input of encoded serial data (MFM, FM, or Differential Manchester) that is to be converted to NRZ data.                                                                                      |

| 2       | vco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | an external VCC<br>RDDAT.        | o is too high as compared to<br>ed Oscillator - an input used                             | 17      | WRDAT           | WRite DATa - an output of encoded serial data (FM, MFM, or Differential Manchester) derived from NRZ data.                                                                                                  |

| 3       | XTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | as a phase refe<br>data (RDDAT). | rence for the encoded read synchronize the 74LS1801                                       | 18      | SYNC            | SYNChronization output - when active low, indicates recognition of valid encoding violation in the RDDAT.                                                                                                   |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | during write mo                  | de; the crystal frequency is                                                              | 19      | PRCLK           | PRecompensation CLocK - an output used to excite an external delay line.                                                                                                                                    |

| 4<br>5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (FM, MFM, Diffe                  | puts designating the format<br>rential Manchester) of serial<br>to be encoded or decoded. | 20      | TXDAT           | Transmit Data an input of NRZ data that is to be encoded to FM, MFM, or Differential Manchester data.                                                                                                       |

| 6 7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  | - missing clock bits are                                                                  | 21      | RD/WR           | ReaD/WRite - an input designating mode of operation: when high, a read is indicated;                                                                                                                        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | generated/detec                  | cted in the data stream,<br>the state of this input                                       | 22      | NORML           | when low, a write is indicated.  NORMaL – a clock input that is used when no precompensation is desired.                                                                                                    |

| 8       | RXDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  | - an output consisting of oded from MFM, FM, or chester data.                             | 23      |                 | Pump Up - an output from the phase com-<br>parator that indicates the frequency of an<br>external VCO is too low as compared to                                                                             |

| 9       | PRCMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  | input that allows precom-<br>M encoded data.                                              | 24      | V <sub>CC</sub> | RDDAT. Supply voltage.                                                                                                                                                                                      |

#### **ORDERING CODE**

| PACKAGES     | COMMERCIAL RANGES<br>V <sub>CC</sub> = 5V ±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------|-------------------------------------------------------------------------------|

| Hermetic DIP | N74LS1801I                                                                    |

| Plastic DIP  | N74LS1801N                                                                    |

August 13, 1985

#### **FUNCTIONAL OPERATION**

The 74LS1801 Encoder/Decoder serves to translate data between disk drive or data communications devices and the 74LS1802 Serializer/Deserializer (or comparable device). Information entering or leaving the Serializer/Deserializer interface is in the form of standard NRZ data and can be encoded to (or decoded from) one of three popular formats:

- Frequency Modulation (FM) single density disk recordings.

- Modified Frequency Modulation (MFM) double density disk recordings.

- Differential Manchester data communications applications.

#### Read/Write and Format Control

The operational mode of the 74LS1801 is dictated by the RD/WR input: when low, a write (encode) is indicated; when high, a read (decode) is designated. In either mode, the format of data being decoded or encoded is controlled by the states of D0 and D1 inputs as shown below:

Table 1. Format Control

| D0 | D1 | RESULTING FORMAT        |

|----|----|-------------------------|

| L  | L  | MFM                     |

| H  | L  | FM                      |

| L  | н  | Differential Manchester |

Following are discussions of the encoding and decoding functions of the 74LS1801, and the timing requirements necessary for accurate data transmittal.

#### **Encoding Logic**

When in the encode mode, NRZ data is input via the TXDAT input and, after about a three bit delay, is output on WRDAT. As described, output format is dependent on the states of D0 and D1. Address marks are distinguished from data by deleting clock pulses within the character.

These "missing clocks" are generated within the byte following a preamble of either all 0's (MFM and FM format) or all 1's (Differential Manchester format). As described in Table 2, clocks are eliminated according to inputs INDX, MSCLK, and the specified encoding format

When encoding data in the MFM format, MSCLK may be enabled during preamble generation and up to the beginning of an address mark. MSCLK can then be disabled during the byte following an address mark, or before the final bit of a four bit series in which the first two bits are 0's (e.g., before the final 0 in 0010). In applications utilizing consecutive A1 characters (such as in the case of floppy disk soft-sectored formats), MSCLK

August 13, 1985

Table 2. Missing Clocks

| MSCLK | ÍNDX | FORMAT                     | RESULTING CLOCK PATTERN Bit Cell Numbers: |      |       |       |         | ı |   |   |

|-------|------|----------------------------|-------------------------------------------|------|-------|-------|---------|---|---|---|

|       |      |                            | 0                                         | 1    | 2     | 3     | 4       | 5 | 6 | 7 |

| L     | Н    | FM                         |                                           |      | ٧     | ٧     | ٧       |   |   |   |

| L     | L    | FM                         |                                           |      | ٧     |       | ٧       |   |   |   |

| L     | н    | Differential<br>Manchester | ٧                                         | ٧    |       | ٧     | ٧       |   |   |   |

| L     | L    | Differential<br>Manchester | ٧                                         | ٧    |       |       | ٧       |   |   |   |

| L     | X    | MFM                        | 2n                                        | d of | 3 clo | cks n | nissing | 9 |   |   |

#### NOTES:

- X = Don't care

- V = Missing Clock

Table 3. Address Mark Identification Requirements in Decode Mode

| MSCLK | INDX | CONDITIONS FOR ACTIVE SYNC OUTPUT    |

|-------|------|--------------------------------------|

| Н     | X    | First "1" bit after preamble         |

| L     | н    | A1 <sub>16</sub> with missing clocks |

| L     | L    | Any byte with missing clocks         |

would remain active until the beginning of the byte following the A1 series.

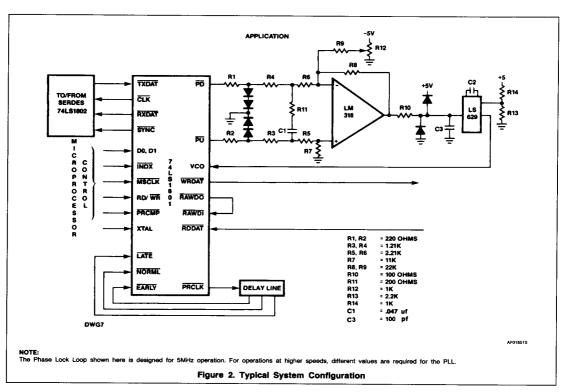

The 74LS1801 also provides pre-compensation capabilities when encoding data in the MFM format. Activating the PRCMP signal (low) synchronizes output data according to a clock input provided on one of three inputs: EARLY – a clock shifted early in time, LATE – a clock shifted late in time, or NORML – a clock provided when no precompensation is needed. These inputs are supplied by an external delay line which, in turn, is excited by the PRCLK output (see Typical System Configuration, Figure 2.)

When encoding in FM or Differential Manchester formats, missing clocks are only generated in the first byte following a preamble of zeroes. The most significant bit of this byte must be a "1"; for example, address marks F8, FB, FC, or FE. MSCLK may be enabled up to the beginning of an address mark; once an address mark has been transmitted, it is not necessary to disable MSCLK.

#### **Decoding Logic**

In the decode mode, data (MFM, FM, or Differential Manchester) is input via the RDDAT input and, after an eleven bit delay, is output as NRZ data on RXDAT. As described above, input format is defined by the states of D0 and D1. In the MFM format, a minimum preamble length of 34 bits is required to allow for phase synchronization and location of an address mark; when in FM or Differential Manchester mode, a minimum length of 18 bits is required. After a preamble has been recognized, the 74LS1801 searches for an address mark. When an address mark is identified, the SYNC output becomes active low, and alerts the 74LS1802 of incoming data. Rules for positive address mark identification are described below and summarized in Table 3.

When MSCLK is inactive, SYNC is activated on the first "1" data bit following a preamble of zeroes (MFM and FM) or 1's (Differential Manchester). Data is contained in the byte following this bit.

If MSCLK is active, the byte following a preamble of all zeroes is checked for the required missing clocks (Table 3) and if detected, SYNC is activated.

## PHASE LOCK LOOP AND DATA SEPARATION LOGIC

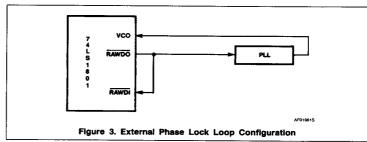

Data/clock separation logic requires a clock pulse that is synchronous with read data (RDDAT); to create this signal, the 74LS1801 employs a Phase Lock Loop. In its simplest form, the PLL consists of an internal phase comparator, an external low pass filter and an external voltage controlled oscillator (VCO). Output from the VCO is continuously fed back to the phase compare circuit and contrasted with data read from the disk or communications device (RDDAT). A difference in phase is represented as one of two quantized output pulses: Pump Up indicates VCO frequency is too low, whereas Pump Down indicates that the VCO frequency is too high. The resulting output  $(\overline{PU} \text{ or } \overline{PD})$  is then processed by a lowpass filter which outputs a DC voltage proportional to the phase deviation. Accordingly, the VCO frequency is precisely serviced to the rate at which data was recorded. The 74LS1801 provides the capability to bypass internal phase compare logic; a typical application of this feature would be in designs implementing a complete external PLL.

Figure 3 illustrates this application and is discussed below.

RAW Data Out is a shaped data pulse derived directly from RDDAT. In MFM and FM modes, output is generated from the falling edge of RDDAT: in Differential Manchester mode, output is generated from both rising and falling edges. RAW Data In is a shaped data pulse derived from RAWDO and is used in internal data separation logic. The falling edge of RAWDI must be in phase with the falling edge of the VCO. RAWDI is normally tied directly to RAWDO.

August 13, 1985 7-21

74LS1801

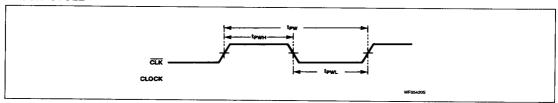

#### **CLOCK CYCLE**

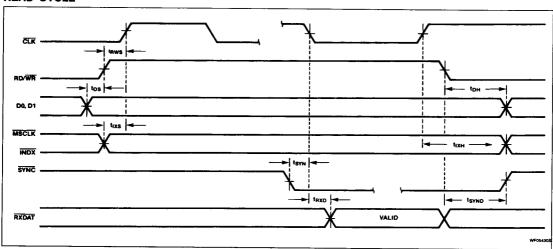

#### **READ CYCLE**

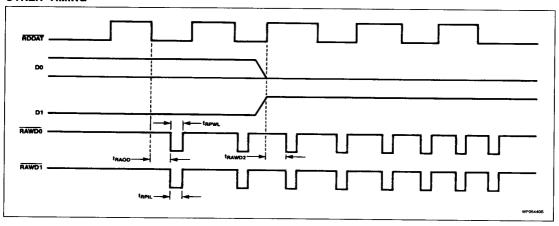

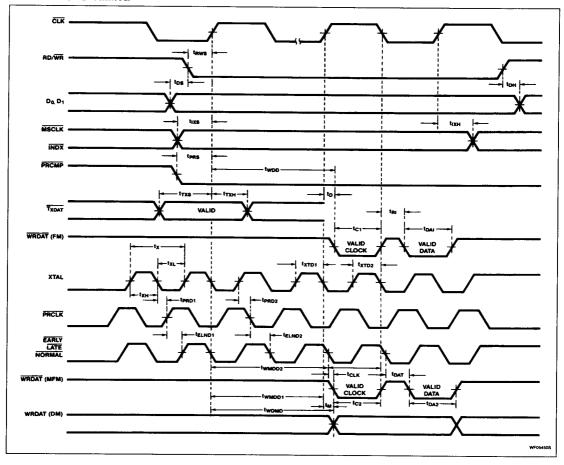

#### OTHER TIMING

August 13, 1985

7-22

74LS1801

August 13, 1985 7-23

74LS1801

#### **ABSOLUTE MAXIMUM RATINGS**

| PIN            | DESCRIPTION      | RATING | UNIT |  |

|----------------|------------------|--------|------|--|

| Vcc            | Supply voltage   | +7.0   | V    |  |

| All other pins | Logic input pins | 5.5    | ٧    |  |

## DC ELECTRICAL CHARACTERISTICS $V_{CC} = 5V \pm 5\%$ ; TA = 0°C to +70°C

| PARAMETER       |                                    | TEAT 001101110110                                                          | LIMITS     |  |              |          |                                          |

|-----------------|------------------------------------|----------------------------------------------------------------------------|------------|--|--------------|----------|------------------------------------------|

|                 |                                    | TEST CONDITIONS                                                            | Min Typ    |  | Max          | UNIT     | COMMENTS                                 |

| V <sub>TH</sub> | Input<br>threshold voltage         |                                                                            | 0.8        |  | 2.0          | V        |                                          |

| V <sub>CD</sub> | Input clamp<br>diode voltage       | I <sub>N</sub> = -18mA                                                     |            |  | -1.2         | ٧        |                                          |

| IIL             | Input low<br>current               | V <sub>IN</sub> = 0.4V                                                     |            |  | -20          | μΑ       |                                          |

| lін             | Input high<br>current              | V <sub>IN</sub> = 2.7V                                                     |            |  | 20           | μΑ       |                                          |

| lį              | Max input<br>high current          | V <sub>IN</sub> = 5.5V                                                     |            |  | 100          | μА       |                                          |

| V <sub>OL</sub> | Output<br>voltage low              | I <sub>OL</sub> = 8mA<br>I <sub>OL</sub> = 20mA                            |            |  | 0.5<br>0.5   | V        | Pins 8, 12, 15, 17, 18, 1<br>Pins 1, 23  |

| V <sub>OH</sub> | Output<br>voltage high             | V <sub>CC</sub> = 4.5V<br>I <sub>OH</sub> = 400μA<br>I <sub>OH</sub> = 1mA | 2.5<br>2.5 |  |              | V        | Pins 8, 12, 15, 17, 18, 19<br>Pins 1, 23 |

| los             | Output<br>short circuit<br>current | V <sub>OUT</sub> = 0<br>V <sub>OUT</sub> = 1                               | -15<br>-15 |  | -100<br>-100 | mA<br>mA | Pins 8, 12, 15, 17, 18, 19<br>Pins 1, 23 |

| Icc             | Supply current                     |                                                                            |            |  | 184          | mA       |                                          |

#### **AC ELECTRICAL CHARACTERISTICS**

| PARAMETER          | DESCRIPTION                  |     | LIMITS (in ns) |           |  |  |  |

|--------------------|------------------------------|-----|----------------|-----------|--|--|--|

| PARAMETER          | DESCRIPTION                  | Min | Тур            | Max       |  |  |  |

| t <sub>PW</sub>    | CLK pulse width              | 100 |                |           |  |  |  |

| tpwL               | CLK low time                 | 50  |                |           |  |  |  |

| t <sub>PWH</sub>   | CLK high time                | 50  |                |           |  |  |  |

| t <sub>X</sub>     | XTAL cycle time              | 50  |                |           |  |  |  |

| t <sub>XH</sub>    | XTAL high time               | 25  |                |           |  |  |  |

| t <sub>XL</sub>    | XTAL low time                | 25  |                |           |  |  |  |

| t <sub>RWS</sub>   | RD/WR set-up to ↑CLK         | О   |                |           |  |  |  |

| t <sub>DS</sub>    | D0, D1 set-up to RD/WR       | l 0 |                |           |  |  |  |

| tixs               | MSCLK, INDX set-up to ↑CLK   |     | 35.2           |           |  |  |  |

| tsyn               | ↓SYNC to ↓CLK                | 2   |                |           |  |  |  |

| t <sub>RXD</sub>   | ↓CLK to RXDAT valid          |     |                | 4         |  |  |  |

| t <sub>DH</sub>    | RD/WR to D0, D1 hold         | 0   |                |           |  |  |  |

| tsynd              | RD/WR to SYNC inactive delay |     |                | 36.4      |  |  |  |

| tRAOD              | ↓RDDAT to ↓RAWDO delay       |     | 29.2           |           |  |  |  |

| t <sub>RPIL</sub>  | RAWDI pulse width            | 20* |                |           |  |  |  |

| t <sub>RPWL</sub>  | RAWDO pulse width            |     |                | 40*       |  |  |  |

| twomp              | TXDAT to WRDAT (DM)          |     |                | tpw + 41. |  |  |  |

| t <sub>M</sub>     | ↑CLK to WRDAT delay          |     | 41.2           | '''       |  |  |  |

| t <sub>RAWD2</sub> | ↑RDDAT to ↓RAWDO delay       |     | 32.2           |           |  |  |  |

August 13, 1985 7-24

74LS1801

#### **AC ELECTRICAL CHARACTERISTICS (Continued)**

| PARAMETER          | DESCRIPTION                                               |         | LIMITS (in ns)         |                      |  |  |

|--------------------|-----------------------------------------------------------|---------|------------------------|----------------------|--|--|

| FAILAMETER         | DESCRIPTION                                               | Min     | Тур                    | Max                  |  |  |

| t <sub>DA2</sub>   | DATA bit duration                                         |         | 23.0                   |                      |  |  |

| tixH               | ↑CLK to MSCLK, INDX hold                                  |         | 14.8                   |                      |  |  |

| t <sub>PRS</sub>   | PRCMP set-up to TCLK                                      |         |                        | 0                    |  |  |

| t⊤xs               | TXDAT set-up to 1CLK                                      |         | 85.2                   |                      |  |  |

| t <sub>TXH</sub>   | TXDAT hold time                                           |         | 14.8                   |                      |  |  |

| twod               | TXDAT to WRDAT clock delay (FM data)                      | 1       | t <sub>PW</sub> + 36.3 |                      |  |  |

| t <sub>D</sub>     | ↑CLK to clock delay (FM data)                             |         | 36.3                   |                      |  |  |

| t <sub>C1</sub>    | Clock bit duration (FM)                                   |         | 19.0                   |                      |  |  |

| t <sub>R1</sub>    | Clock & data bit separation                               |         | 31.0                   |                      |  |  |

| t <sub>DA1</sub>   | Data bit duration (FM)                                    |         | 19.0                   |                      |  |  |

| txTD1              | ↑XTAL to ↑ <del>CLK</del> delay                           |         | 35.2                   |                      |  |  |

| tXTD2              | ↑XTAL to ↓ <del>CLK</del> delay                           |         | 32.2                   |                      |  |  |

| t <sub>PRD1</sub>  | ↓XTAL to ↑PRCLK delay                                     |         | 26.3                   |                      |  |  |

| t <sub>PRD2</sub>  | ↑XTAL to ↓PRCLK delay                                     |         | 28.3                   |                      |  |  |

| t <sub>ELND1</sub> | PRCLK to Early, Late, Normal rising edge                  | 1/2 tpw |                        | 1/4 tpw              |  |  |

| t <sub>ELND2</sub> | ↓PRCLK to Early, Late, Normal falling edge                | 1/4 tpw |                        | 0                    |  |  |

| twmDD2             | TXDAT to WRDAT data delay (MFM)                           |         | 1                      | 3.5 x tp             |  |  |

| t <sub>WMDD1</sub> | TXDAT to WRDAT clock delay (MFM)                          |         |                        | 3.0 x t <sub>P</sub> |  |  |

| <sup>t</sup> CLK   | Early, Late, Normal falling edge to clock bit delay (MFM) |         | 12.1                   |                      |  |  |

| t <sub>C2</sub>    | Clock bit duration (MFM)                                  |         | 23.0                   |                      |  |  |

| t <sub>DAT</sub>   | Early, Late, Normal falling edge to data bit delay (MFM)  |         | 12.1                   |                      |  |  |

<sup>\*</sup>Tabular entries with an asterisk are parameters that are guaranteed at the values listed; these values were determined either by system bench testing or by Signetics' characterization procedures. All other tabular entries are taken directly from simulation results run at range of operational frequencies; these values are not tested or guaranteed.