# FAIRCHILD DIODE-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS

# INDUSTRIAL MICROCIRCUITS-COMPOSITE DATA SHEET

0°C TO 75°C TEMPERATURE RANGE

GENERAL DESCRIPTION - Fairchild Diode Transistor Micrologic® (DTµL) Integrated Circuits family uses diode-transistor logic and is designed specifically for integrated circuit technology. The design of these circuits offers distinctly superior performance. Some of the advantages follow:

#### **FEATURES**

- High performance with a single power supply --- 5.0 V

- High noise immunity --- 1.0 V

- High fan-out capability --- 8-25

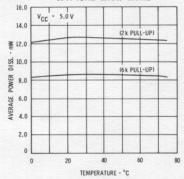

- Gates with 6k or 2k pull-up resistors for optimum speed

- Fan-out and noise immunity trade-off

- Low power dissipation --- 8.5 mW/Gate

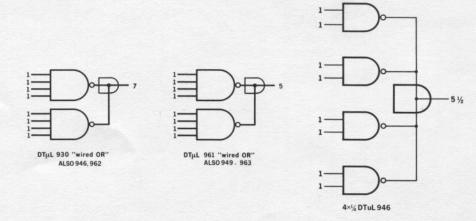

- Gate outputs can be tied together for the "wired OR" function

# ORDER INFORMATION

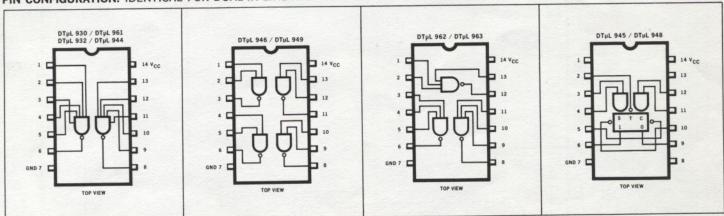

To order Diode Transistor Micrologic elements specify U3I9XXX59X for Flat package and U6A9XXX59X for Dual In-Line package where XXX is 930,932 etc.

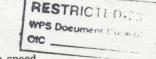

# PIN CONFIGURATION: IDENTICAL FOR DUAL-IN-LINE AND FLAT PACKAGES

313 FAIRCHILD DRIVE, MOUNTAIN VIEW, CALIFORNIA, (415) 962-5011, TWX: 910-379-6435

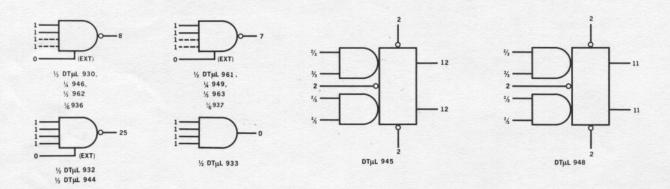

# DTµL GATES

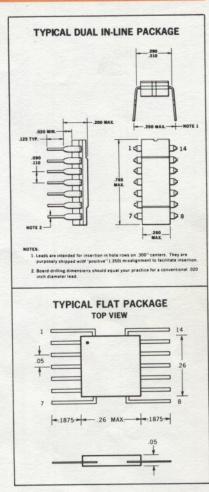

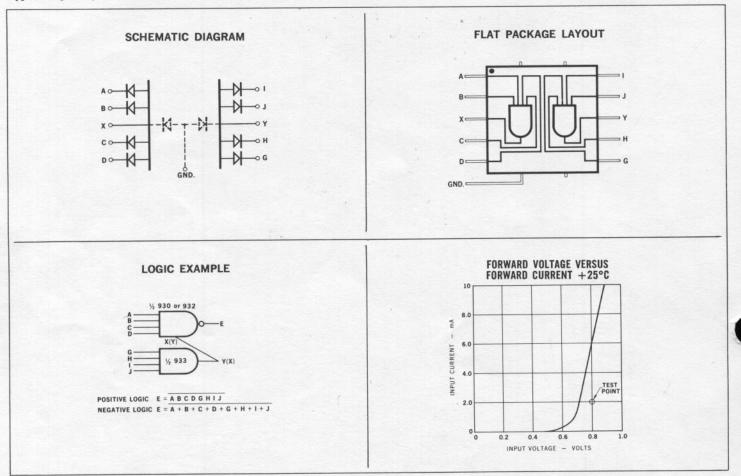

All  $DT\mu L$  gates are positive logic NAND gates or negative logic NOR gates. A variety of gate combinations is available which provides the system designer the utmost in logic flexibility and reduces package requirements to a minimum. Gate outputs may be paralleled to perform OR (collector) logic. In addition, gates may be cross-connected to form flip-flops, exclusive OR, etc. Gates with  $2 k\Omega$  pull-up resistors offer improved propagation delay times.

#### AVERAGE POWER DISSIPATION VERSUS TEMPERATURE (TYPICAL EACH GATE)

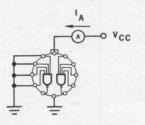

#### **TEST CONDITIONS**

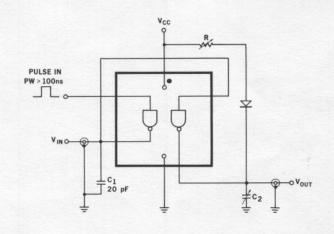

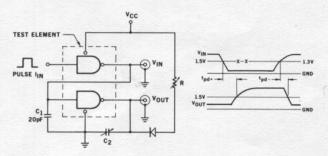

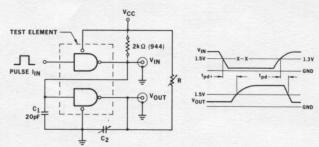

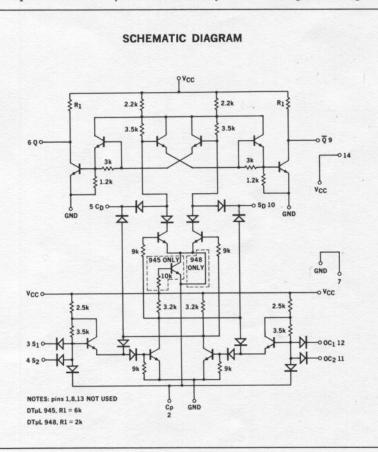

## TYPICAL Tpd TEST CIRCUIT DTµL GATES

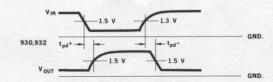

$T_{pd}$  - will be read from input at 1.3 V.

$$(v_{CC} = 5 V, T = 25^{\circ}C)$$

|                     |                   | R            | C <sub>2</sub> | Min.  | Max.  |

|---------------------|-------------------|--------------|----------------|-------|-------|

| (6 k Pull-up)       | t <sub>pd+</sub>  | 3.9 kΩ       | 30 pF          | 25 ns | 80 ns |

| (6 k & 2 k Pull-up) | t <sub>pd</sub> - | 400 Ω        | 50 pF          | 10 ns | 30 ns |

| (2 k Pull-up)       |                   | $3.9k\Omega$ | 30 pF          | 15 ns | 50 ns |

## OPERATING VOLTAGE CHARACTERISTICS

WORST CASE (OUTPUT LOGIC LEVEL — VOH AND VOL INPUT THRESHOLD LEVELS — VIH AND VIL)

3.2

2.8

VOH MIN

1.6

VOL MAX

0

0

20

40

1EMPERATURE - "C

0

80

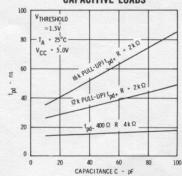

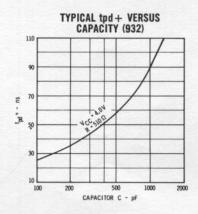

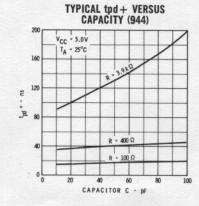

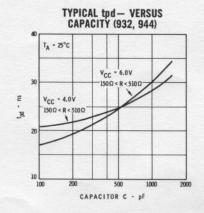

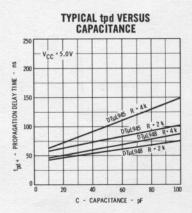

#### TIME DELAY VERSUS CAPACITIVE LOADS

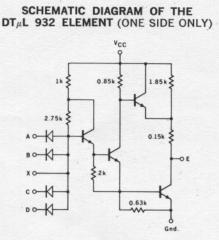

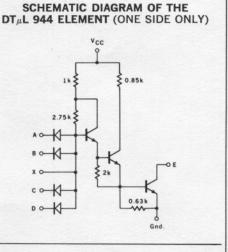

# DTµL 932 BUFFER ELEMENT DTµL 944 POWER GATE

The  $DT\mu L$  932 is a dual 4-input inverting driver. It features an emitter-follower pull-up which provides a high fan-out device with superior capacitance-driving capability. The  $DT\mu L$  944 has an output with no internal pull-up. This provides a high fan-out device whose outputs may be tied together to perform the "wired OR" function. The 944 is useful as an interface driver or as a low-power lamp driver. The fan-in of either element may be extended with the use of the  $DT\mu L$  933.

#

#### tpd TEST CIRCUIT FOR DT<sub>µ</sub>L 932 ELEMENT

All Diodes are FD600 or Equivalent at 25°C C<sub>1</sub> and C<sub>2</sub> includes Probe and Jig Capacitance

# tpd TEST CIRCUIT FOR DT $_{\mu}$ L 944 ELEMENT

C<sub>1</sub> and C<sub>2</sub> includes Probe and Jig Capacitance

# DTµL 945 • DTµL 948 - CLOCKED FLIP - FLOP

The  $DT\mu L$  945 and  $DT\mu L$  948 Clocked Flip-Flops are directly-coupled units operating on the "master-slave" principle. Information enters the "master" while the Trigger input voltage is high and transfers to the "slave" when the Trigger input voltage goes low. Since operation depends only on voltage levels, any sort of waveshape having the proper voltage levels may be used as a trigger signal. Rise and fall times are irrelevant.

The  $DT\mu L$  945 and  $DT\mu L$  948 have an improved direct Set and Clear design which allows unhampered asynchronous entry irrespective of signals applied to any other inputs. The direct inputs always take precedence, thus simplifying the design of arbitrarily preset ripple-counters and other minimum hardware applications.

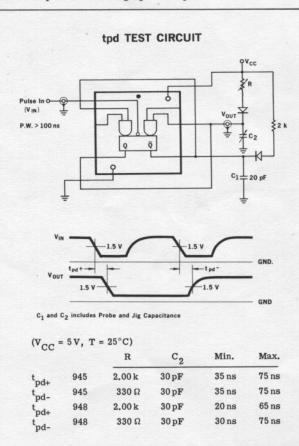

Output buffers provide isolation between the "slave" and the output load, thereby enhancing immunity to signal line noise. The  $DT_{\mu}L$  945 incorporates the standard 6k-ohm output pull-up resistor, while the  $DT_{\mu}L$  948 features a 2k-ohm output pull-up resistor for improved rise times, and matched delay between rising and falling outputs for capacitive loading up to 100 pF.

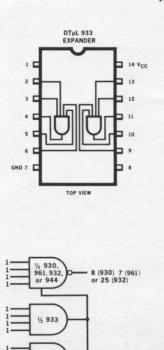

# DT<sub>µ</sub>L 933 EXTENDER

The  $DT\mu L$  933 is a Dual Input-Extender consisting of two independent diode arrays identical in every respect to the input diodes of the  $DT\mu L$  Gate and Buffer elements. Good practice dictates that extension interconnection paths be as short as possible to minimize the effects of distributed capacitance on circuit performance.

Typical input capacitance of  $DT\mu L$  933 is 2 pF, output capacitance is 5 pF.

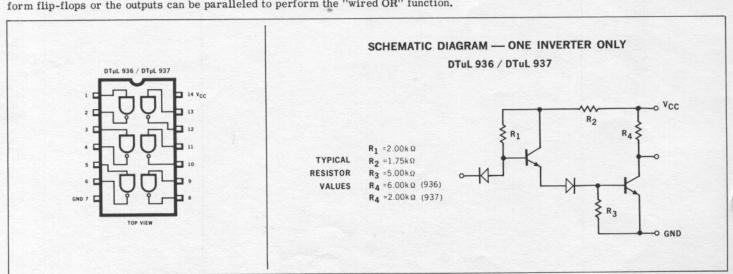

#### DTul 936 • DTul 937 - HEX INVERTER

The  $DT_{\mu}L$  936 hex inverter has input-output characteristics identical to the other  $DT_{\mu}L$  gates. Inverters can be cross-connected to form flip-flops or the outputs can be paralleled to perform the "wired OR" function.

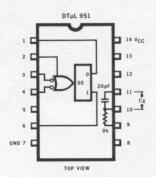

### DTµL 951 - MONOSTABLE MULTIVIBRATOR

The  $DT\mu L$  951 is an integrated monostable multivibrator designed for use with other members of the  $DT\mu L$  family. It provides complementary output pulses which are typically 100 ns wide. This pulse width is adjustable by the addition of external components.

#### **ABSOLUTE MAXIMUM RATINGS**

(above which useful life may be impaired)

Supply Voltage (VCC),

-55°C to +125°C, continuous:

+8.0 Volts

Supply Voltage (VCC),

pulsed, <1 second:

+12 Volts

Output Current, into outputs:

50 mA

Current into Pin 10

5.0 mA

Input Forward Current

-10 mA

Input Reverse Current

1.0 mA

#### INPUT-OUTPUT LOAD FACTORS TO DT<sub>H</sub>L FAMILY

Each DT $\mu$ L 951 input should be rated at 2 loads. Each DT $\mu$ L 951 output may drive 10 DT $\mu$ L loads.

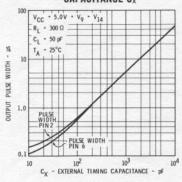

#### OUTPUT PULSE WIDTH VERSUS EXTERNAL TIMING CAPACITANCE Cx

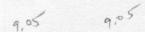

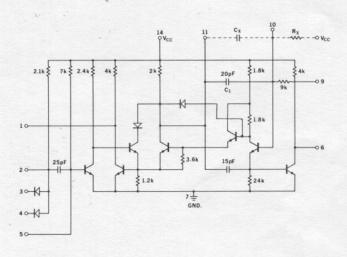

#### SCHEMATIC DIAGRAM

#### RULES FOR USE OF DT<sub>µ</sub>L 951

- 1. With Pin 9 connected to  $V_{CC}$  and no external capacitor  $(C_x)$ , the output pulse width is approximately 100 ns.

- 2. With Pin 9 connected to  $V_{CC}$  and an external capacitor  $(C_x)$  connected between Pins 10 and 11, the output pulse width (T) is:  $T \approx 4.5 \ (C_x + 20)$  with  $C_x$  in pF and T in ns.

- 3. For improved pulse width control, Pin 9 is left open and a stable external resistor (R $_{_{\rm X}}$ ) of 9 k  $\Omega$  minimum to 15 k  $\Omega$  maximum is connected from Pin 10 to V $_{\rm CC}$ . The output pulse width is given by the expression: T  $\approx$  0.5 R $_{_{\rm X}}$  (C $_{_{\rm X}}$  + 20) with R $_{_{\rm X}}$  in k  $\Omega$ , C $_{_{\rm Y}}$  in pF and T in ns.

- 4. The output duty cycle (pulse width/period) should not exceed 40%. It may be increased to 50% by adding a 2-k  $\Omega$  resistor between Pin 11 and  $V_{CC}$ . Higher duty cycles are obtainable but the output pulse width and performance are less predictable.

- 5. The maximum input fall time to trigger: 25 ns for a 1.0-volt swing. 50 ns for a 2.0-volt swing; 100 ns for a 4.0-volt swing.

- 6. The AC sensitivity of the inputs may be decreased by connecting a capacitor between Pin 5 and ground.

- 7. The minimum pulse width at output Pin 1 is approximately 100 ns. This pulse width may be decreased to 50 ns by connecting a  $10\,k\,\Omega$  resistor between Pin 5 and  $V_{CC}$

#### ABSOLUTE MAXIMUM RATINGS (above which useful life may be impaired)

| Supply Voltage (V <sub>CC</sub> ),                   |            | Input Forward Current | -10 mA          |

|------------------------------------------------------|------------|-----------------------|-----------------|

| -55°C to +125°C, continuous                          | +8.0 Volts | Input Reverse Current | 1.0 mA          |

| Supply Voltage (V <sub>CC</sub> ), pulsed, <1 second | +12 Volts  | Operating Temperature | 0°C to +75°C    |

| Output Current, into outputs                         |            | Storage Temperature   | -65°C to +150°C |

| DT μL 932 & 944                                      | 100 mA     |                       |                 |

| DT μL, except 932 & 944                              | 30 mA      | t. 2                  |                 |

#### INPUT-OUTPUT LOADING FACTORS

The number of elements that may be driven by an output terminal may consist of any combination of elements whose summation of input loading does not exceed the output terminal driving capability.

#### RULES FOR INPUT EXPANSION AND "WIRED OR" CONNECTION

EXTENSION OF INPUTS

#### RULES

- 1. Outputs of  $DT\mu L$  gates with  $6 k\Omega$  pull-up resistors, 930, 946, and 962 may be tied together for the "wired OR" function. Subtract 1 unit fan-out for each added gate. Subtract 5 fan-outs for 6 added gates.

- 2. Outputs of DT  $\mu$ L gates with  $2\,k\,\Omega$  pull-up resistors, 949, 961, and 963 may be tied together for the "wired OR" function. Subtract 2 units of fan-out for each added gate.

- 3. Outputs of DT  $\mu$ L 932 may not be tied together for the 'wired OR' function.