#### Signetics

| 863-                  |

|-----------------------|

|                       |

| June 4, 1990          |

| Product Specification |

|                       |

#### **FEATURES**

- Allows burst-mode access for systems using Nibble/Page/Static column mode DRAMs

- Complete control of DRAM access. acknowledge, refresh and address multiplexing functions

- True RAS interleaving for minimum refresh and RAS precharge over-

- Asynchronous arbitration to speed UP accesses

- Selectable Precharge and Acknowledge times

- Selectable Row address hold times

- Supports CAS before RAS refresh

- Allows control of dynamic RAMs with row access times down to 30ns

- Output drivers designed for incident wave switching

#### DESCRIPTION

The Signetics Burst Mode DRAM Controlier (BMDC) is a high performance memory timing generator designed to support Page, Nibble or Static Column modes of operation in addition to the normal DRAM access cycles. It performs memory access/refresh arbitration, refresh and memory access timing, RAS interleaving, CAS byte decoding and controls up to four banks of DRAM.

The BMDC generates DRAM timing and thus requires a companion address multiplexer like the 74F1762 Memory Address Multiplexer for row and column address generation. This provides the flexibility of using the controller with any size of DRAM array by simply using an appropriate address multiplexer. For example when used NOTE: DRAMs

# FAST 74F1766 **Burst Mode DRAM** Controller (BMDC)

| TYPE    | TYPICAL IMAX | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|---------|--------------|-----------------------------------|

| 74F1766 | 150MHz       | 200mA                             |

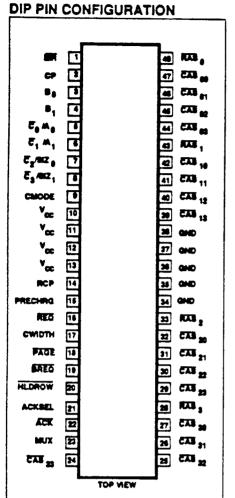

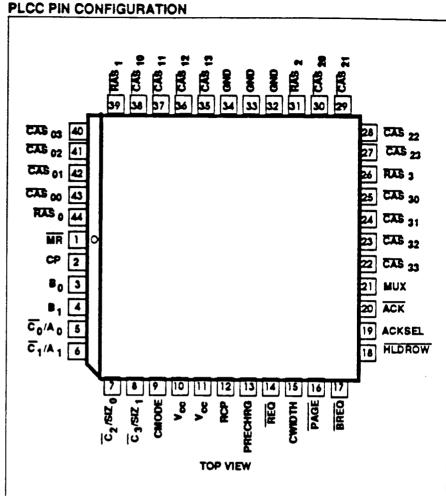

# ORDERING INFORMATION

| PACKAGES           | COMMERCIAL RANGE  V <sub>CC</sub> = 5V±10%; T <sub>A</sub> = 0°C to +70°C |

|--------------------|---------------------------------------------------------------------------|

| 48-Pin Plastic DIP | N74F1766N                                                                 |

| 44-Pin PLCC        | N74F1766A                                                                 |

# INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

|    | PINS                                                                                                                                       | DESCRIPTION                   | 74F(U.L.)<br>HIGH/LOW | LOAD VALUE<br>HIGH/LOW |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|------------------------|

|    | C <sub>0</sub> /A <sub>0</sub> , C <sub>1</sub> /A <sub>1</sub> ,<br>C <sub>2</sub> /SIZ <sub>0</sub> , C <sub>3</sub> /SIZ <sub>1</sub> , | CAS Enable inputs             | 1.0/1.0               | 20µA/0.6mA             |

|    | PRECHAG                                                                                                                                    | RAS Precharge Select Input    | 1.0/1.0               | 20µA/0.6mA             |

|    | REC                                                                                                                                        | Memory access request input   | 1.0/1.0               | 20µA/0.6mA             |

| ١, | CP                                                                                                                                         | Clock input                   | 1.0/1.0               | 20µA/0.6mA             |

|    | RCP                                                                                                                                        | Refresh clock input           | 1.0/1.0               | 20µA/0.6mA             |

|    | B <sub>0</sub> , B <sub>1</sub>                                                                                                            | Bank select inputs            | 1.0/1.0               | 20µA/0.6mA             |

| .  | MR                                                                                                                                         | Reset input                   | 1.0/1.0               | 20µA/0.6mA             |

| 1  | BREQ                                                                                                                                       | Burst request input           | 1.0/1.0               | 20µA/0.6mA             |

|    | ACKSEL                                                                                                                                     | Acknowledge select input      | 1.0/1.0               | 20µA/0.6mA             |

| ١, | HLDROW                                                                                                                                     | Row address hold select input | 1.0/1.0               | 20µA/0.6mA             |

| !  | PAGE                                                                                                                                       | Page mode select input        | 1.0/1.0               | 20µA/0.6mA             |

|    | CMODE                                                                                                                                      | CAS mode select input         | 1.0/1.0               | 20uA/0.6mA             |

| L  | CWIDTH                                                                                                                                     | CAS width select input        | 1.0/1.0               | 20µA/0.6mA             |

|    | ACK                                                                                                                                        | Acknowledge output            | 750/40                | 3.0mA/24mA             |

| L  | MUX                                                                                                                                        | Address Multiplexer output    | 150/40                | 15.QmA/24mA            |

| L  | FAS <sub>0-3</sub>                                                                                                                         | Row address strobe outputs    | 750/40                | 15.0mA/24mA            |

|    | CAS <sub>00-33</sub>                                                                                                                       | Column address strobe outputs | 750/40                | 15.0mA/24mA            |

with the 74F1762, it can control 4Mbit 1.One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.8mA in the Low state

| PIN DESCRI | PTION |  |

|------------|-------|--|

|------------|-------|--|

| SYMBOL               | DIP              | PLCC             | TYPE   | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                 |

|----------------------|------------------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СР                   | 2                | 2                | Input  | Clock input. Used by the controller for all timing and arbitration functions.                                                                                                                                                                                                                                     |

| RCP                  | 14               | 12               | Input  | Refresh clock input. Divided internally by 64 to produce an internal Refresh Requist.                                                                                                                                                                                                                             |

| PRECHING             | 15               | 13               | Input  | RAS Precharge input. A Low will program the Controller to guarantee 4 CP clock cycles of precharge. A High will guarantee 3 clock cycles of precharge.                                                                                                                                                            |

| REC                  | 16               | 14               | input  | Active Low Memory Access Request input, must be asserted for the entire DRAM access cycle. REQ is sampled on the rising edge of the CP clock.                                                                                                                                                                     |

| B <sub>o</sub> .B,   | 3,4              | 3,4              | Input  | RAS Bank Select inputs. See Table 1 for decoding information.                                                                                                                                                                                                                                                     |

| BREQ                 | 19               | 17               | Input  | Active Low Burst Request input. If active during an access cycle, the controller automatically toggles CAS, outputs for burst access. The duration of the CAS, outputs are controlled by the CWIDTH and PAGE inputs.                                                                                              |

| ACKSEL               | 21               | 19               | Input  | Acknowledge timing Select input. A Low will program the Controller to assert ACK output 2 CP clock cycles after CAS, is asserted. When High ACK output will be asserted at the time of assertion of CAS.                                                                                                          |

| HLDROW               | 20               | 18               | Input  | Row Address Hold input. A Low will program the Controller to assert MUX output 1/2 CP clock cycles after RAS <sub>v</sub> is asserted. When High MUX output will be asserted at the time of assertion of RAS <sub>v</sub> .                                                                                       |

| ACK                  | 22               | 20               | Output | Active Low, 3-state Acknowledge output. Asserted as selected by the ACKSEL input. This is asserted only once during a burst or non-burst memory access cycle, and is not asserted during a memory refresh cycle.                                                                                                  |

| CMODE                | 9                | 9                | Input  | $\overline{\text{CAS}}$ Mode select input. When Low $\overline{\text{CAS}}_{\text{x}}$ outputs are enabled directly by the $\overline{\text{C}}_{0.3}$ inputs. When High $\overline{\text{CAS}}_{\text{x}}$ outputs are enabled by decoding the $A_{0.1}$ and $\overline{\text{SiZ}}_{0.1}$ inputs (see Table 2). |

| ਟ₀∕∧₀                | 5                | 5                | Input  | CAS <sub>X0</sub> enable input. As selected by the CMODE input. "X" indicates Banks 0-3.                                                                                                                                                                                                                          |

| ੋ (A,                | 6                | 6                | Input  | CAS <sub>X1</sub> enable input. As selected by the CMODE input. "X" indicates Banks 0-3.                                                                                                                                                                                                                          |

| Cz/siz               | 7                | 7                | Input  | CAS <sub>X2</sub> enable input. As selected by the CMODE input, "X" indicates Banks 0-3.                                                                                                                                                                                                                          |

| C₃/siz,              | 8                | 8                | input  | CAS <sub>X3</sub> enable input. As selected by the CMODE input, "X" indicates Banks 0-3.                                                                                                                                                                                                                          |

| RAS <sub>0-3</sub>   | 48,43,           | 44,39,           | Output | Active Low Row Address Strobe outputs. Asserted as dictated by the Boat inputs.                                                                                                                                                                                                                                   |

| 0-3                  | 33,28            | 31,26            | Обфа   | (see Table 1 for decoding information)                                                                                                                                                                                                                                                                            |

| CWIDTH               | 17               | 15               | Input  | CAS, pulse Width select input. This input selects the initial CAS, pulse width in the burst mode. When Low the initial CAS, pulse is selected equal to 3 CP clock cycles and when High it's selected equal to 2 CP clock cycles. This input is ignored in the non-burst mode.                                     |

| MUX                  | 23               | 21               | Output | Row/Column address Multiplex output. Asserted as selected by the HLDROW input and is used by an external address multiplexer like the 74F1762.                                                                                                                                                                    |

| CAS <sub>00-33</sub> | 47-44,<br>42-39, | 43-40,<br>38-35, | Output | Active Low Column Address Strobe outputs. Asserted when enabled by the CAS <sub>X</sub> enable inputs (Table 2) and RAS <sub>X</sub> bank circuitry.                                                                                                                                                              |

|                      | 32-29,           | 30-27,           |        |                                                                                                                                                                                                                                                                                                                   |

|                      | 27-24            | 25-22            |        |                                                                                                                                                                                                                                                                                                                   |

| PAGE                 | 18               | 16               | Input  | PAGE mode select input. Controls CAS, pulse width after the initial CAS, pulse in the burst mode. When this input is Low the CAS, pulse is selected equal to 2 CP cycles and when High it's selected equal to 1 CP cycle. This is ignored in the non-burst mode.                                                  |

| MR                   | 1                | 1                | Input  | Active Low Master Reset input. The first Low to High transition on the CP clock after RESET is Low will reset the controller. After reset, the 74F1766 remains in test mode until the first rising edge of CP clock.                                                                                              |

| Vœ                   | 10-13            | 10,11            |        | Power                                                                                                                                                                                                                                                                                                             |

| GND                  | 34-38            | 32-34            |        | Ground                                                                                                                                                                                                                                                                                                            |

FAST 74F1766

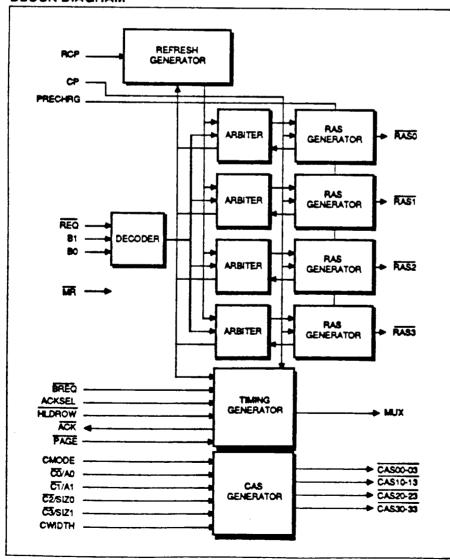

#### ARCHITECTURE

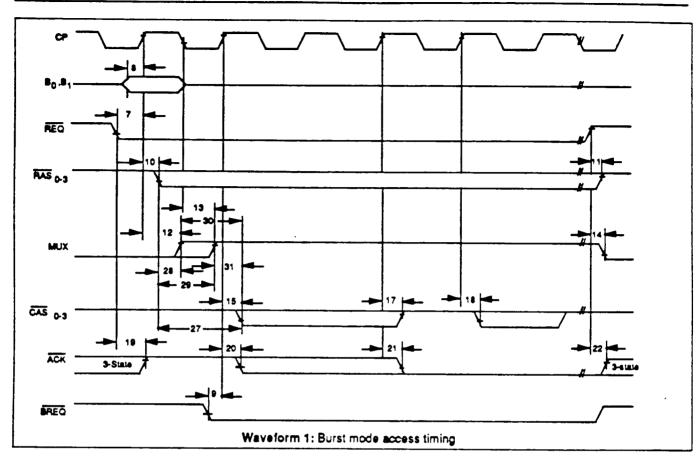

The 74F1766 Burst Mode DRAM controller is a synchronous device, with all signal generation being a function of the input clock (CP).

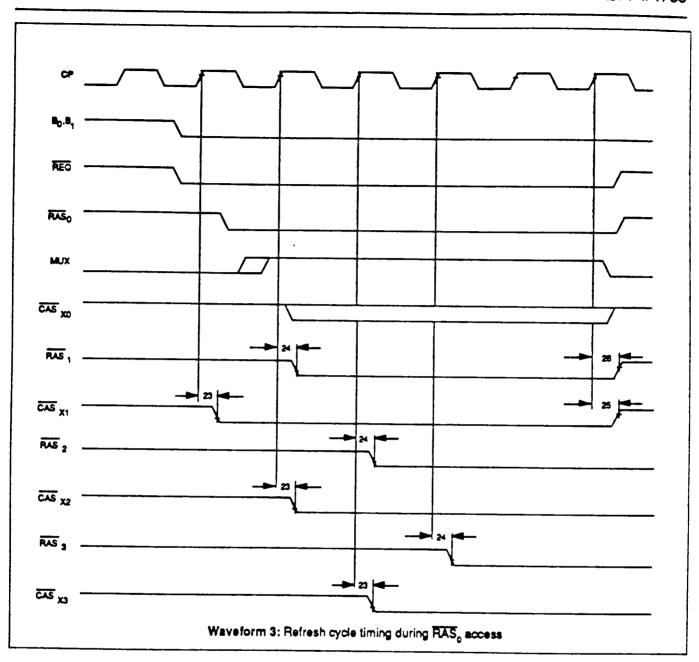

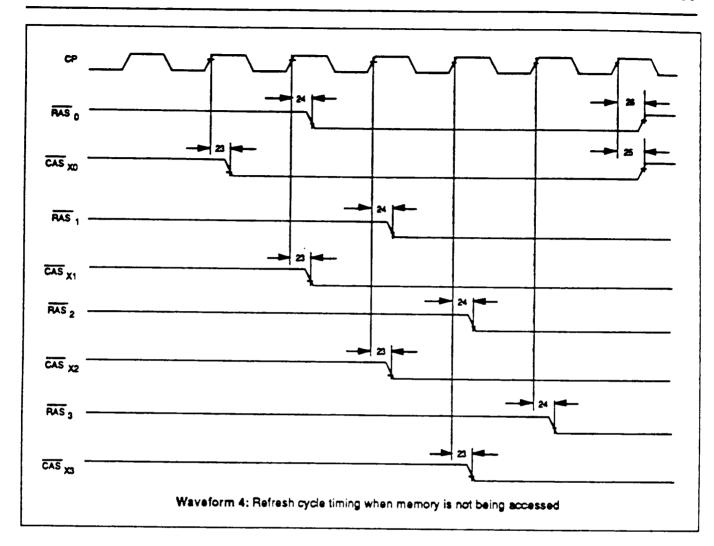

The F1766 Block Diagram (Figure 1) shows the overall architecture of the device. The refresh generator uses CAS before RAS refresh and produces refresh requests based upon the frequency of the refresh clock (RCP). A memory refresh request is generated for all four banks every 64 cycles of the RCP clock. This request is arbitrated individually for all banks with it's corresponding memory access request made through the REQ input. If both memory access and refresh requests are active at a given time the request sampled first will begin immediately and the other request (if still asserted) will be serviced upon completion of the current cycle and it's associated precharge time.

Every one of the four banks have individual refresh monitors to keep track of any missed refreshes during a long page mode access. A total of 127 missed refreshes can be stored by each bank. After the page mode access cycle the controlier will burst refresh that bank until all missed refreshes have been performed. in order to limit the number of outputs switching at the same time the refresh generator will stagger the refresh cycles to individual banks, starting from Bank 0. The bank select inputs (B, 1) select which RAS, output will be enabled during the access cycle. Each RAS output has it's own arbiter and timing generator to allow true RAS interleaving between access cycles and refresh cycles. This also enables transparant RAS precharge between access cycles. The RAS precharge time can be selected by the PRECHRG input to be equal to either 3 or

4 CP clock cycles.

The timing generator allows burst or nonburst accesses selected by the BREQ input. # BREQ input is asserted during a memory access cycle the controller will automatically toggle CAS, outputs for burst accesses. The duration of the first CAS, pulse is determined by the CWIDTH input, and by the PAGE input for subsequent CAS, pulses. This is particularly useful when block moves are made into and out of memory for cache transfers. The CAS, outputs may be gated by the byte select inputs ( $C_{0,a}$ ) or by a decoding function generated by the  $A_{\rm p}/A_{\rm p}/SIZ_{\rm p}/s$ SIZ, using the CMODE input. Each RAS output has an associated set of CAS outputs for that bank, for example RAS, uses CAS outputs. This allows simultaneous refresh of RAS banks while another bank is being accessed by the processor.

The ACKSEL input allows the assertion of Acknowledge (ACK) output to be either when CAS, is asserted or 2 CP clock cycles after that. ACK stays asserted in the burst mode until REQ is negated. The HLDROW input can be used to assert MUX output when RAS, is asserted or one-half CP clock cycle after that.

**FUNCTIONAL DESCRIPTION**

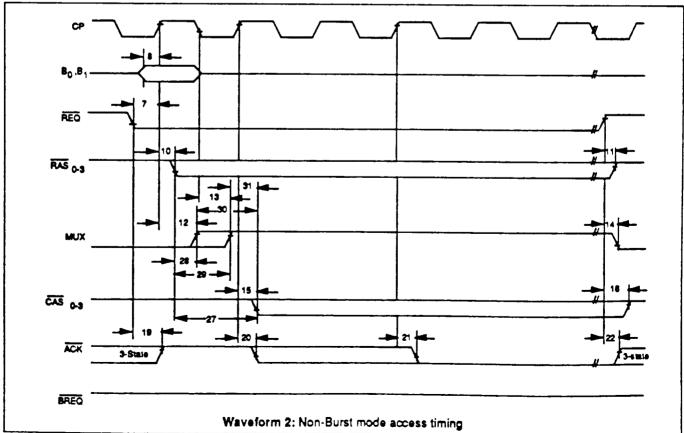

Most DRAMs require that RAS and CAS inputs be toggled a number of times before the DRAM may be used. The BMDC has an initialization feature which allows the automatic excersizing of the DRAMs. This is done by resetting the device. which forces the refresh counter to be offset by ten, thus forcing ten refresh cycles before allowing any memory access cycles. The REQ input is sampled on the rising edge of the CP clock. If no refresh request is being serviced, one of the RAS, outputs (depending on the Boninputs). Will be asserted immediately. Depending on the state of the HLDROW input, the MUX output will be driven High either at the assertion of RAS, or onehalf CP cycle after that. One CP cycle after the assertion of RAS, the CAS, outputs enabled either by the Conjunction of A./A./SIZ,/ SIZ, (as selected by the CMODE input) will be asserted. If the ACKSEL input is High, the ACK output will be asserted at this time; otherwise it will be asserted 2 CP cycles after this time.

The BREQ input is sampled when the CAS, outputs are initially asserted, and this determines what will take place on the CAS, outputs after their initial assertion. If BREQ is High, the RAS, MUX and CAS, outputs will remain in their present state until the negation of REQ, at which time all these signals are negated. Negation of REQ is asynchronous to the CP clock cycle and therefore is not sampled

#### **BLOCK DIAGRAM**

FAST 74F1766

by the clock. If the BREQ is Low at the assertion of CAS, the RAS, and MUX outputs will stay in their existing state but the CAS, outputs after staying Low for 2 CP cycles will alternately be negated and asserted for one CP clock cycle if PAGE input is High or for two CP clock cycles if PAGE input is Low. This process will continue untill the negation of the REQ input, at which time the RAS, MUX, CAS, and ACK outputs will be negated.

As mentioned before, the controller guarantees a RAS precharge on all the RAS, outputs to be either 3 or 4 CP clock cycles as selected by the PRECHRG input. This precharge function is independent among the RAS, outputs, which means that, by connecting the appropriate low-order address lines from the processor to the B<sub>0.1</sub> inputs, sequential accesses, a common occurance with microprocessors, will result in no precharge overhead.

The refresh function is also independent

between the RAS, outputs, which means that three RAS, outputs can be performing a CAS before RAS refresh, while the fourth is in the precharge mode or is being accessed, thus reducing the overall refresh overhead.

**Output driving Characteristics**

Considering the transmission line characteristics of the DRAM arrays, the outputs of the DRAM controller have been designed to provide incident-edge switching (in Dual-Inline-Packaged memory ar rays), needed in high performance systems. For more information on the driving characteristics, please refer to Signetics application note number AN218. The driving characteristics of the 74F1766 are the same as those of the 74F765 shown in the application note.

Testing the BMDC

Precautions have been taken in the design of the BMDC to facilitate testing of the device. After a MR is issued and the

CP input is toggled from Low to High all internal flip-flops are brought into a known state, and the device goes into the test mode from the time MR is deasserted till the time the first Low to High transition occurs on the CP clock. During the test mode, bank refresh counters (that keep track of missed refreshes) are clocked by a High to Low transition on the  $\overline{C}_{0.3}$  inputs and the main refresh counter is clocked on the rising RCP clock edge. The comparators that compare the contents of the main refresh counter and refresh counters of individual banks are clocked by the Low to High transition on the PRECHRG input and are gated on to RAS, outputs by the C. inputs. So whenever C. are Low, RAS outputs are disabled (pulled High). If the contents of the main refresh counter and the individual bank counters are equal, the corresponding RAS output will be High, if not equal the corresponding RAS output will be Low. This allows full testing of the Counters and comparators with relatively few lines of code.

| Во | ₿, | RAS <sub>o</sub> | RAS, | RAS, | RAS, |

|----|----|------------------|------|------|------|

| 0  | ٥  | 0                | 1    | 1    | 1    |

| 0  | 1  | 1                | Ó    | 1    | 1    |

| 1  | 0  | 0                | 1    | 0    | 1    |

| 1  | 1  | 0                | 1    | 1    | 0    |

**TABLE 1: BANK SELECT DECODE**

| CMODE       | OPERATION   | ₹sız,       | C₂⁄sız₀ | ₹,/A,            | C <sub>0</sub> /A <sub>0</sub> | CAS <sub>xs</sub> | CAS <sub>x2</sub> | CAS <sub>x1</sub> | CAS <sub>xo</sub> |

|-------------|-------------|-------------|---------|------------------|--------------------------------|-------------------|-------------------|-------------------|-------------------|

| 1<br>1<br>1 | LONG WORD   | 0 0 0       | 0 0 0   | 0<br>0<br>1<br>1 | 0 1 0 1                        | 0 0 0             | 0<br>0<br>0       | 0<br>0<br>1<br>1  | 0 1 1 1           |

| 1<br>1<br>1 | BYTE        | 0 0 0       | 1 1 1   | 0 0 1 1          | 0<br>1<br>0                    | 1 1 0             | 1<br>1<br>0<br>1  | 1<br>0<br>1       | 0<br>1<br>1       |

| 1<br>1<br>1 | WORD        | 1 1 1       | 0 0 0   | 0 0 1 1          | 0<br>1<br>0                    | 1<br>1<br>0<br>0  | 1<br>0<br>0       | 0 0 1 1           | 0 1 1 1           |

| 1 1 1 1     | THREE BYTES | 1<br>1<br>1 | 1 1 1   | 0 0 1 1          | 0<br>1<br>0<br>1               | 1 0 0 0           | 0 0 1             | 0 0 1 1           | 0 1 1 1           |

**TABLE 2: BYTE SELECT DECODE**

FAST 74F1766

# ABSOLUTE MAXIMUM RATINGS (Operation beyond the limits set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the operating free-air temperature range.)

| PARAMETER                                      | RATING                                                                                                                                                                       | UNIT                                                                                                                                                                                                                                                                         |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Supply voltage                                 | -0.5 to +7.0                                                                                                                                                                 | V                                                                                                                                                                                                                                                                            |  |  |

| Input voltage                                  | -0.5 to +7.0                                                                                                                                                                 | V                                                                                                                                                                                                                                                                            |  |  |

| Input current                                  | -30 to +5                                                                                                                                                                    | mA                                                                                                                                                                                                                                                                           |  |  |

| Voltage applied to output in High output state | -0.5 to +V                                                                                                                                                                   | V                                                                                                                                                                                                                                                                            |  |  |

| Current applied to output in Low output state  | 500                                                                                                                                                                          | mA                                                                                                                                                                                                                                                                           |  |  |

| Operating free-air temperature range           | 0 to +70                                                                                                                                                                     | •c                                                                                                                                                                                                                                                                           |  |  |

| Storage temperature                            | -65 to +150                                                                                                                                                                  | •c                                                                                                                                                                                                                                                                           |  |  |

|                                                | Supply voltage Input voltage Input current Voltage applied to output in High output state Current applied to output in Low output state Operating free-air temperature range | PARAMETER RATING  Supply voltage -0.5 to +7.0  Input voltage -0.5 to +7.0  Input current -30 to +5  Voltage applied to output in High output state -0.5 to +V <sub>CC</sub> Current applied to output in Low output state 500  Operating free-air temperature range 0 to +70 |  |  |

# RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PA                                 |                     | · · · · · · · · · · · · · · · · · · · |              |     |      |

|-----------------|------------------------------------|---------------------|---------------------------------------|--------------|-----|------|

|                 |                                    | PARAMETER           |                                       |              | Max | UNIT |

| V <sub>∞</sub>  | Supply voltage                     | 4.5                 | 5.0                                   | 5.5          | V   |      |

| V <sub>M</sub>  | High-level input voltage           | 2.0                 |                                       |              |     |      |

| V <sub>L</sub>  | Low-level input voltage            |                     |                                       | <del>-</del> | 0.8 | ٧    |

| l <sub>sc</sub> | input clamp current                |                     |                                       |              | -18 | mA   |

| I <sub>OH</sub> | High-level output current          | All pins except ACK |                                       |              | -15 | mA   |

| OH              |                                    | ACK output          |                                       |              | -3  | mA   |

| loc             | Low-level output current           |                     |                                       |              | 24  | mA   |

| TA              | Operating free-air temperature rai | nge                 | 0                                     |              | 70  | •c   |

FAST 74F1766

#### DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

| SYMBOL             | PARAMETER                                               | 1                      |                                                                                            |                         |                     | LIMITS   |                                                  |      |      |

|--------------------|---------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------|-------------------------|---------------------|----------|--------------------------------------------------|------|------|

|                    | PARAMETER                                               |                        | TEST CONDITIONS <sup>1</sup>                                                               |                         |                     |          | Typ <sup>2</sup>                                 | Mex  | UNIT |

| V <sub>ОН</sub>    |                                                         | All pins               | V <sub>CC</sub> = MIN,                                                                     | 1 -15-4                 | ±10%V <sub>CC</sub> | 2.5      | 3.2                                              |      | V    |

|                    |                                                         | except ACK             | V. = MAX,                                                                                  | l <sub>OH</sub> =15mA   | ±5%√∞               | 2.7      | 3.4                                              |      | V    |

| VOH2               | High-level output voltage                               |                        | V <sub>IH</sub> = MIN                                                                      | I <sub>OH2</sub> 335mA  | ±5%V∞               | 2.4      |                                                  |      | ٧    |

| V <sub>OH</sub>    |                                                         | ACK                    | V <sub>CC</sub> = MIN,<br>V <sub>L</sub> = MAX,<br>V <sub>H</sub> = MIN                    | I -MAY                  | ±10%V <sub>CC</sub> | 2.4      |                                                  |      | V    |

| - UH               |                                                         | ACA                    | VIH = MIN                                                                                  | I <sub>OH</sub> =MAX    | ±5%V <sub>0</sub>   | 2.7      | 3.3                                              |      | ٧    |

| V <sub>OL</sub>    |                                                         |                        | V <sub>CC</sub> = MIN,                                                                     | I <sub>OL</sub> =24mA   | ±10%V <sub>CC</sub> |          | 0.35                                             | 0.50 | V    |

|                    | ·                                                       | All pins<br>except ACK | V <sub>E</sub> = MAX,<br>. V <sub>EH</sub> = MIN                                           | 1                       | ±5%∨ <sub>CC</sub>  |          | 0.35                                             | 0.50 | V    |

| V <sub>OL2</sub> 3 | Low-level output voltage                                |                        |                                                                                            | I <sub>OL2</sub> 3=60mA | #5%V <sub>CC</sub>  |          | 0.45                                             | 0.80 | ٧    |

|                    |                                                         |                        | V <sub>CC</sub> = MIN,                                                                     |                         | ±10%V <sub>CC</sub> |          | 0.35                                             | 0.50 | V    |

| V <sub>OL</sub>    |                                                         | ACK                    | V <sub>IL</sub> = MAX,<br>V <sub>IH</sub> = MIN                                            | I <sub>OL</sub> =MAX    | ±5%√ <sub>CC</sub>  |          | 0.35                                             | 0.50 | V    |

| V <sub>IK</sub>    | Input clamp voltage                                     |                        | V <sub>CC</sub> = MIN, I,                                                                  | · lac                   |                     | <u> </u> | -0.73                                            | -1.2 | V    |

| 1,                 | Input current at maximum                                | nput voltage           | V <sub>CC</sub> =0.0V, V <sub>I</sub> = 7.0V                                               |                         |                     |          |                                                  | 100  | μA   |

| <sup>1</sup> нн    | High-level input current                                |                        | V <sub>CC</sub> =MAX, V <sub>1</sub> = 2.7V                                                |                         |                     | <u> </u> | <del>                                     </del> | 20   | μA   |

| I <sub>IL</sub>    | Low-level input current                                 |                        | V <sub>CC</sub> =MAX, V <sub>i</sub> = 0.5V                                                |                         |                     |          | ļ ——                                             | -0.6 | ·m/  |

| l <sub>OZH</sub>   | Off-state output current,<br>High level voltage applied |                        | V <sub>CC</sub> =MAX, V <sub>o</sub> = 2.7V<br>V <sub>CC</sub> =MAX, V <sub>o</sub> = 0.5V |                         |                     |          |                                                  | 50   | μA   |

| lozı.              | Off-state output current,<br>Low level voltage applied  |                        |                                                                                            |                         |                     |          |                                                  | -50  | μΔ   |

| los <sup>4</sup>   | Short-circuit                                           |                        | V <sub>CC</sub> =MAX                                                                       | All pins                | xcept ACK           | -100     |                                                  | -225 | m/   |

| ·os                | output current                                          |                        | ·œ-····                                                                                    | XCK out                 | put                 | -60      |                                                  | -150 | m/   |

| <sup>1</sup> cc    | Supply current                                          | ГССН                   | V <sub>CC</sub> =MAX                                                                       |                         |                     |          | 185                                              | 240  | m/   |

|                    | (total)                                                 | loca                   | ••                                                                                         |                         |                     |          | 200                                              | 260  | mA   |

#### NOTES:

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

3. 1<sub>OH</sub> <sup>2</sup> a. 1<sub>OH</sub> <sup>2</sup> are transient currents necessary to guarantee a Low to High & a High to Low transition in a 30 OHM transmission line respectively. Refer to Application note number AN218 for further explanation.

<sup>4.</sup> Not more than one output should be shorted at a time. For testing los, the use of high-speed test apparatus and/or sample-and-hold techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting of a High output may raise the chip temperature. well above normal and thereby cause invalid readings in other parameter tests. In any sequence of parameter tests, to tests should be performed last.

### AC ELECTRICAL CHARACTERISTICS

|    |                                                                                          |                 | LIMITS |                                                                           |              |                                                                  |        |     |

|----|------------------------------------------------------------------------------------------|-----------------|--------|---------------------------------------------------------------------------|--------------|------------------------------------------------------------------|--------|-----|

| NO | PARAMETER                                                                                | TEST CONDITIONS |        | T <sub>A</sub> =25<br>V <sub>e=</sub> +5.0\<br>C <sub>L</sub> =30<br>RL=7 | /±10%<br>0pF | T <sub>A</sub> =0°C<br>V <sub>ac</sub> =+5.<br>C <sub>L</sub> =3 | UNI    |     |

| 1  |                                                                                          |                 | Min    | Тур                                                                       | Max          | Min                                                              | Max    | ]   |

| 1  | CP clock period (tcp)                                                                    |                 | 10     |                                                                           |              | 10                                                               |        | ns  |

| 2  | CP clock low time                                                                        |                 | 4      |                                                                           |              | 4                                                                |        | ns  |

| 3  | CP clock high time                                                                       |                 | 6      |                                                                           |              | 6                                                                |        | ns  |

| 4  | RCP clock period                                                                         | ·               | 100    |                                                                           |              | 100                                                              |        | ns  |

| 5  | RCP clock low time                                                                       |                 | 10     |                                                                           |              | 10                                                               |        | ns  |

| 6  | RCP clock high time                                                                      |                 | 10     |                                                                           |              | 10                                                               |        | ns  |

| 7  | Setup time REQ(1) to CP(1)                                                               |                 | 2.5    |                                                                           |              | 4                                                                |        | ns  |

| 8  | Setup time $B_{\bullet}$ , $B_{1}$ to $CP(\hat{1})$                                      |                 | 3      |                                                                           |              | 4                                                                |        | ns  |

| •  | Setup time BREQ to CP(1)                                                                 |                 | 3      |                                                                           |              | 4                                                                |        | ns  |

| 10 | Propagation delay CP(1) to RAS(1)                                                        |                 | 3      | 7.5                                                                       | 9.5          | 3                                                                | 10     | ns  |

| 11 | Propagation delay $\overline{\text{REQ}}(\uparrow)$ to $\overline{\text{RAS}}(\uparrow)$ |                 | 4      | 9                                                                         | 12           | 3                                                                | 13     | ns  |

| 12 | Propagation delay CP(T) to MUX(T)                                                        | HEDROW = 1      | 3      | 8                                                                         | 10           | 3                                                                | 11     | ns  |

| 13 | Propagation delay $CP(1)$ to $MUX(1)$                                                    | HLDROW = 0      | 2      | 5.5                                                                       | 7.5          | 2                                                                | 8.5    | ns  |

| 14 | Propagation delay REQ(1) to MUX(1)                                                       |                 | 4      | 8.5                                                                       | 10.5         | 4                                                                | 11.5   | пз  |

| 15 | Propagation delay CP(T) to CAS(1)                                                        |                 | 3      | 8.5                                                                       | 11.5         | 3                                                                | 12     | ns  |

| 16 | Propagation delay REQ(1) to CAS(1)                                                       |                 | 4      | 9.5                                                                       | 12           | 4                                                                | 14     | ns  |

| 17 | Propagation delay CP(T) to CAS(T)                                                        | BREQ = 0        | 3      | 8                                                                         | 10           | 3                                                                | 11     | ns  |

| 18 | Propagation delay CP(T) to CAS(L)                                                        | BREQ = 0        | 3      | 9                                                                         | 11           | 3                                                                | 12     | ns  |

| 19 | Propagation delay $\overline{REQ}(\downarrow)$ to $\overline{ACK}(3-state to High)$      |                 | 2      | 5                                                                         | 7            | 2                                                                | 8      | ns  |

| 20 | Propagation delay CP(1) to ACK(1)                                                        | ACKSEL = 1      | 3      | 7.5                                                                       | 9.5          | 3                                                                | 10     | ns  |

| 21 | Propagation delay CP( $\hat{T}$ ) to $\overline{ACK}(\downarrow)$                        | ACKSEL = 0      | 3      | 7.5                                                                       | 9.5          | 3                                                                | 10     | ns  |

| 22 | Propagation delay REO(1) to ACK( Low to 3- state)                                        |                 | 2      | 5                                                                         | 7            | 2                                                                | 7.5    | ns  |

| 23 | Propagation delay CP(T) to CAS(L) *                                                      | REFRESH CYCLE   | 4      | 9.5                                                                       | 12           | 4                                                                | 13     | ns  |

| 24 | Propagation delay CP(T) to RAS(1) *                                                      | REFRESH CYCLE   | 3      | 7.5                                                                       | 9.5          | 3                                                                | 10     | ns  |

| 5  | Propagation delay CP(1) to CAS(1) *                                                      | REFRESH CYCLE   | 4      | 9.5                                                                       | 12           | 4                                                                | 14     | ns  |

| e  | Propagation delay CP(T) to RAS(T) *                                                      | REFRESH CYCLE   | 4      | 9                                                                         | 11           | 3                                                                | 13     | ns. |

| 7  | Propagation delay RAS(1) to CAS(1)                                                       |                 | 1tcp-1 | 11cp+1                                                                    | 1tcp+2.5     | 1tcp-1                                                           | 1tcp+3 | ns  |

<sup>\*</sup> The same parameters will hold for a refresh cycle during RAS, RAS, and RAS, access cycles.

FAST 74F1766

# AC ELECTRICAL CHARACTERISTICS

| NO | PARAMETER                          | TEST CONDITIONS | LIMITS                                                                               |            |            |                                                                                                |          |      |

|----|------------------------------------|-----------------|--------------------------------------------------------------------------------------|------------|------------|------------------------------------------------------------------------------------------------|----------|------|

|    |                                    |                 | T <sub>A</sub> =25°C<br>V <sub>a</sub> =>5.0V±10%<br>C <sub>L</sub> =300pF<br>RL=70Ω |            |            | T <sub>A</sub> =0°C to +70°C<br>V <sub>ec</sub> =+5.0V ±10%<br>C <sub>L</sub> =300pF<br>BL=700 |          | UNIT |

|    |                                    |                 | Min                                                                                  | Тур        | Max        | Min                                                                                            | Max      | 1 1  |

| 28 | Propagation delay RAS(1) to MUX(1) | HLDROW = 1      | -1                                                                                   | 0.5        | 2          | -1.5                                                                                           | 2.5      | ns   |

| 29 | Propagation delay FAS(1) to MUX(1) | HLDROW = 0      | 1/2top-3.5                                                                           | 1/2tcp-1.5 | 1/21cp     | 1/2tcp-1.5                                                                                     |          | ns   |

| 30 | Propagation delay MUX(T) to CAS(1) | HLDROW = 1      | 1tcp-1.5                                                                             | 11cp+0.5   | 1tcp+2     | 1tcp-2.5                                                                                       | 1tco+2.5 |      |

| 31 | Propagation delay MUX(1) to CAS(↓) | HLDROW = 0      | 1/21cp+0.5                                                                           | 1/2tcp+2   | 1/21cp+4.5 | 1/2tcp-0.5                                                                                     | ,        |      |

FAST 74F1766

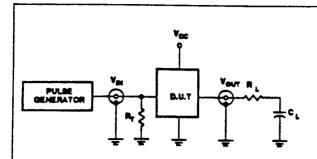

# **TEST CIRCUIT AND WAVEFORMS**

# Test Circuit For Totem-Pole Outputs

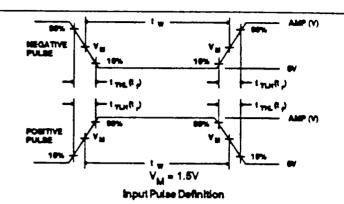

#### **DEFINITIONS**

- R<sub>1</sub> = Load resistor; see AC CHARACTERISTICS for value.

- C<sub>L</sub> = Load capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

- R<sub>T</sub> = Termination resistance should be equal to Z<sub>OUT</sub> of pulse generators.

| FAMILY  | INPUT PULSE REQUIREMENTS |           |       |             |                  |  |  |  |

|---------|--------------------------|-----------|-------|-------------|------------------|--|--|--|

| ( AMIL) | Amplitude                | Rep. Rate | ¹w    | <b>t</b> tH | * <sub>THL</sub> |  |  |  |

| 74F     | 3.0V                     | 1 MHz     | 500ns | 2.5ns       | 2.5ns            |  |  |  |