November 1992

# Intel486™ SL Microprocessor SuperSet Data Book

Order Number: 241325-001

# Intel486™ SL Microprocessor SuperSet

| CONTENTS                                                              | PAGE        | CONTENTS                                                | PAGE        |

|-----------------------------------------------------------------------|-------------|---------------------------------------------------------|-------------|

| 1.0 INTRODUCTION                                                      | 2-6         | 3.0 82360SL I/O SPECIFICA                               | ATIONS 2-79 |

| 1.1 Challenges Faced by the Porta PC Designer                         | ıble<br>2-6 | 3.1 82360SL I/O Pin Assig<br>Signal Characteristics .   | nment and   |

| 1.2 The Intel486™ SL Microproces Superset                             | ssor<br>2-6 | 3.2 82360SL I/O Signal De 3.3 82360SL I/O D.C.          |             |

| 1.3 Setting the Standard for a New Class of Mobile Computers          | ,<br>2-7    | Specifications                                          |             |

| 1.4 Overview of System Architecture                                   |             | 3.3.1 Capacitance D.C. Specifications                   | 2-94        |

| 1.5 Intel486™ SL Microprocessor:                                      |             | 3.3.2 3V D.C. Specifica                                 |             |

| Central Processing Unit (CPU), (                                      | On-         | 3.3.3 5V D.C. Specificat                                | tions 2-95  |

| Chip Cache, On-Chip Floating Po<br>Unit (FPU) and Memory Controll     | oint<br>er  | 3.4 82360SL I/O Timing Specifications                   | 2-97        |

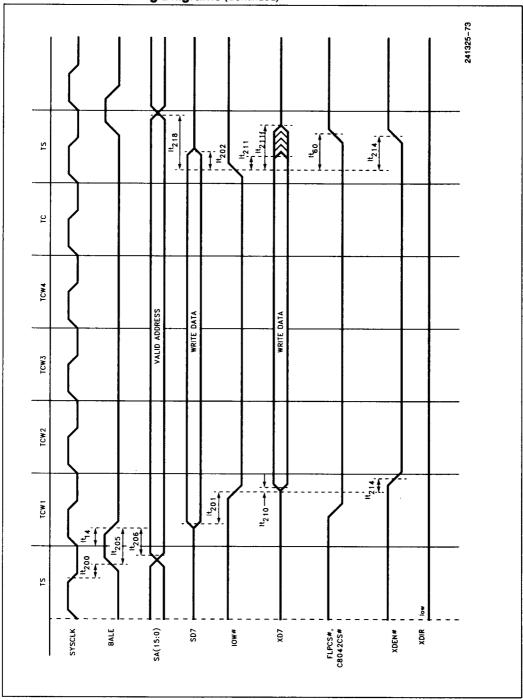

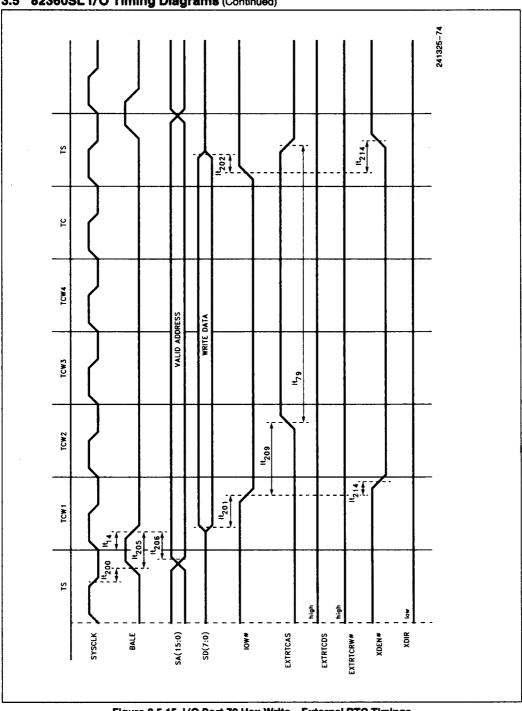

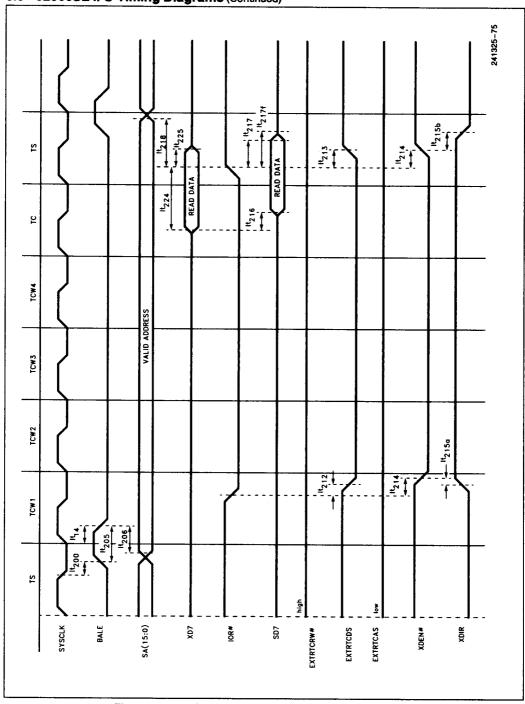

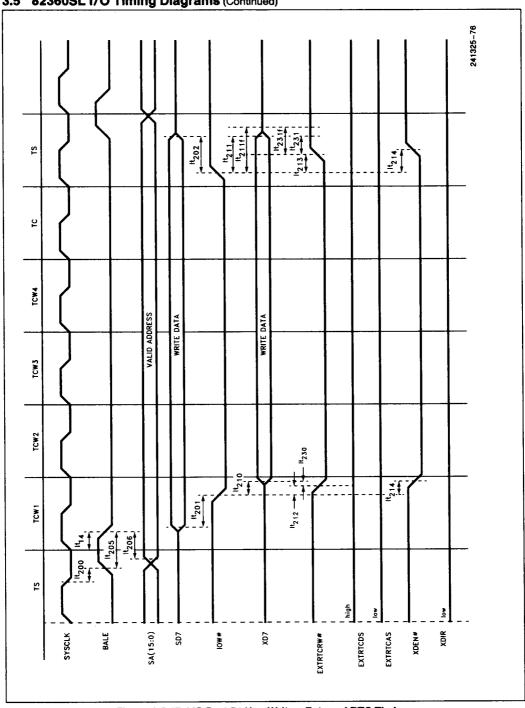

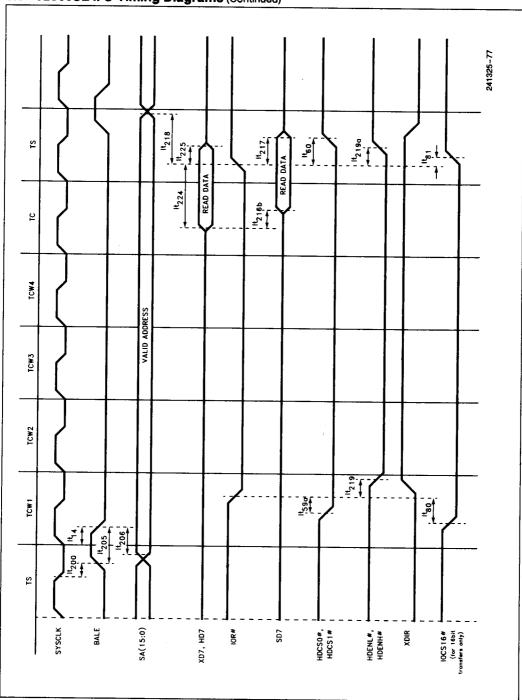

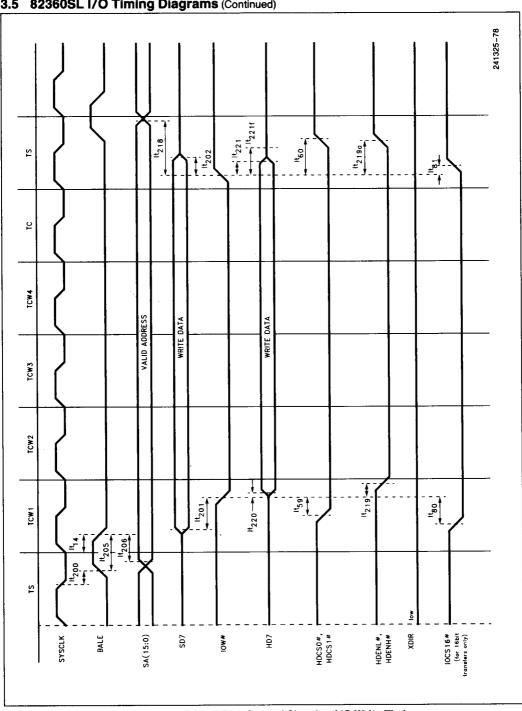

| Subsystem                                                             | 2-9         | 3.5 82360SL I/O Timing D                                |             |

| 1.6 82360SL I/O: Integrated ISA                                       |             | 3.6 Capacitive Derating Inf                             |             |

| Peripheral and Power Managem<br>Device                                | ent<br>2-11 | 82360SL I/O Maximum                                     | Timing      |

| 2.0 Intel486TM SL MICROPROCESS                                        | OR          | Operation                                               | 2-133       |

| SPECIFICATIONS  2.1 Intel486™ SL Microprocessor Assignment and Signal | Pin         | 82360SL I/O Minimum<br>Derating Curves—5V<br>Operation  | ,           |

| Characteristics                                                       | 2-14        | 82360SL I/O Maximum                                     | Timina      |

| 2.2 Intel486TM SL Microprocessor<br>Signal Descriptions               | 2-23        | Derating Curves—3.3 Operation                           | IV 2-136    |

| 2.3 Intel486™ SL Microprocessor Specifications                        | DC<br>2-35  | 82360SL I/O Minimum<br>Derating Curves—3.3<br>Operation | Timing<br>V |

| 2.4 Intel486TM SL Microprocessor<br>Timing Specifications             |             | 3.7 Crystal and Oscillator                              |             |

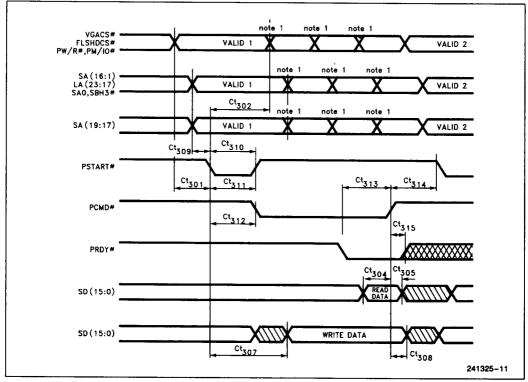

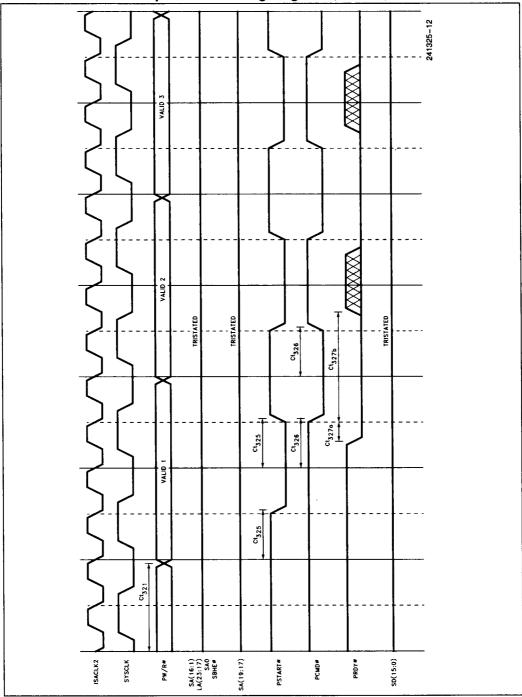

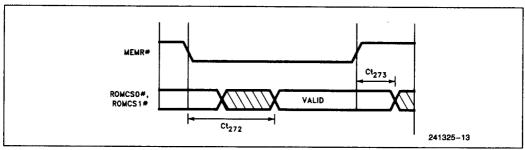

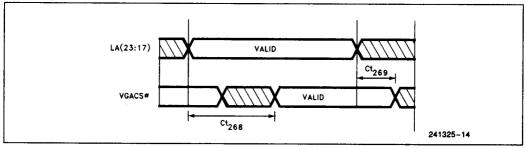

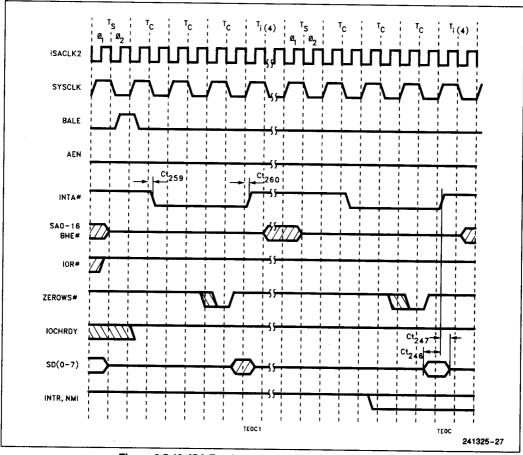

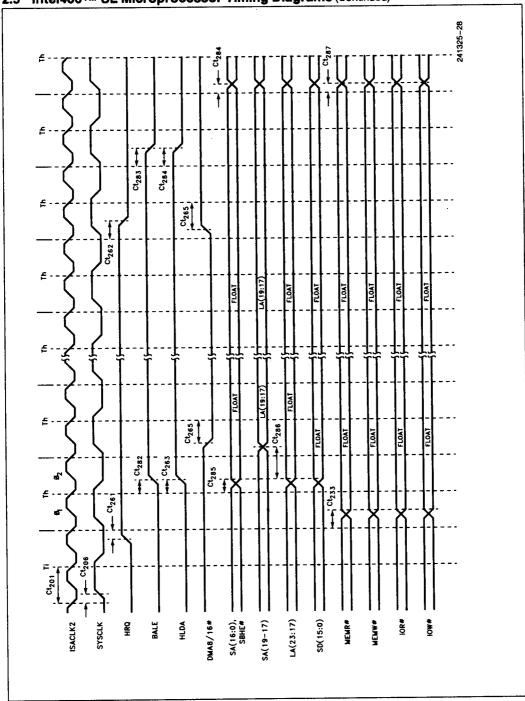

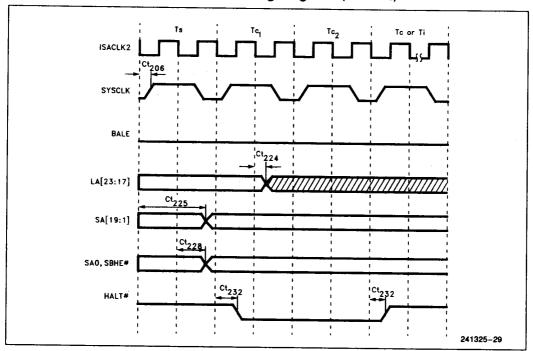

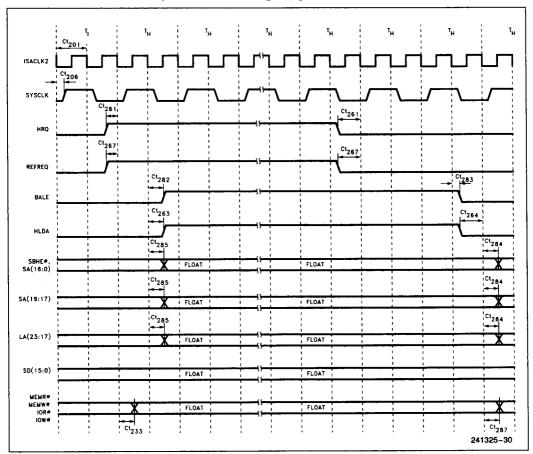

| 2.5 Intel486™ SL Microprocessor Timing Diagrams                       |             | Specifications                                          | 2-139       |

| 2.6 Power Sequencing Specifications                                   |             | 4.0 PACKAGE THERMAL SPECIFICATIONS                      | 2-141       |

| 2.7 JTAG Specifications                                               |             | 5.0 MECHANICAL DETAILS                                  |             |

| 2.8 Capacitive Derating Information                                   |             | PACKAGES                                                | 2-142       |

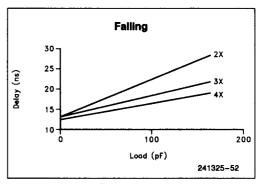

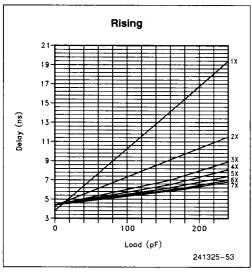

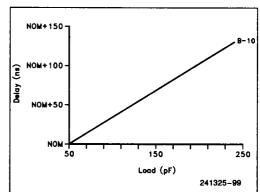

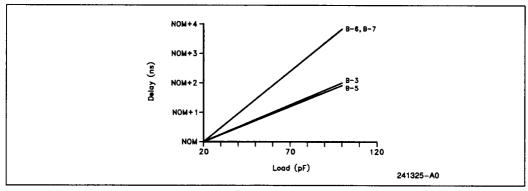

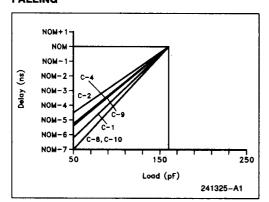

| 2.8.1 Derating Curves for PI- and ISA-Bus Signal Pins                 | d           | 6.0 APPENDIX A RELATED DOCUMENTS                        | 2-150       |

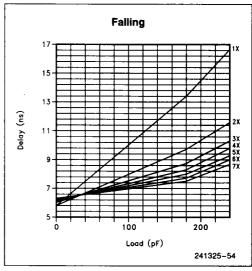

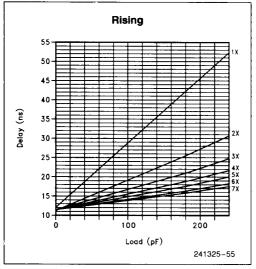

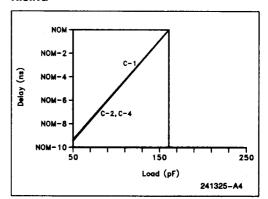

| 2.8.2 Derating Curves for Memo                                        |             |                                                         |             |

## Intel486™ SL MICROPROCESSOR SUPERSET HIGHLY-INTEGRATED STATIC Intel486™ SL MICROPROCESSOR COMPLETE ISA PERIPHERAL SUBSYSTEM SYSTEM-WIDE POWER MANAGEMENT

- Static Intel486™ SL CPU

- Runs MS-DOS\*, WINDOWS\*, OS/2\*\* and UNIX\*\*\*

- Object Code Compatible with Intel 8086, 80286, Intel386™ and Intel486™ Microprocessors

- Architecture Extension for Power Management

- Transparent to Operating Systems and Applications

- Programmable Memory Control

- No-Giue DRAM interface

- 256K to 64 Mbytes

- Complete ISA System, with Extended Support

- Full ISA Bus Control, Status and Address and Data Interface Logic

- Compatible ISA Bus Peripherals

- System I/O Decoding, Programmable Chip Selects and Support Interfaces

- High-Speed Peripheral Bus (PI-Bus Support)

- IdeaPort Interface for Hardware Expansion

The Intel486 SL Microprocessor SuperSet combines an ISA compatible personal computer's microprocessor, memory controller and peripheral subsystems into just two Very Large Scale Integration (VLSI) devices. The product's true Intel486 DX core, high-integration and power conservation features reduce the size and power consumption typically associated with fully Industry Standard Architecture (ISA) bus compatible systems without compromising performance. In addition, new expandability and flexibility features offer the capability for continued innovation in battery-operated, space-constrained systems. The SL SuperSet brings 100% ISA-Bus compatibility to system designs ranging from a new generation of notebook computers to pen-based computers.

<sup>\*</sup>MS-DOS and WINDOWS are trademarks of Microsoft Corporation.

<sup>\*\*</sup>OS/2 is a trademark of International Business Machines Corporation.

<sup>\*\*\*</sup>UNIX is a trademark of UNIX System Laboratories, Inc.

# Intel486™ SL MICROPROCESSOR Intel486 MICROPROCESSOR CORE, WITH INTEGRATED MEMORY CONTROLLER AND SYSTEM POWER MANAGEMENT FULLY-STATIC CHMOS™ V TECHNOLOGY

- Static 3.3V Intel486™ CPU Core

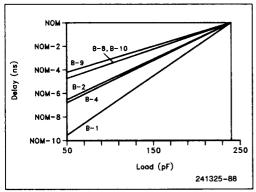

- Optimized and Compatible with Standard Operating System Software such as MS-DOS, WINDOWS, OS/2 and UNIX

- Object Code Compatible with Intel 8086, 80286, Intel386™ and Intel486 Microprocessors

- Runs All Desk-Top Applications, 16-or 32-bit

- D.C. to 33 MHz Operation

- 64 Mbytes Physical Memory/64 Terabytes Virtual Memory

- 4 Gigabyte Maximum Segment Size

- High Integration, Low Power CHMOS™ V Technology

- High Integration Enables On-Chip

- 4-Way Set Associative 8 Kbyte Cache and Cache Controller

- Floating Point Unit

- --- Paged, Virtual Memory Management

- 32-Bit Architecture

- Data Buses

- -- Registers

- 8-, 16-, 32-Bit Data Types

- Transparent Power Management System Architecture

- System Management Mode Architecture

- Extension for Truly Compatible Systems

- Programmable Hardware Supports Custom Power-Control Methods

- **■** Direct Drive Bus Interface

- Full ISA Bus Interface

- High Speed Peripheral Interface (PI)

Bus

- High Performance and Flexible Memory Interface

- 32-Bit DRAM Data Bus

- No-Glue DRAM Interface

- Selectable 3.3V/5V DRAM Interface

- Up to 5 Banks of DRAM, Size of Each and/or Total up to 64 Mbyte

- Each Bank Programmable for Size, Organization, Speed, and Output Buffer Strength

- Burst Mode Supported

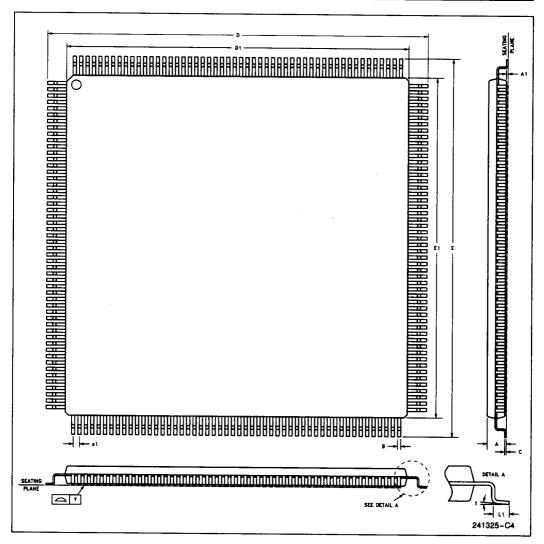

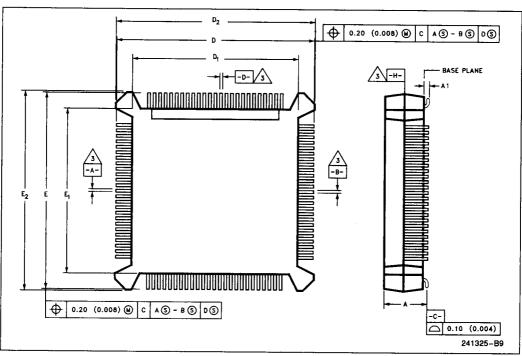

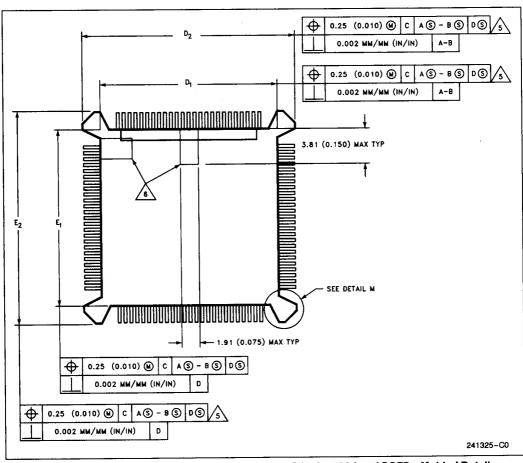

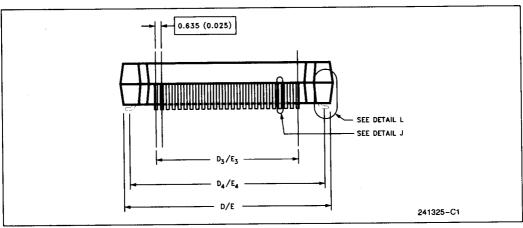

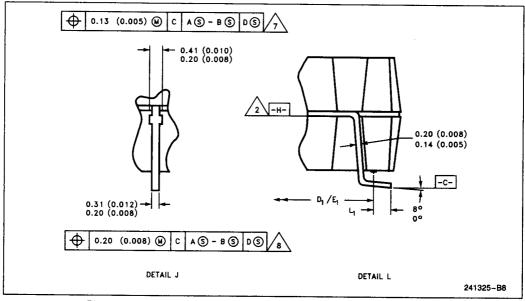

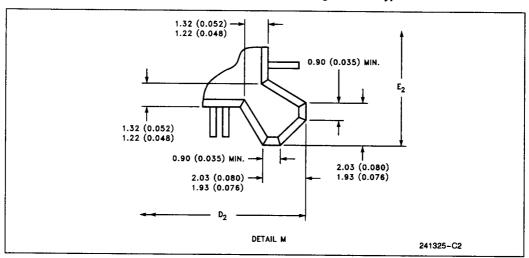

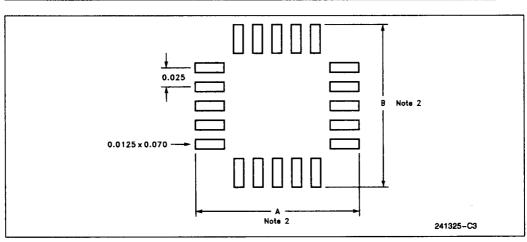

Available in PQFP, LGA and SQFP Packages

241325-C5

# 82360SL I/O SUBSYSTEM COMPLETE ISA PERIPHERAL SUBSYSTEM INTEGRATED SYSTEM POWER MANAGEMENT FULLY-STATIC CHMOS™ V TECHNOLOGY

- Complete ISA System, with Extended Support

- Full ISA Bus Control, Status and Address and Data Interface Logic

- --- Compatible ISA Bus Peripherals:

- Two 8237 Direct Memory Access Controllers

- Two 8254 Programmable Timer

Counters (6 Timer/Counter

Channels)

- Two 8259A Programmable

- Interrupt Controllers (15 Channels)

- --- Enhanced LS612 Page Memory Mapper

- One 146818 Compatible Real Time Clock w/256-byte CMOS RAM

- Two 16450 Compatible Serial Port Controllers

- One 8-Bit Parallel I/O Port with High Speed Protocol

- (Centronics or Bi-Directional)

- Additional System I/O Decoding, Programmable Chip Selects and Support Interfaces:

- -- Full Integrated Drive Electronics (I.D.E.) Hard Disk Interface

- Floppy Disk Controller

- Keyboard Controller Chip Selects and Support Logic

- **■** External Real Time Clock Support

- PS/2 and EISA Control/Status Ports

- Local Memory and ISA-Bus Memory Refresh Control

- New IdeaPort Interface for Hardware Expansion

- Transparent Power Management System Architecture

- Architecture Extension for Truly Compatible Systems

- Transparent to Operating Systems and Applications Programs

- Programmable Hardware Supports

Custom Power-Control Methods

- Integrated Power Management Unit Manages Power-Events Safety

- Selectable 3.3V/5V Operating Voltage

Available in SQFP and PQFP Packages

241325-C6

#### 1.0 INTRODUCTION

This document provides the pinouts, signal descriptions, and D.C./A.C. electrical characteristics of the Intel486 SL microprocessor and 82360SL I/O peripheral device. Consult Intel for the most recent design-in information. For a thorough description of any functional topic, other than the parametric specifications, please refer to the latest Intel486 SL Microprocessor System Design Guide and the Intel486 SL Microprocessor Programmer's Reference Manual.

In recent years, users have shown an increasing tendency to insist on the most powerful processors available, and to quickly upgrade to systems based on those processors. This trend has been accelerated by the advent of 32-bit operating systems, advanced graphical user interfaces (GUIs), and computationally intensive applications (i.e., computeraided design and multimedia), all of which place great demands on system resources. At the same time, users are demanding the ability to take their work home, on the road, and in the field. The Intel486 SL microprocessor will allow users to obtain the benefits of longer battery-life for portable computing without sacrificing the performance they require. This market for portables is expanding at a rapid pace; it is the fastest growing segment of the PC-compatible market.

# 1.1 Challenges Faced by the Portable PC Designer

Designing new products for the fast-paced portable computer market presents a unique set of challenges. System performance is key; GUIs, operating systems and both desktop and pen-based application programs are becoming increasingly complex while users have come to expect workstation-like performance in the palm of their hand. Form factors are shrinking so rapidly that highly integrated system logic is a must. Compatibility with existing machines, operating systems and applications software must also be maintained.

In addition, portable computers are battery-powered so power consumption must be strictly limited whenever possible. This requires the presence of power management circuitry and software that is tightly coupled to both the microprocessor and the remainder of system logic. Implementation of power management in a fashion transparent to the operating system and applications programs is essential.

Furthermore, the pressure to shorten time-to-market cycles is always increasing. The highly competitive nature of this market means that development dollars must be spent wisely. The result is a need for a consistent and flexible architecture across an entire product line. Such an approach ensures that com-

patibility requirements are met and that investments in BIOS and power management firmware are amortized across multiple products.

# 1.2 The Intel486™ SL Microprocessor Superset

Building on the Intel386TM SL microprocessor standard for mobile computers, Intel developed the Intel486 SL microprocessor family to support the next generation of notebook and pen-based computers. The SL SuperSet consists of both the highly integrated CPU and I/O companion chip, the 82360SL. The high performance low voltage, sophisticated power management, and design flexibility makes the Intel486 SL microprocessor SuperSet ideal for ISA-compatible portable system designs. As a member of the Intel486 processor family, it provides 100% binary compatibility with all Intelx86 software.

At the heart of the Intel486 SL CPU is a true 32-bit Intel486 DX microprocessor. The 8 Kbyte on-chip cache, RISC integer core, and full 32-bit data bus give the Intel486 SL CPU twice the performance of the Intel386 SL CPU. The on-chip math coprocessor is an enhanced version of the Intel387<sup>TM</sup> math coprocessor which further increases performance on scientific applications (floating point based).

With a full-featured on-chip memory controller and a 26-bit address bus, it directly supports up to 64 Mbytes of physical memory. The memory controller permits each memory bank to use a different DRAM size (from 256K to 4 Mbytes) and provides automatic refresh capability during suspend mode. It also automatically routes each access cycle to its appropriate destination, which could be the internal cache, ISA bus or Peripheral Interface (PI) bus.

The performance of the Intel486 SL CPU is further enhanced by a high-speed PI expansion bus, a 16-bit bus that supports high-speed graphics displays (increasingly important for ruuning state-of-the-art operating systems and applications software) and solid-state memory devices such as Flash memory disk drives.

Designed from the ground up with power savings in mind, the Intel486 SL CPU contains a fully static processor core operating at 3.3V which significantly reduces full-on power consumption. Its memory bus, PI bus, and ISA bus all feature "flexible voltage" support for either 3.3V or 5V components. Thus, the DRAM subsystem may run at either 3.3V or 5V. The Intel486 SL CPU may be used in conjunction with current 5V peripherals or—as they become available—future 3.3V peripherals. This flexible voltage feature will allow system designers to maintain compatibility with current hardware while paving the way for future designs that are fully low-voltage in design.

intجا.

Equally important is the capability of the processor to manage system power consumption. The Intel486 SL CPU incorporates the same System Management Mode (SMM) found in the previous Intel386 SL CPU. A non-maskable System Management Interrupt (SMI), a corresponding Resume instruction and a new memory space for system management code are the basis of SMM. SMM ensures seamless power control of the processor core, system logic, main memory and one or more peripheral devices from within any application or operating system. Since the SMM operation with the Intel486 SL CPU is fully compatible with existing SL designs, manufacturers' investments in BIOS and power management firmware are preserved and design cycles are shortened.

The 82360SL I/O chip is the companion product to the Intel486 SL CPU. Originally developed as part of the Intel386 SL microprocessor SuperSet, the 82360SL integrates dedicated system logic that provides a complete set of PC-compatible support functions. These functions include two serial ports, one parallel port, two timer/counters, two interrupt controllers, NMI logic and two DMA controllers. A real time clock/calendar, 256 bytes of CMOS RAM and the DMA page registers are also provided.

In addition, peripheral support capability is built-in to the 82360SL. This is comprised of decoder circuitry for Flash memory and for external floppy disk and keyboard controllers. An Intelligent Device Electronics (IDE) fixed disk drive interface is also provided. The 82360SL contains extensive circuitry used to control the power consumption of peripheral devices. This is based on a full complement of hardware timers, event monitors and I/O interfaces. These are controlled by BIOS firmware so that customization for a particular system configuration can be readily achieved.

#### 1.3 Setting the Standard for a New Class of Mobile Computers

With the Intel486 SL CPU, Intel has combined the best features from the Intel486 microprocessor and SL architecture and optimized them for mobile computing. This combination of high-performance, highintegration, and power-management features makes the Intel486 SL microprocessor the ideal microprocessor for next-generation notebook and pen-based computers. Developing these new systems will be greatly facilitated by the Intel SL architecture flexibility and compatibility with future generations.

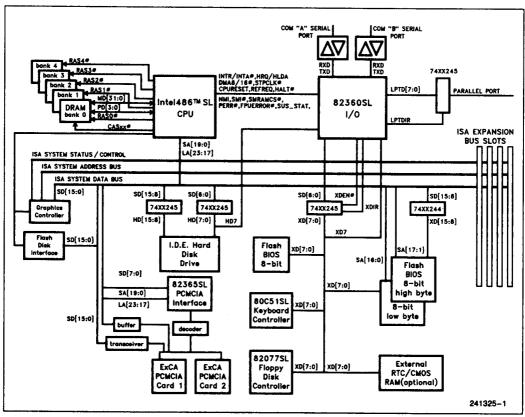

#### 1.4 Overview of System Architecture

The Intel486 SL microprocessor, in combination with the 82360SL I/O, provides the majority of the core logic required to design a high performance ISA-Bus compatible personal computer. The 82360SL I/O is pin-to-pin compatible with its predecessor, the 5V 82360SL I/O. Other system components not integrated in the Intel486 SL CPU or 82360SL I/O include: a graphics controller and display subsystem, a keyboard controller and keyboard/mouse, removable storage (such as floppy disk controller/floppy disk drive or PCMCIA FLASH memory card), fixed storage (such as an I.D.E. hard disk drive), DRAM system memory (such as on-board DRAM or a JEI-DA/JEDEC 88 pin DRAM memory card), and BIOS/ user/graphics ROM, (such as EPROM or FLASH). The Intel 80C51SL Keyboard Controller, 82365SL PCMCIA I/F Controller, 82077SL Floppy Controller and a third party graphics controller may be used to create a full-function transportable personal computer. A typical Intel486 SL microprocessor based system is depicted in Figure 1-1.

Figure 1-1. Intel486™ SL Microprocessor SuperSet System Block Diagram

#### 1.5 Intel486<sup>TM</sup> SL Microprocessor: Central Processing Unit (CPU), Onchip Cache, On-chip Floating Point Unit (FPU) and Memory Controller Subsystem

Intel486TM SL Microprocessor SuperSet

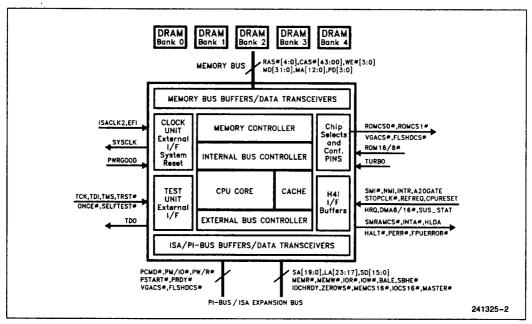

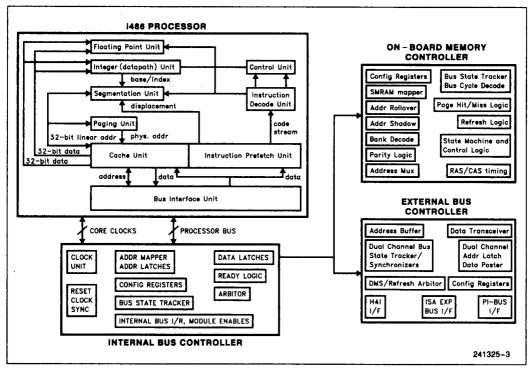

The Intel486 SL CPU is the next generation microprocessor in the Intel SL family. Portable personal computer manufacturers may use the Intel486 SL CPU, in conjunction with the 82360SL I/O, to produce systems of higher performance, higher integration, and lower power consumption. Included in this highly integrated chip are a static Intel486 microprocessor core, an on-chip cache, an on-chip floating point unit, a 32-bit on-chip memory controller and a 16-bit external bus controller. High performance is a direct result of the reduced clocks per instruction associated with the Intel486 CPU. Intel486 SL CPU offers low power consumption by supporting reduced supply voltage operation of the core logic, by instituting a fully static design, and by using the low power Intel CHMOS V process technology. The onboard/local DRAM buffers may be selectively powered to support 3.3V or 5V DRAMs. The powering of ISA bus interface and I/O interface is at 3.3V or 5V. This ensures the usability of the Intel486 SL CPU, the existing ISA bus peripherals, and future 3.3V peripherals. Table 1-1 describes the options available with the Intel486 SL CPU. Figure 1-2 shows the internal modules of the Intel486 SL CPU.

Table 1-1, Intel486™ SL Microprocessor Options

|                    |          |                    | p. 00000                       | Optiono                  |

|--------------------|----------|--------------------|--------------------------------|--------------------------|

| Product            | FPU      | Frequency<br>(MHz) | ISA/PI<br>Interface<br>Voltage | Package                  |

| Intel486 SL<br>CPU | Internal | 25, 33(1)          | 3.3V(1)<br>or 5V               | SQFP(1),<br>PQFP,<br>LGA |

1. Currently, this document does not describe 33 MHz, SQFP and 3.3V interface to ISA/PI bus. For more updated information on the CPU options, please contact your Intel sales office.

The Intel486 SL CPU is a high performance solution that offers fast time-to-market for personal computer manufacturers. It reduces system development time by retaining the same interfaces to the 82360SL I/O, ISA expansion bus, and high speed peripheral interface bus (PI-bus). A system designer may create a personal computer which has all of the same components as the Intel386™ SL CPU system with the exception of the Intel486 SL CPU and the on-board DRAM subsystem. The new printed circuit board assembly could be smaller since the Intel486 SL CPU eliminates the need for external cache data SRAM and external math co-processor. Although the Intel486 SL CPU is not a drop in replacement for the Intel386 SL CPU, 75% of the signals share the same functionality. The Intel486 SL CPU maintains software compatibility with the Intel386 SL CPU System Management Mode (SMM). BIOS and System Setup software may be easily modified to support the new DRAM memory configurations without impacting applications software drivers.

The Intel486 CPU, with on-chip cache, yields an average of 1.8-2.4 clocks per instruction as compared to 12 clocks for the 8086/8088 and 4.5 clocks for the 80286 or 80386 CPUs. In a true zero wait state. uniprocessor environment, the Intel486 SL CPU system performance could be as much as 2.5 times that of an Intel386 CPU. Intel486 SL CPU with FPU provides both integer and floating point performance improvements when compared with the Intel386 and Intel387TM Math Co-processor combination, Figure 1-3 shows the functional modules of the Intel486 SL CPU.

Figure 1-2. Internal Modules of Intel486™ SL Microprocessor

Figure 1-3. Intel486™ SL Microprocessor Internal Functional Block Diagram

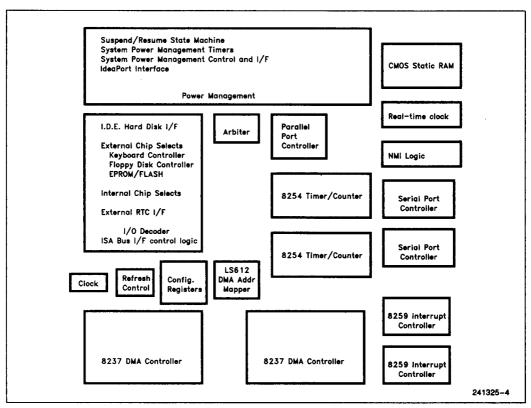

#### 1.6 82360SL I/O: Integrated ISA Peripheral and Power Management Device

The new low-voltage 82360SL Peripheral I/O is pinfor-pin compatible with the existing 5V 82360SL I/O. It can operate both at 5V and 3.3V. It is available both in 208-lead SQFP and 196-lead PQFP. The 82360SL I/O contains dedicated logic to perform a number of CPU, memory, and peripheral support functions. It also contains an extensive set of programmable power management facilities that minimize system power requirements for battery-powered portable computers.

The 82360SL I/O includes a complete set of on-chip peripheral device functions including two 16450 compatible serial ports, one 8-bit Centronics interface or bi-directional parallel port, two 8254 compatible timer counters, two 8259 compatible interrupt controllers, two 8237 compatible DMA controllers. one 74LS612 compatible DMA page register, one 14618 compatible real-time clock/calendar with an additional 128 bytes of battery backed CMOS RAM and an integrated drive electronics (IDE) hard disk interface. The Intel 82360SL I/O also contains highly programmable chip selects and complete peripheral interface logic for direct keyboard and floppy disk controller support. The peripheral registers and functions behave exactly the same as the discrete components commonly found in industry standard personal computers. The peripheral logic is enhanced for static operation by supporting write only registers as read/write.

The processor and the memory support functions contained in the 82360SL I/O eliminate most of the external random-logic "glue" that might otherwise be required. The 82360SL I/O provides internal programmable- frequency clock generators for the ISA backplane and video subsystems. A programmable, low power DRAM refresh timer is also provided to maintain system memory integrity during the power saving Suspend state.

The 82360SL I/O contains a flexible set of hardware functions to support the growing sophistication in power management schemes required by portable systems. Numerous hardware timers, event monitors, and I/O interfaces can programmably monitor and control system activity. Firmware developed by the system designer allocates and directs the hardware to fulfill the unique power management needs of a given system configuration.

All of the standard peripheral registers, clock-generation logic, and power-management facilities have been designed to ensure complete compatibility with the existing operating systems and applications software.

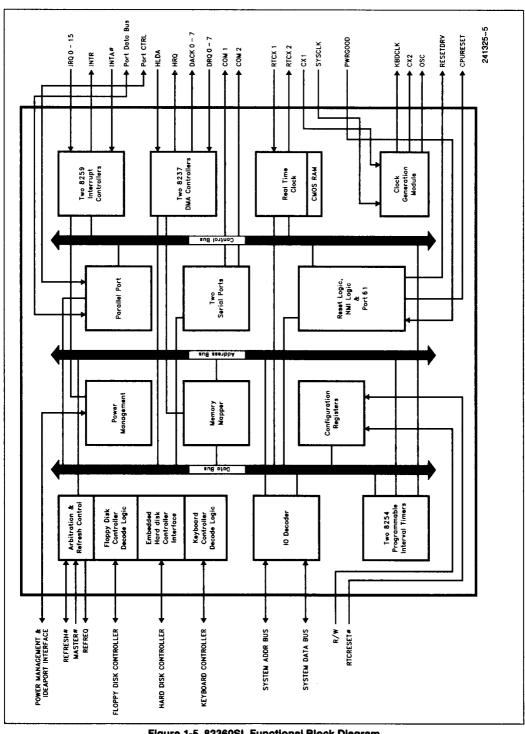

Figures 1-4 and 1-5 show the functional blocks and micro-architecture of the 82360SL I/O.

Figure 1-4. Intel 82360SL iSA Peripheral I/O Internal Functional Modules

Figure 1-5. 82360SL Functional Block Diagram

#### 2.0 Intel486™ SL MICROPROCESSOR SPECIFICATIONS

#### 2.1 Intel486 SL Microprocessor Pin Assignment and Signal Characteristics

Section 2 provides information for the Intel486 SL CPU pin assignments and signal mnemonics. In ad-

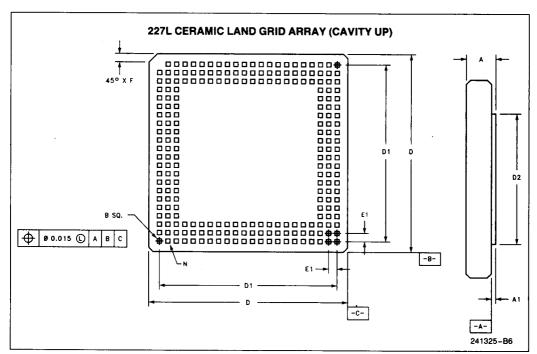

dition to the package pin out diagrams, a table is provided for easy location of signals. The table lists the Intel486 SL CPU package device pinouts in the 196-lead JEDEC Plastic Quad Flat Package (PQFP) and the 227 lead LGA package. The table includes additional information on the signals and the associated pin. A brief explanation of each column is given in Table 2-1.

Table 2-1. Description of the Columns of Table 2-2

|            | Table 2-1. Description of the Columns of Table 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic   | Signal Name Associated with the Package Pinouts and Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PQFP       | 196-lead JEDEC Plastic Quad Flatpack (MM-PQFP), approximately 0.635mm lead spacing (25 mil). The PQFP is a surface mount OEM package used for all production speed grades of the Intel486 SL CPU. There are 171 active signals.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | There are 13 $V_{CC}$ pins and 12 $V_{SS}$ pins available in the 196 PQFP. Currently 4 $V_{CC}$ 's are always connected to 3.3V and power the plane for all internal logic and input buffers, 5 $V_{CC}$ 's are associated with the memory bus which may be connected to either 3.3V or 5V and 4 $V_{CC}$ 's are associated with the ISA bus which are connected to 5.0V. All grounds ( $V_{SS}$ ) are common to a single ground plane.                                                                                                                                                                                                                               |

|            | This column lists the pin number that is associated with the corresponding signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LGA        | This column lists the pin names of the Intel486 SL CPU in a 227-lead LGA package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Туре       | Input—Input pins are unidirectional signals which are driven by external devices or logic into the Intel486 SL CPU buffers. Inputs are selectively biased to either 3.3V or 5.0V when connected to the associated $V_{\rm CC}$ 's for each buffer group.                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | Output—Output pins are unidirectioral signals which are driven out by the Intel486 SL CPU buffers. Outputs are selectively biased to either 3.3V or 5.0V when connected to the associated $V_{\rm CC}$ 's for each buffer group.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | I/O—Input/Output pins are bi-directional signals to/from the Intel486 SL CPU buffers. I/O pins when enabled as outputs are selectively biased to either 3.3V or $5,0V$ when connected to the associated $V_{\rm CC}$ 's for each buffer group.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Term       | Indicates the internal pull-up or pull-down resistor value associated with this signal. Signals which are either pulled-up or pulled-down may be determined by referencing the Stop Clock description. In general open drain signals which are a "wire-OR" on the ISA bus use a "hard pull-up/pull-down" (typically $600\Omega-1000\Omega$ ). The open drain Intel486 SL CPU ISA bus signals include: IOCHRDY, IOCS16#, MASTER#, MEMCS16# and 0WS#. Asynchronous inputs such as NMI, INTR, HRQ have "soft" pulldowns in the range of 20K. The ISA bus Command, Data and Miscellaneous Chip Selects have "soft" pull-ups or pull-downs in the range of 60 K $\Omega$ . |

| 3.3V or 5V | This column specifies whether the named pin is powered by 3.3V or 5V and also the $V_{CC}$ pin number associated with the supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ONCE       | On-Chip Emulation Mode (ONCE). This indicates the signal state of this pin when Intel486 SL CPU ONCE # pin is LOW. Signals when the Intel486 SL CPU is in on-chip emulation mode may be in one of five states:  Tri—Tri-state logic level  Drv—Active and driven, (the signal continues to operate and may change logic states)  En—The input buffer is enabled, allowing signals to be recognized.  Dis—The input buffer is disabled, prohibiting signals from being recognized.  Hold—Held in the last logic state prior to entering ONCE mode.                                                                                                                     |

Table 2-1. Description of the Columns of Table 2-2 (Continued)

| Mnemonic | Signal Name Associated with the Package Pinouts and Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drive    | I/O and output buffers for the memory bus and ISA bus have programmable output strengths. In general a three legged binary configuration is supported by the output buffers which have 1x, 2x and 4x "legs" corresponding to lumped capacitive load of 34 pF, 68 pF and 136 pF. The 7 strengths or loads which are supported by the programmable output buffers include: 34 pF, 68 pF, 102 pF, 136 pF, 170 pF, 204 pF and 238 pF. The V <sub>OH</sub> and V <sub>OL</sub> of 3.3V output and I/O buffers matches the V <sub>OH</sub> and V <sub>OL</sub> of 5.0V buffers. The associated I <sub>OL</sub> (current into an output which will establish a logic high) are specific to the buffer type and programming of the output buffer. The memory bus buffers are controlled by the Memory Controller Unit 32-bit MCBUFF configuration register. The memory bus buffers are divided into the following five groups:  Column Address Strobe for each bank Memory Address for all DRAM banks and Write Enable per Byte Common Write Enable (for all bytes in a DRAM banks) Row Address Strobe for each bank Memory Data and Parity for all DRAM banks The ISA bus buffers are controlled by the External Bus Controller 16-bit EBCBUFF configuration register. The ISA bus buffers are divided into the following six groups:  Lower System Data Byte (SD7:0) Upper System Data Byte (SD15:8) Lower System Addresses (SA16:0) Upper System Addresses (SA19:17 and LA23:17) Memory Command Signals (MEMR #, MEMW #) I/O Command Signals (MEMR #, MEMW #) |

| PWR RST  | Power On-Reset (PWRGOOD De-Asserted with EFI active). This indicates the signal state of this pin when the Intel486 SL CPU is in Global Reset. In general, inputs have the designation TRI for tri-state. Internal logic connected to the input buffers is electrically isolated when the Intel486 SL CPU is in suspend and the input termination (pull-up or pull-down) is disabled. Outputs and I/O buffers may be in one of five states:  Tri—Tri-state logic level  Drv—Active and driven, (the signal continues to operate and may change logic states)  En—The input buffer is enabled, allowing signals to be recognized.  Dis—The input buffer is disabled, prohibiting signals from being recognized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SUSP     | Suspend Mode (SUSP). This indicates the signal state of this pin when Intel486 SL CPU is in Suspend Mode. In general, inputs have the designation TRI for tri-state. Internal logic connected to the input buffers is electrically isolated when the Intel486 SL CPU is in suspend and the input termination (pull-up or pull-down) is disabled. The only inputs which are actively sampled (ACTV) in suspend are: EFI, ISACLK2, CPURESET, SUS_STAT, ONCE#, PWRGOOD and REFREQ. Outputs and I/O buffers may be in one of five states: Tri—Tri-state logic level  Drv—Active and driven, (the signal continues to operate and may change logic states)  En—The input buffer is enabled, allowing signals to be recognized.  Dis—The input buffer is disabled, prohibiting signals from being recognized.  Hold—Held in the last logic state prior to entering Suspend Mode  PU—Pulled up  PD—Pulled down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 2-1. Description of the Columns of Table 2-2 (Continued)

| Mnemonic | Signal Name Associated with the Package Pinouts and Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load     | This column lists the maximum and minimum capacitive loads which the buffer can directly drive in pF for each signal. This is specified for output and input-output pins only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| STOPCLK  | Stop Clock Mode (STOPCLK). This indicates the signal state of this pin when the Intel486 SL CPU is in Stop Clock Mode. During Stop Clock the internal Intel486 SL CPU and FPU clock is stopped. Alternate Master or DMA may continue to operate and the Intel486 SL CPU cache will continue to snoop. The on-board memory controller may also be active to service DRAM accesses by an ISA bus master or DMA device as well as providing refresh. In general, input and output signals on the ISA bus are pulled high or low to their "inactive logic state" and have the designation PU or PD during Stop Clock. Signals in Stop Clock mode may be in one of four states:  PU—Pulled up  PD—Pulled down  Drv—Active and driven, (the signal continues to operate and may change logic states)  En—The input buffer is enabled, allowing signals to be recognized.  Dis—The input buffer is disabled, prohibiting signals from being recognized. |

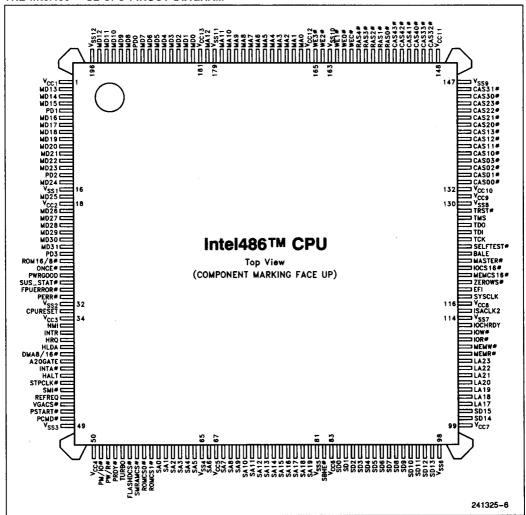

#### THE Intel486TM SL CPU PINOUT DIAGRAM

Intel486<sup>TM</sup> SL Microprocessor SuperSet

Figure 2-1. Top View of the Pinout of the Intel486™ SL Microprocessor in a 196-Lead PQFP Package

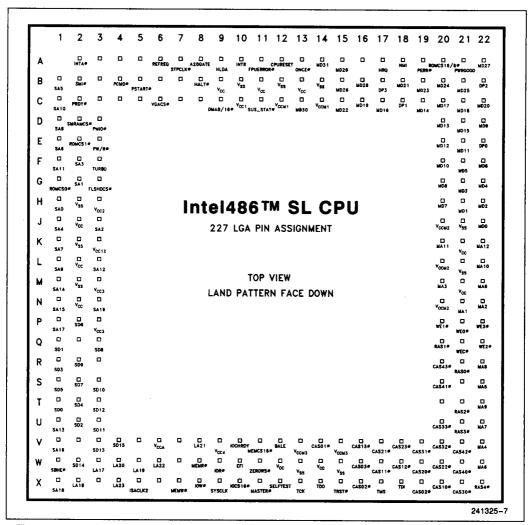

Figure 2-2. Top View of the Pinout of the Intel486™ SL Microprocessor in a 227-Lead LGA Package

Table 2-2. Intel486™ SL Microprocessor Pin Characteristics

| Mnemonic  | PQFP    | LGA | Туре | Term       | Drive <sup>(1)</sup><br>I <sub>OL</sub> /I <sub>OH</sub><br>(Default) | Load<br>Min, Max | PWR<br>RST | Susp <sup>(2)</sup><br>(Default) | STOPCLK | ONCE | 3.3∀ a  | r 5V              |

|-----------|---------|-----|------|------------|-----------------------------------------------------------------------|------------------|------------|----------------------------------|---------|------|---------|-------------------|

| A20GATE   | Pin 40  | 80A | - 1  | 60K        |                                                                       |                  | Dis        | Dis                              | PU      | Dis  | 5V      | VcC3              |

| BALE      | Pin 123 | V12 | 0    | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Hold | 5V      | V <sub>CC8</sub>  |

| CAS00#    | Pin 133 | X16 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Đr                               | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS01#    | Pin 134 | V14 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | D۲۷                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS02#    | Pin 135 | X19 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Dr∨                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS03#    | Pin 136 | W16 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS10#    | Pin 137 | X20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri_ | 3.3V/5V | V <sub>CC10</sub> |

| CAS11#    | Pin 138 | W17 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS12#    | Pin 139 | W18 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS13#    | Pin 140 | V16 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS20#    | Pin 141 | W19 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS21#    | Pin 142 | V17 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS22#    | Pin 143 | W20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS23#    | Pin 144 | V18 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS30#    | Pin 145 | X21 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS31#    | Pin 146 | V19 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS32#    | Pin 149 | V20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS33#    | Pin 150 | U20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS40#    | Pin 151 | W21 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS41#    | Pin 152 | S20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS42#    | Pin 153 | V21 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CAS43#    | Pin 154 | R20 | 0    | Hold       | 17/10                                                                 | 15, 72           | Tri        | Drv                              | Drv     | Tri  | 3.3V/5V | V <sub>CC10</sub> |

| CPURESET  | Pin 33  | A12 | ı    | 20K        |                                                                       |                  | En         | En                               | PD      | Dis  | 5V      | V <sub>CC3</sub>  |

| DMA8/16#  | Pin 39  | C09 | 1    | 60K        |                                                                       |                  | Dis        | Dis                              | PU      | Dis  | 5V      | V <sub>CC3</sub>  |

| EFI       | Pin 118 | W10 | ı    |            |                                                                       |                  | En         | Dis                              | En      | Tri  | 5V      | V <sub>CC8</sub>  |

| FLSHDCS#  | Pin 55  | G03 | 0    | Hold       | 7/4                                                                   | 10, 50           | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC3</sub>  |

| FPUERROR# | Pin 30  | A11 | 0    |            | 7/4                                                                   |                  | Tri        | Tri                              | ₽rv     | Tri  | 5V      | V <sub>CC3</sub>  |

| HALT#     | Pin 42  | B08 | 0    | Hold       | 13/8                                                                  | 10, 50           | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC3</sub>  |

| HLDA      | Pin 38  | A09 | 0    | Hold       | 7/4                                                                   | 10, 50           | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC3</sub>  |

| HRQ       | Pin 37  | All | ı    | 20K        |                                                                       |                  | Dis        | Dis                              | PD      | Dis  | 5V      | V <sub>CC3</sub>  |

| INTA#     | Pin 41  | A02 | 0    | Hold       | 12/6                                                                  | 10, 50           | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC3</sub>  |

| INTR      | Pin 36  | A10 | 1    | 20K        |                                                                       |                  | Dis        | Dis                              | PD      | Dis  | 5V      | VCC3              |

| IOCHRDY   | Pin 113 | V10 | 1/0  | 1K         | 7/4                                                                   | 10, 160          | Tri        | Tri                              | . PU    | Tri  | 5V      | V <sub>CC8</sub>  |

| IOCS16#   | Pin 121 | X10 | 1/0  | 1K         |                                                                       | 10, 160          | Dis        | Dis                              | PU      | Tri  | 5V      | V <sub>CC8</sub>  |

| IOR#      | Pin 111 | W09 | 1/0  | 60K        | 7/4                                                                   | 10, 160          | Tri        | PU                               | PU      | Tri  | 5V      | V <sub>CC8</sub>  |

| IOW#      | Pin 112 | X08 | 1/0  | 60K        | 7/4                                                                   | 10, 160          | Tri        | PU                               | PU      | Tri  | 5V      | V <sub>CC8</sub>  |

| ISACLK2   | Pin 115 | X05 | ı    | ļ <u>.</u> |                                                                       | ļ                | En         | Dis                              | En      | Tri  | 5V      | V <sub>CC8</sub>  |

| LA17      | Pin 102 | W03 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC6</sub>  |

| LA18      | Pin 103 | X02 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC8</sub>  |

| LA19      | Pin 104 | W05 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC6</sub>  |

| LA20      | Pin 105 | W04 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CO8</sub>  |

| LA21      | Pin 106 | V08 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC6</sub>  |

| LA22      | Pin 107 | W06 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC6</sub>  |

| LA23      | Pin 108 | X04 | 1/0  | Hold       | 7/4                                                                   | 10, 160          | Tri        | Tri                              | Drv     | Tri  | 5V      | V <sub>CC6</sub>  |

<sup>1.</sup> Drive currents are for default buffer strengths only. Refer to Intel486 SL Microprocessor SuperSet Programmer's Reference Manual for details.

<sup>2.</sup> The states of ISA-bus and PI-bus pins listed in this column are programmable. Refer to Intel486 SL Microprocessor SuperSet Programmer's Reference Manual for details.

Table 2-2. Intel486™ SL Microprocessor Pin Characteristics (Continued)

|          |         |     | <del></del> | т    | 1                                                                     |                  |            | T                                | istics (CO |      | <u>,</u> |                                        |

|----------|---------|-----|-------------|------|-----------------------------------------------------------------------|------------------|------------|----------------------------------|------------|------|----------|----------------------------------------|

| Mnemonic | PQFP    | LGA | Туре        | Term | Drive <sup>(1)</sup><br>I <sub>OL</sub> /I <sub>OH</sub><br>(Default) | Load<br>Min, Max | PWR<br>RST | Susp <sup>(2)</sup><br>(Default) | STOPCLK    | ONCE | 3.3V d   | or 5V                                  |

| MAO      | Pin 167 | W22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA1      | Pin 168 | N21 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA2      | Pin 169 | N22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| МАЗ      | Pin 170 | M20 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA4      | Pin 171 | V22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA5      | Pin 172 | S22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA6      | Pin 173 | M22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA7      | Pin 174 | U22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA8      | Pin 175 | R22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA9      | Pin 176 | T22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Dry        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA10     | Pin 177 | L22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA11     | Pin 178 | K20 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MA12     | Pin 180 | K22 | 0           | Hold | 12/6                                                                  | 32, 240          | Tri        | Drv                              | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MASTER#  | Pin 122 | X11 | 1           | 1K   | -                                                                     |                  | Dis        | Dis                              | PU         | Tri  | 5V       | V <sub>CC8</sub>                       |

| MD0      | Pin 182 | J22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD1      | Pin 183 | H21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD2      | Pin 184 | H22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD3      | Pin 185 | G21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD4      | Pin 186 | G22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD5      | Pin 187 | F21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  |                                        |

| MD6      | Pin 188 | F22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD7      | Pin 189 | H20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD8      | Pin 191 | G20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD9      | Pin 192 | D22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub><br>V <sub>CC13</sub> |

| MD10     | Pin 193 | F20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD11     | Pin 194 | E21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD12     | Pin 195 | E20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC13</sub>                      |

| MD13     | Pin 2   | D20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  |                                        |

| MD14     | Pin 3   | C19 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD15     | Pin 4   | D21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  |                                        |

| MD16     | Pin 6   | C17 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD17     | Pin 7   | C20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  |                                        |

| MD18     | Pin 8   | C21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD19     | Pin 9   | C16 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD20     | Pin 10  | C22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  |                                        |

| MD21     | Pin 11  | B18 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD22     | Pin 12  | C15 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD23     | Pin 13  | B19 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD24     | Pin 15  | B20 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD25     | Pin 17  | B21 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD26     | Pin 19  | B15 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  |          | V <sub>CC2</sub>                       |

| MD27     | Pin 20  | A22 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD28     | Pin 21  | B16 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             |            |      | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD29     | Pin 22  | A15 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| MD30     | Pin 23  | C13 | 1/0         | Hold | 12/6                                                                  | 8, 32            | Tri        | Hold                             | Drv<br>Drv | Tri  | 3.3V/5V  | VCC2                                   |

| MD31     | Pin 24  | A14 | 1/0         | Hold | 12/6                                                                  |                  | Tri        |                                  |            | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

| IMD31    | F111 24 | A14 | 1/0         | noia | 12/6                                                                  | 8, 32            | ın         | Hold                             | Drv        | Tri  | 3.3V/5V  | V <sub>CC2</sub>                       |

<sup>1.</sup> Drive currents are for default buffer strengths only. Refer to Intel486 SL Microprocessor SuperSet Programmer's Reference Manual for details.

<sup>2.</sup> The states of ISA-bus and PI-bus pins listed in this column are programmable. Refer to intel486 SL Microprocessor SuperSet Programmer's Reference Manual for details.

Table 2-2. Intel486™ SL Microprocessor Pin Characteristics (Continued)

|            |         |     |      |      | Drive(1)                                      |                  |            | l'''                             | 000 6001 | r    | -       |                   |

|------------|---------|-----|------|------|-----------------------------------------------|------------------|------------|----------------------------------|----------|------|---------|-------------------|

| Mnemonic   | PQFP    | LGA | Туре | Term | l <sub>OL</sub> /l <sub>OH</sub><br>(Default) | Load<br>Min, Max | PWR<br>RST | Susp <sup>(2)</sup><br>(Default) | STOPCLK  | ONCE | 3.3V o  | r 5V              |

| MEMCS16#   | Pin 120 | V11 | 1/0  | 1K   |                                               | 10, 160          | Dis        | Dis                              | ₽U       | Tri  | 5V      | Vccs              |

| MEMR#      | Pin 109 | W08 | 1/0  | 60K  | 7/4                                           | 10, 160          | Tri        | PU                               | PU       | Tri  | 5V      | V <sub>CC8</sub>  |

| MEMW#      | Pin 110 | X07 | 1/0  | 60K  | 7/4                                           | 10, 160          | Tri        | PU                               | PU       | Tri  | 5V      | V <sub>CC8</sub>  |

| NMI        | Pin 35  | A18 | 1    | 20K  |                                               |                  | Dis        | Dis                              | PD       | Dis  | 5V      | V <sub>CC3</sub>  |

| ONCE#      | Pin 27  | A13 | - 1  | 60K  |                                               |                  | En         | En                               | PU       | En   | 5V      | V <sub>CC3</sub>  |

| PCMD#      | Pin 48  | B04 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | PU                               | Drv      | Tri  | 5V      | V <sub>СС3</sub>  |

| PD0        | Pin 190 | E22 | 1/0  | Hold | 12/6                                          |                  | Tri        | Hold                             | Drv      | Tri  | 3.3V/5V | V <sub>CC13</sub> |

| PD1        | Pin 5   | C18 | 1/0  | Hold | 12/6                                          |                  | Tri        | Hold                             | Drv      | Tri  | 3.3V/5V | V <sub>CC13</sub> |

| PD2        | Pin 14  | B22 | 1/0  | Hold | 12/6                                          |                  | Tri        | Hold                             | Drv      | Tri  | 3.3V/5V | V <sub>CC13</sub> |

| PD3        | Pin 25  | B17 | 1/0  | Hold | 12/6                                          |                  | Tri        | Hold                             | Drv      | Tri  | 3.3V/5V | V <sub>CC13</sub> |

| PERR#      | Pin 31  | A19 | 0    | Hold |                                               | 8, 32            | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| PM/IO#     | Pin 51  | D03 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | PU                               | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| PRDY#      | Pin 53  | C03 | . 1  | 60K  |                                               |                  | Dis        | Dis                              | PU       | Dis  | 5V      | Vccs              |

| PSTART#    | Pin 47  | B05 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | PU                               | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| PW/R#      | Pin 52  | E03 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | PU                               | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| PWRGOOD    | Pin 28  | A21 | ı    |      |                                               |                  | En         | En                               | En       | Dis  | 5V      | V <sub>CC3</sub>  |

| RAS0#      | Pin 155 | R21 | 0    | Hold | 17/10                                         | 32, 136          | Tri        | Drv                              | Drv      | Tri  | 3.3V/5V | V <sub>CC12</sub> |

| RAS1#      | Pin 156 | Q20 | 0    | Hold | 17/10                                         | 32, 136          | Tri        | Drv                              | Drv      | Tri  | 3.3V/5V | V <sub>CC12</sub> |

| RAS2#      | Pin 157 | T21 | 0    | Hold | 17/10                                         | 32, 136          | Tri        | Drv                              | Drv      | Tri  | 3.3V/5V | V <sub>CC12</sub> |

| RAS3#      | Pin 158 | Ų21 | 0    | Hold | 17/10                                         | 32, 136          | Tri        | Drv                              | Drv      | Tri  | 3.3V/5V | V <sub>CC12</sub> |

| RAS4#      | Pin 159 | X22 | 0    | Hold | 17/10                                         | 32, 136          | Tri        | Drv                              | Drv      | Tri  | 3.3V/5V | V <sub>CC12</sub> |

| REFREQ     | Pin 45  | A06 | ı    | Hold |                                               |                  | Dis        | En                               | En       | Dis  | 5V      | Vccз              |

| ROMCS0#    | Pin 57  | G01 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| ROMCS1#    | Pin 58  | E02 | 0    | Hold | 7/4                                           | 10, 50           | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC3</sub>  |

| ROMCS16/8# | Pin 26  | A20 | ı    | 60K  |                                               |                  | Dis        | Dis                              | PU       | Dis  | 5V      | Vccs              |

| SA0        | Pin 59  | H01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA1        | Pin 60  | G02 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA2        | Pin 61  | J03 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA3        | Pin 62  | F02 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA4        | Pin 63  | J01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA5        | Pin 64  | B01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA6        | Pin 66  | E01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA7        | Pin 68  | K01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA8        | Pin 69  | D01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

| SA9        | Pin 70  | L01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |

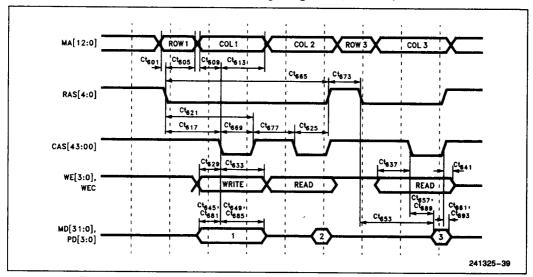

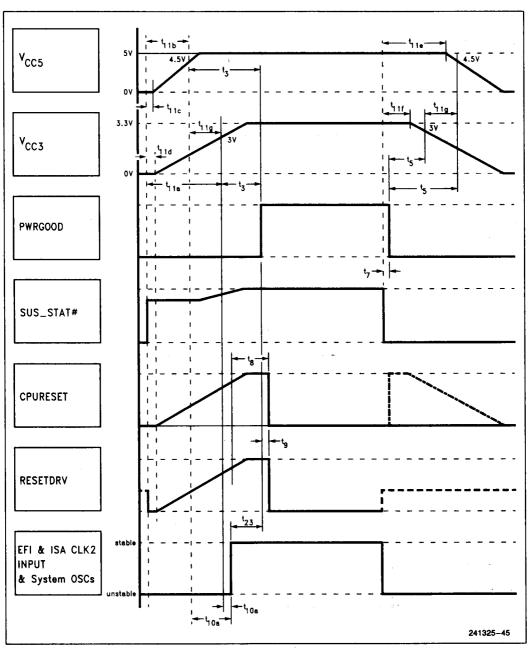

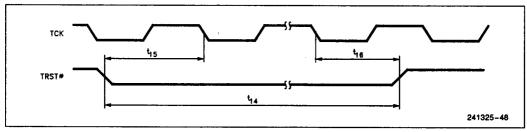

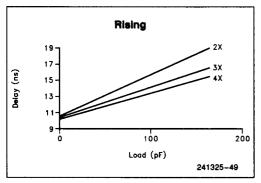

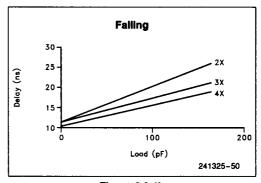

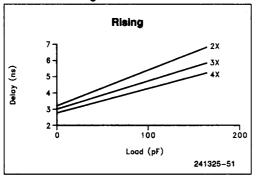

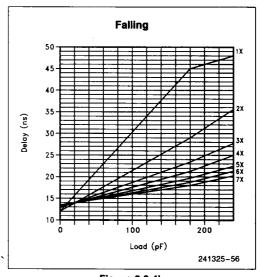

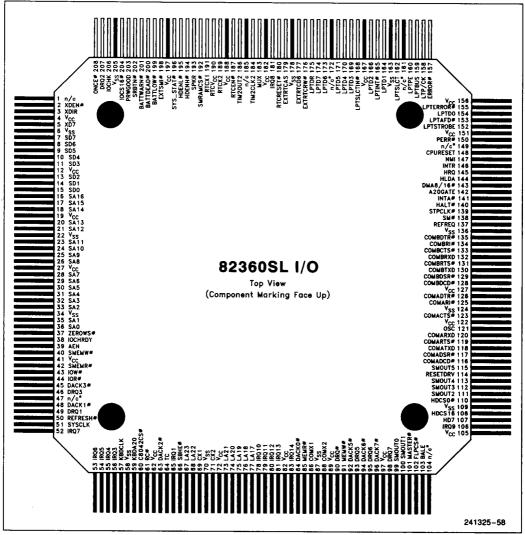

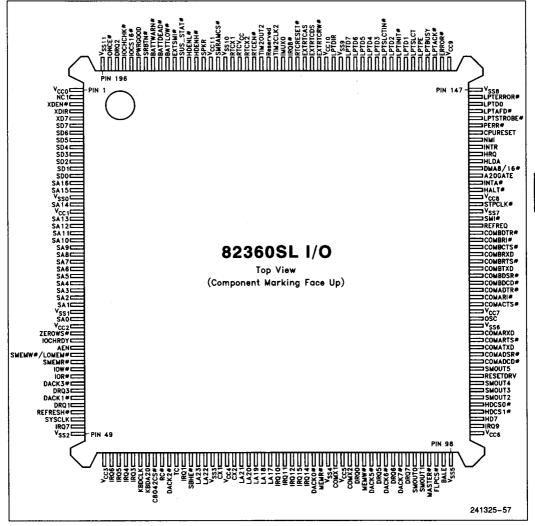

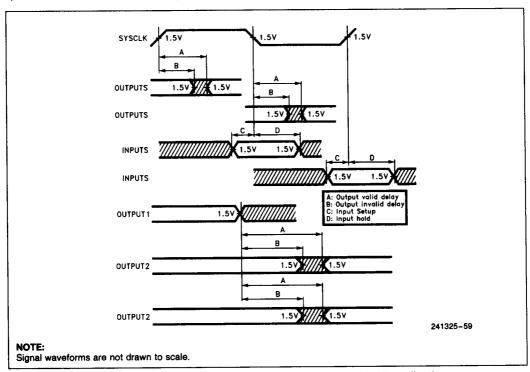

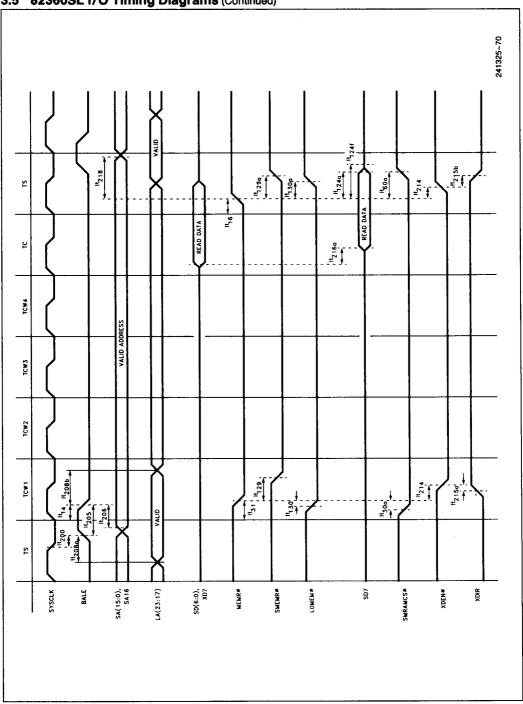

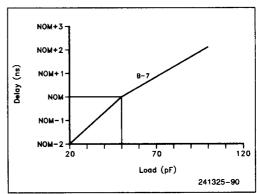

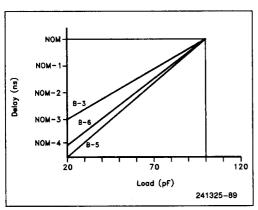

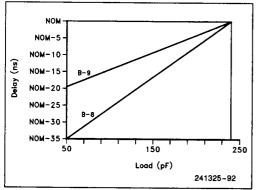

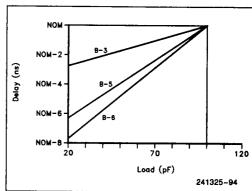

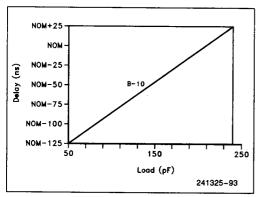

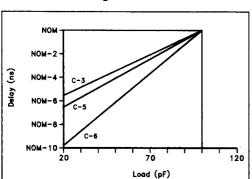

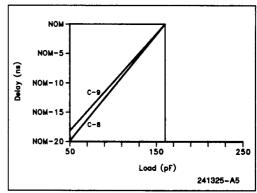

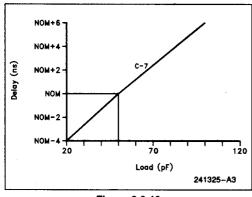

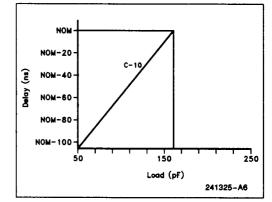

| SA10       | Pin 71  | C01 | 1/0  | Hold | 7/4                                           | 10, 160          | Tri        | Tri                              | Drv      | Tri  | 5V      | V <sub>CC5</sub>  |