### Description

The  $\mu$ PD70136 (V33  $^{\rm m}$ ) is a 16-bit, high-speed CMOS microprocessor that is object and source code compatible with the  $\mu$ PD70116 (V30  $^{\rm m}$ ). Performance is four times that of the 10-MHz V30 due to a number of architectural features, such as hard-wired data path control and dedicated high-speed logic. The address space is expanded to 16M bytes using an internal address translation table.

The powerful instruction set includes bit processing, bit-field insertion and extraction, and BCD string arithmetic. Using a modified Booth's algorithm, the 16-MHz device can execute a 16-bit multiply in 750 ns.

The  $\mu$ PD70136 has separate 16-bit data and 24-bit address buses. Bus control is synchronous. The nominal bus cycle is two clock periods. Dynamic bus sizing is supported for devices that require an 8-bit data path. This allows the  $\mu$ PD70136 to be used in either 16- or 8-bit systems.

An undefined instruction trap allows instructions that are not part of the V-Series instruction set (such as commands for proprietary MMUs) to be emulated. The  $\mu$ PD72291, a high-speed CMOS floating-point coprocessor capable of 530K floating-point operations per second at 16 MHz. is offered.

#### **Features**

- 125-ns minimum instruction execution time at 16 MHz

- □ Expanded address space

- 24-bit addressing to 16M bytes

- LIM 4.0 compatible

- No microcode; better performance with hard-wired data path control

- Dynamic bus sizing for both memory and I/O

- Fully μPD70116 software compatible

- Undefined instruction trap

V30 is a registered trademark of NEC Corporation V20, V33, V40, and V50 are trademarks of NEC Corporation

- High-speed multiplication: 16-bit multiply in 12 clocks (0.75 μs at 16 MHz)

- High-speed division: 16-bit divide in 19 clocks (1.19 μs at 16 MHz)

- μPD72291 floating-point coprocessor executes 530K floating-point operations per second

- BCD string arithmetic instructions

- CMOS with low-power standby mode

- 12.5-MHz or 16-MHz clock

- Single power supply

## **Ordering Information**

| Part Number  | Clock (MHz) | Packag <del>e</del> |

|--------------|-------------|---------------------|

| μPD70136R-12 | 12.5        | 68-pin ceramic PGA  |

| R-16         | 16          | •                   |

| L-12         | 12.5        | 68-pin PLCC         |

| L-16         | 16          | -                   |

| GJ-12        | 12.5        | 74-pin plastic QFP  |

| GJ-16        | 16          | -                   |

## **Pin Configurations**

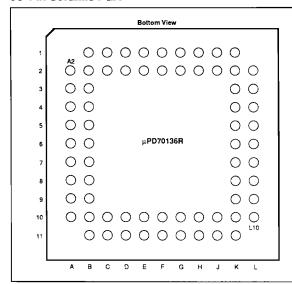

#### 68-Pin Ceramic PGA

| Pin       | Symbol          | Pin | Symbol          | Pin | Symbol         | Pin | Symbol |

|-----------|-----------------|-----|-----------------|-----|----------------|-----|--------|

| A2        | AEX             | B9  | CLK             | F10 | VDD            | K4  | A 12   |

| A3        | HLDAK           | B10 | D <sub>14</sub> | F11 | GND            | K5  | A 14   |

| A4        | READY           | B11 | D <sub>12</sub> | G1  | Ao             | K6  | GND    |

| A5        | CPREQ           | C1  | UBE             | G2  | A1             | K7  | A 16   |

| A6        | V <sub>DD</sub> | C2  | BUSST1          | G10 | D <sub>5</sub> | К8  | D 18   |

| <b>A7</b> | CPBUSY          | C10 | D <sub>11</sub> | G11 | D4             | К9  | A 20   |

| 8A        | INT             | C11 | D <sub>10</sub> | H1  | A2             | K10 | A 23   |

| A9        | D <sub>15</sub> | D1  | BUSST0          | H2  | A3             | K11 | A 22   |

| A10       | D <sub>13</sub> | D2  | R/W             | H10 | D3             | L2  | A7     |

| В1        | BUSLOCK         | D10 | Dg              | H11 | D <sub>2</sub> | L3  | A 9    |

| B2        | BCYST           | D11 | D <sub>8</sub>  | J1  | A4             | L4  | A 11   |

| В3        | BS8/BS16        | E1  | M/10            | J2  | A5             | L5  | A 13   |

| В4        | HLDRQ           | E2  | DSTB            | J10 | D <sub>1</sub> | L6  | V DD   |

| B5        | RESET           | E10 | D <sub>7</sub>  | J11 | Do             | L7  | A 15   |

| В6        | GND             | E11 | D <sub>6</sub>  | K1  | A6             | L8  | A 17   |

| 87        | CPERR           | F1  | GND             | K2  | A8             | L9  | A 19   |

| B8        | NMI             | F2  | VDD             | КЗ  | A 10           | L10 | A 21   |

49NR-339B

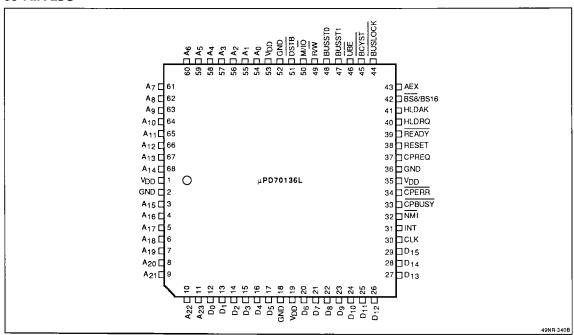

#### 68-Pin PLCC

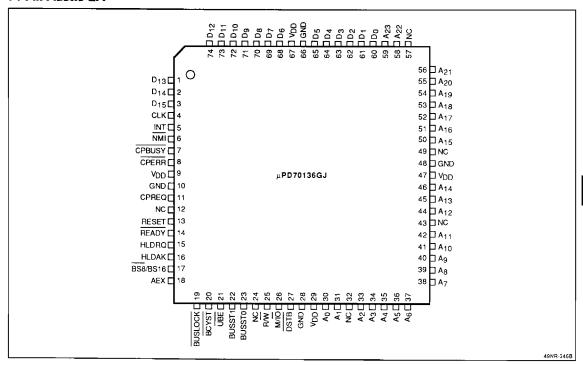

### 74-Pin Plastic QFP

## Pin Identification

| Symbol                          | 1/0     | Function                   |

|---------------------------------|---------|----------------------------|

| A <sub>0</sub> -A <sub>23</sub> | 3-state | Address bus                |

| D <sub>0</sub> -D <sub>15</sub> | 3-state | Data bus                   |

| UBE                             | 3-state | Upper byte enable          |

| R/W                             | 3-state | Read/write                 |

| w/i0                            | 3-state | Memory I/O                 |

| BUSSTO,<br>BUSST1               | 3-state | Bus status                 |

| SCYST                           | 3-state | Bus cycle start strobe     |

| STB                             | 3-state | Data strobe                |

| BUSLOCK                         | Out     | Bus lock                   |

| READY                           | In      | Ready                      |

| 3S8/BS16                        | In      | Dynamic bus sizing control |

| EX                              | Out     | Address expansion flag     |

| HLDRQ                           | in      | Bus hold request           |

| Symbol          | 1/0 | Function                               |

|-----------------|-----|----------------------------------------|

| HLDAK           | Out | Bus hold acknowledge                   |

| INT             | ln  | Maskable interrupt                     |

| NMI             | ln  | Nonmaskable interrupt                  |

| CPBUSY          | In  | Coprocessor busy                       |

| CPERR           | In  | Coprocessor error                      |

| CPREQ           | In  | Coprocessor request                    |

| RESET           | In  | Reset                                  |

| CLK             | In  | Clock                                  |

| V <sub>DD</sub> |     | +5-volt power supply                   |

| GND             |     | Ground                                 |

| IC              | _   | Internal connection; connect to ground |

| NC              | _   | No connection                          |

Table 1. Output Pin States

|          | States                                  |                                                                                                                               |

|----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Hold     | Standby                                 | Reset                                                                                                                         |

| Hi-z     | L                                       | Hi-z                                                                                                                          |

| Hi-z     | (Note 2)                                | Hi-z                                                                                                                          |

| Hi-z     | Н                                       | Hi-z                                                                                                                          |

| Hi-z     | L                                       | Hi-z                                                                                                                          |

| Hi-z     | L                                       | Hi-z                                                                                                                          |

| Hi-z     | Н                                       | Hi-z                                                                                                                          |

| Hi-z     | (Note 3)                                | Hi-z                                                                                                                          |

| Hi-z     | Н                                       | Hi-z                                                                                                                          |

| (Note 4) | (Note 4)                                | Н                                                                                                                             |

| (Note 5) | (Note 5)                                | L                                                                                                                             |

| Н        | L                                       | L                                                                                                                             |

|          | Hi-z Hi-z Hi-z Hi-z Hi-z Hi-z Hi-z Hi-z | Hold Standby Hi-z L Hi-z (Note 2) Hi-z H Hi-z L Hi-z L Hi-z L Hi-z L Hi-z L Hi-z H (Note 3) Hi-z H (Note 4) (Note 4) (Note 5) |

#### Notes:

- (1) Latched internally.

- (2) Undefined during first two clock periods of the halt acknowledge cycle; three-state thereafter.

- (3) Low during first clock period of the halt acknowledge cycle; high thereafter.

- (4) Low if BUSLOCK prefix is used for halt instruction; high otherwise

- (5) Low if in extended addressing mode; high otherwise.

#### PIN FUNCTIONS

### CLK (Clock)

CLK is the main clock. All timing is relative to this input. Each bus state is one CLK period wide. Instruction clock counts refer to this CLK input.

## A<sub>0</sub>-A<sub>23</sub> (Address Bus)

A<sub>0</sub>-A<sub>23</sub> form the 24-bit physical address bus. It is used to access both the 16M-byte expanded and 1M-byte normal memory spaces and the 64K-byte I/O space. These three-state outputs become valid during T1 of all bus cycles and remain valid until after the bus cycle is completed. During HLDAK and when RESET is active, these outputs are not driven.

### D<sub>0</sub>-D<sub>15</sub> (Data Bus)

$D_0$ - $D_{15}$  form the 16-bit data bus, which is used to transfer 16- and 8-bit data between the  $\mu$ PD70136 and the external system. To accommodate 8-bit devices, dynamic bus

sizing can be selected so that only the lower 8 bits,  $D_0$ - $D_7$ , are used. During CPU read cycles, the value on the data bus is latched by the CPU on the trailing edge of T2 or the last TW state. During CPU write cycles,  $D_0$ - $D_{15}$  become valid after the rising edge of T1 and remain valid until after the rising edge of the clock cycle following T2 or the last TW state. During HLDAK and when RESET is asserted,  $D_0$ - $D_{15}$  are not driven.

## **UBE** (Upper Byte Enable)

UBE indicates that the upper 8 bits of the data bus will be used in the current CPU bus cycle. This signal is used in conjunction with A<sub>0</sub> as shown in table 2.

Table 2. Bus Operation vs UBE and Ao

| Bus Operation             | UBE | A <sub>0</sub> | Number of<br>Bus Cycles |

|---------------------------|-----|----------------|-------------------------|

| Word at even address,     | 0   | 0 (Note 1)     | 2                       |

| $\overline{BS}8/BS16 = 0$ | 1   | 1 (Note 3)     | ='                      |

| Word at odd address       | 0   | 1 (Note 1)     | 2                       |

|                           | 1   | 0 (Note 2)     | ='                      |

| Byte at even address      | 1   | 0              | 1                       |

| Byte at odd address       | 0   | 1              | 1                       |

#### Notes:

- (1) First bus cycle

- (2) Second bus cycle

- (3) Second cycle for bus sizing

$\overline{\text{UBE}}$  has the same timing as A<sub>0</sub>-A<sub>23</sub> and is not driven during HLDAK or while RESET is asserted.

## R/W (Read/Write)

$R/\overline{W}$  indicates whether the current bus cycle will be a read or a write. If  $R/\overline{W}$  is high, then the cycle will be a read; if low, a write cycle.  $R/\overline{W}$  has the same timing as  $A_0$ - $A_{23}$  and is not driven during HLDAK or while RESET is asserted.

## M/IO (Memory/IO)

M/IO indicates whether the current bus cycle will be an access to the memory or I/O space. If  $M/\overline{IO}$  is high, access will be to memory; if low, to the I/O space. M/IO is used with BUSST0 and BUSST1 to identify the cycle type.  $M/\overline{IO}$  has the same timing as  $A_0$ - $A_{23}$  and is not driven during HLDAK or while RESET is asserted.

## BUSST0-BUSST1 (Bus Cycle Status)

BUSST0 and BUSST1, in conjunction with  $M/\overline{10}$  and  $R/\overline{W}$ , identify the current cycle type as shown in table 3.

Table 3. Bus Cycle Types

|          |   | Status |        |                       |  |  |

|----------|---|--------|--------|-----------------------|--|--|

| M/IO R/W |   | BUSST1 | BUSSTO | Type of Bus Cycle     |  |  |

| 0        | 1 | 0      | 0      | Interrupt acknowledge |  |  |

| 0        | 1 | 0      | 1      | I/O read              |  |  |

| 0        | 0 | 0      | 1      | I/O write             |  |  |

| 0        | 1 | 1      | 0      | Coprocessor read      |  |  |

| 0        | 0 | 1      | 0      | Coprocessor write     |  |  |

| 0        | 0 | 1      | 1      | HALT acknowledge      |  |  |

| 1        | 1 | 0      | 0      | Instruction fetch     |  |  |

| 1        | 1 | 0      | 1      | Memory read           |  |  |

| 1        | 0 | 0      | 1      | Memory write          |  |  |

| 1        | 1 | 1      | 0      | CP data read          |  |  |

| 1        | 0 | 1      | 0      | CP data write         |  |  |

Note: All bus status signals change after the start of the T1 state.

The 11 cycle types are described in detail in the bus cycles section. The remaining five combinations of these inputs are reserved for future use.

BUSST0-BUSST1 have the same timing as the address bus,  $A_0$ - $A_{23}$ , and are not driven during HLDAK or while RESET is asserted.

## **BCYST** (Bus Cycle Start)

BCYST indicates the start of a bus cycle. It is asserted low during T1 of every bus cycle, and only for the first clock period of each bus cycle. BCYST is not driven during HLDAK or while RESET is asserted.

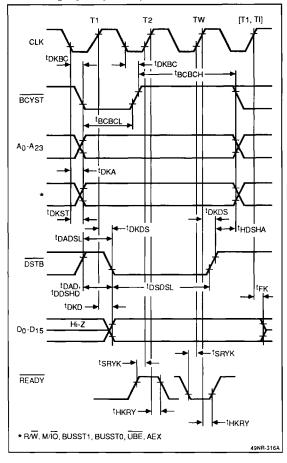

## DSTB (Data Strobe)

$\overline{\text{DSTB}}$  indicates the status of the data on D<sub>0</sub>-D<sub>15</sub>. When asserted low during a write cycle, the  $\mu\text{PD70136}$  drives the write data on D<sub>0</sub>-D<sub>15</sub>. When the CPU asserts this output during a read cycle, external logic should drive the read data onto D<sub>0</sub>-D<sub>15</sub>.

DSTB is asserted following the rising edge (middle) of T1, and stays asserted through T2 and any TW (wait) state that may be inserted. During write cycles, DSTB will be deasserted after the rising edge of either T2 or the last wait state. During read cycles, DSTB is deasserted after the trailing edge of T2 or the last wait state. DSTB is not driven during HLDAK, HALT acknowledge cycles, or while RESET is asserted.

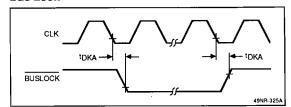

## **BUSLOCK** (Bus Lock)

BUSLOCK should be used by external logic to exclude any other bus master (e.g., a DMA controller) from using a shared resource that the μPD70136 currently is using. When BUSLOCK is asserted high, HLDRQ will be ignored.

$\overline{\text{BUSLOCK}}$  is asserted when the  $\overline{\text{BUSLOCK}}$  prefix is executed or when the  $\mu\text{PD70136}$  is performing a bus operation that must not be interfered with, such as an interrupt acknowledge cycle.  $\overline{\text{BUSLOCK}}$  has the same timing as the address bus  $A_0\text{-}A_{23}$  and is driven high during HLDAK and RESET.

## **READY** (System Ready)

$\overline{\text{READY}}$  is asserted low when the external system is ready for the current bus cycle to terminate. While  $\overline{\text{READY}}$  is not asserted, the  $\mu\text{PD70136}$  will add TW (wait) states to the current bus cycle. The bus state in which  $\overline{\text{READY}}$  is sampled low will be the last state of the cycle.

READY is used during CPU read cycles to give slow devices time to drive the D<sub>0</sub>-D<sub>7</sub> inputs, and during write cycles to give slow devices enough time to finish the write operation.

READY is sampled on the rising (middle) edge of T2 and all TW states. READY is ignored during the HLDAK state. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

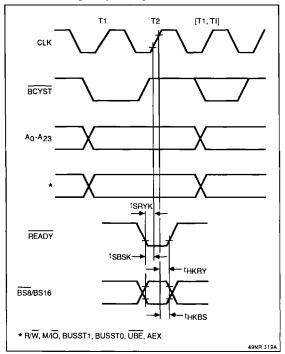

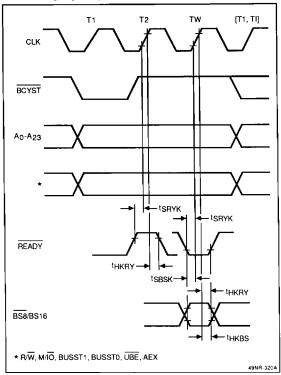

## BS8/BS16 (8-Bit Bus Size/16-Bit Bus Size)

BS8/BS16 is driven low by external logic when the  $\mu$ PD70136 addresses a device with an 8-bit data path. If the  $\mu$ PD70136 operand is 16 bits wide and BS8/BS16 is low, then the  $\mu$ PD70136 will perform two 8-bit bus cycles. The current bus cycle will handle the low byte on D<sub>0</sub>-D<sub>7</sub>, and the next bus cycle will handle the upper byte also on D<sub>0</sub>-D<sub>7</sub>. This input is ignored during HLDAK, interrupt acknowledge, and coprocessor cycles.

BS8/BS16 is sampled on the rising (middle) edge of T2 or the last TW state, coincident with READY. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

#### AEX (Address Expansion)

AEX is asserted when the expanded addressing mode is enabled. When AEX is high, the memory address space is 16M bytes (24-bit address), and when low, 1M bytes (20-bit address).

## **HLDRQ** (Hold Request)

HLDRQ is asserted high by external logic when an external bus master (e.g., a DMA controller) wants to take over the  $\mu$ PD70136 bus. When HLDRQ is detected high, the  $\mu$ PD70136 will release the bus after the current bus operation is completed. Note that this is not necessarily the current bus cycle. The  $\mu$ PD70136 releases its bus by floating the address, data, and control buses. See table 1.

HLDRQ is sampled on the rising edge of each clock. It will be ignored while BUSLOCK is asserted. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

## **HLDAK (Hold Acknowledge)**

HLDAK is asserted when the  $\mu$ PD70136 enters the hold acknowledge state in response to HLDRQ. Data, address, and control buses are not driven. See table 1.

## **INT (Interrupt Request)**

INT is asserted high by external logic to notify the CPU that an external event has occurred that requires the CPU's attention. After INT has been sampled high, and if the IE (enable interrupts) bit in the PSW is high, interrupt processing will begin after the current instruction is completed.

INT is sampled on the rising edge of each clock. After being asserted high, INT must be kept high until the first INTAK cycle begins. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

### NMI (Nonmaskable Interrupt Request)

NMI is asserted by external logic to notify the CPU that an external event has occurred which requires the CPU's immediate attention. When NMI is sampled low, interrupt processing will begin immediately after the current instruction is completed. A trap will be taken through vector 2. The state of the IE bit in the PSW has no effect on NMI acceptance.

NMI is sampled on the rising edge of each clock. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

Once NMI is samped low, an internal flag is set, so that a one-clock pulse meeting setup and hold times will be recognized. The flag is cleared when the NMI is accepted and can be set again immediately.

## **CPBUSY** (Coprocessor Busy)

$\overline{\text{CPBUSY}}$  is asserted low by a coprocessor (such as  $\mu\text{PD72291}$ ) when it is busy with an internal operation. The  $\mu\text{PD70136}$  uses this pin to check the status of the coprocessor.

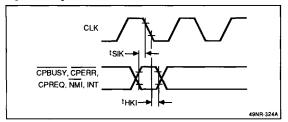

CPBUSY is sampled on the falling edge of each clock. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

## **CPERR** (Coprocessor Error)

<u>CPERR</u> is asserted low by a coprocessor to notify the μPD70136 of an error.

CPERR is sampled on the falling edge of each clock. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

### **CPREQ** (Coprocessor Request)

CPREQ is asserted high by a coprocessor to request the  $\mu$ PD70136 to run a memory operation for the coprocessor.

CPREQ is sampled on the falling edge of each clock. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

## **RESET (Reset)**

RESET is asserted high when external logic needs to initialize the  $\mu$ PD70136; for instance, after power-up. When RESET is asserted for at least 6 clock periods, the  $\mu$ PD70136 will abort any current bus cycles and initialize the registers as shown in table 4.

Table 4. Register Initialization by Reset

| Register | Offset Value | - |

|----------|--------------|---|

| PFP      | 0000H        |   |

| PC       | 0000H        |   |

| PS       | FFFFH        |   |

| SS       | 0000H        |   |

| DS0      | 0000H        |   |

| DS1      | 0000H        |   |

|     |   |   |   |   |   |   |   |   |   | _ | - | 4 | _ |   | - | - |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PSW | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| Cleared                                                                                     |

|---------------------------------------------------------------------------------------------|

| Normal Address Mode                                                                         |

| Undefined (if power has just been turned on) Unchanged (if power on, but RESET is asserted) |

|                                                                                             |

Refer to table 1 for the state of the  $\mu$ PD70136 outputs during reset. When RESET is deasserted low, the  $\mu$ PD70136 will begin fetching from address 0FFFF0H. This input is not internally synchronized. To ensure proper device operation, minimum setup and hold times must be met.

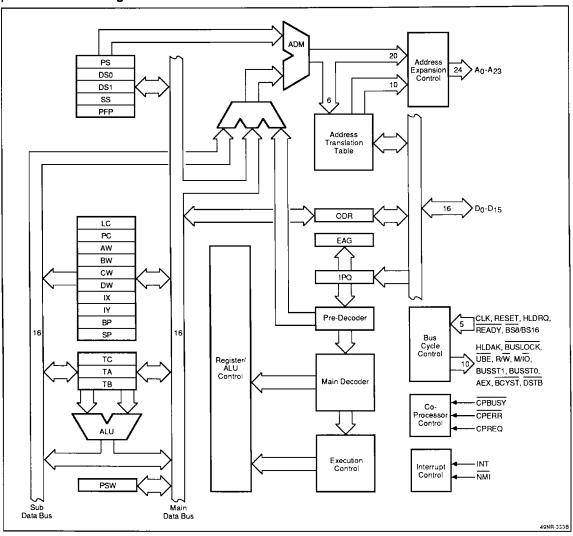

## μPD70136 Block Diagram

### **ELECTRICAL SPECIFICATIONS**

## **Absolute Maximum Ratings**

$T_A = +25^{\circ}C$

| Power supply voltage, V <sub>DD</sub> | -0.5 to +7.0 V                    |

|---------------------------------------|-----------------------------------|

| Input voltage, V <sub>I</sub>         | -0.5 V to V <sub>DD</sub> + 0.3 V |

| CLK input voltage, V <sub>K</sub>     | -0.5 V to V <sub>DD</sub> + 1.0 V |

| Output voltage, V <sub>O</sub>        | -0.5 V to V <sub>DD</sub> + 0.3 V |

| Operating temperature, TOPT           | -10 to +70°C                      |

| Storage temperature, T <sub>STG</sub> | -65 to +150°C                     |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage.

## Capacitance

$T_A = +25^{\circ}C$ ,  $V_{DD} = 0 V$

| Parameter         | Symbol | Max | Unit | Conditions                          |

|-------------------|--------|-----|------|-------------------------------------|

| Input capacitance | Cı     | 15  | pF   | fc = 1 MHz;                         |

| I/O capacitance   | CIO    | 15  | рF   | unmeasured pins<br>returned to 0 V. |

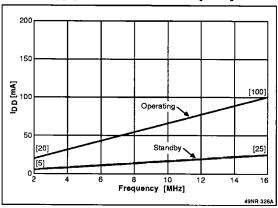

## Typical Supply Current vs Clock Frequency

### **DC Characteristics**

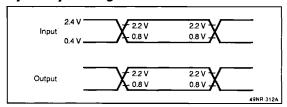

$T_A = -10 \text{ to } +70^{\circ}\text{C}, V_{DD} = +5 \text{ V} \pm 10\%$

| Parameter                                                   | Symbol           | Min                 | Тур | Max                   | Unit | Conditions               |

|-------------------------------------------------------------|------------------|---------------------|-----|-----------------------|------|--------------------------|

| Input voltage high                                          | V <sub>IH</sub>  | 2.2                 |     | V <sub>DD</sub> + 0.3 | ٧    | -                        |

| Input voltage low                                           | V <sub>IL</sub>  | -0.5                |     | 0.8                   | V    |                          |

| CLK Input voltage high                                      | V <sub>KH</sub>  | 0.8 V <sub>DD</sub> |     | V <sub>DD</sub> + 0.5 | V    |                          |

| CLK input voltage low                                       | V <sub>KL</sub>  | -0.5                | -   | 0.6                   | v    | <del></del>              |

| Output voltage high                                         | V <sub>OH</sub>  | 0.7 V <sub>DD</sub> | _   | -                     | v    | I <sub>OH</sub> -400 mA  |

| Output voltage low                                          | V <sub>OL</sub>  |                     |     | 0.45                  | V    | I <sub>OL</sub> = 2.5 mA |

| Input leakage current high                                  | ILIH             |                     |     | -10                   | μА   | $V_I = V_{DD}$           |

| input leakage current low                                   | ILIL             |                     |     | 10                    | μА   | V <sub>1</sub> = 0 V     |

| Output leakage current high                                 | ILOH             |                     |     | 10                    | μА   | $V_O = V_{DD}$           |

| Output leakage current low                                  | I <sub>LOL</sub> |                     |     | -10                   | μА   | V <sub>O</sub> = 0 V     |

| Supply current                                              | I <sub>DD</sub>  | 16 MHz              | 100 | 150                   | mA   | Normal operation         |

|                                                             | (see graph)      |                     | 25  | 35                    | mA   | Standby mode             |

|                                                             |                  | 12.5 MHz            | 75  | 110                   | mA   | Normal operation         |

|                                                             |                  |                     | 20  | 30                    | mA   | Standby mode             |

| *Stop mode current is not a function of CPU clock frequency |                  | #                   |     | 200                   | μА   | Stop mode                |

## μPD70136 (V33)

**AC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = 5 \text{ V} \pm 10\%; C_L = 100 \text{ pF}$

|                                           |                     | 12.5-MHz Lim                            | nits | 16 MHz-Limit                            |     |      |

|-------------------------------------------|---------------------|-----------------------------------------|------|-----------------------------------------|-----|------|

| Parameter                                 | Symbol              | Min                                     | Max  | Min                                     | Max | Unit |

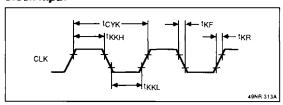

| Clock period                              | t <sub>CYK</sub>    | 80                                      | 500  | 62.5                                    | 500 | ns   |

| Clock high-level width                    | <sup>t</sup> ккн    | 35                                      |      | 25                                      |     | ns   |

| Clock low-level width                     | <sup>t</sup> KKL    | 35                                      |      | 25                                      |     | ns   |

| Clock rise time (1.7 V → 3.0 V)           | t <sub>KR</sub>     |                                         | 5    |                                         | 5   | ns   |

| Clock fall time (3.0 V → 1.7 V)           | t <sub>KF</sub>     |                                         | 5    |                                         | 5   | ns   |

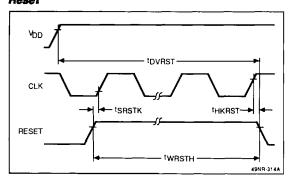

| Reset delay time (V <sub>DD</sub> valid)  | <sup>‡</sup> DVRST  | 1                                       |      | 1                                       |     | μs   |

| Reset setup time (CLK ↓)                  | <sup>t</sup> SRSTK  | 10                                      |      | 10                                      |     | ns   |

| Reset hold time (CLK ↓)                   | †HKRST              | 15                                      |      | 15                                      |     | ns   |

| Reset high time                           | twrst h             | 6                                       | •    | 6                                       |     | ‡CYI |

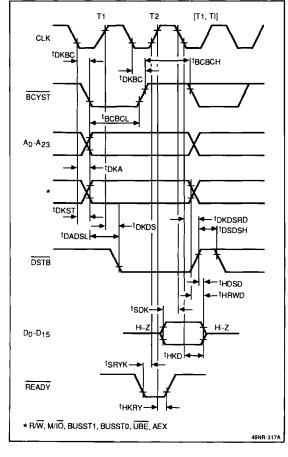

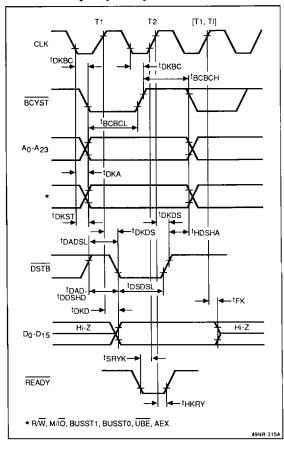

| CLK ↓ → BCYST delay                       | <sup>‡</sup> DKBC   | 5                                       | 40   | 5                                       | 40  | ns   |

| BCYST low-level width                     | tBCBCL              | t <sub>CYK</sub> - 10                   |      | t <sub>CYK</sub> - 10                   |     | ns   |

| BCYST high-level width                    | tвсвсн              | t <sub>CYK</sub> (n + 1) -10            |      | t <sub>CYK</sub> (n + 1) -10            |     | ns   |

| CLK ↓ → address delay                     | <sup>t</sup> DKA    | 5                                       | 40   | 5                                       | 40  | ns   |

| CLK ↓ → status delay                      | t <sub>DKST</sub>   | 5                                       | 40   | 5                                       | 40  | ns   |

| READY setup time (CLK ↑)                  | †SRYK               | 7                                       |      | 7                                       |     | ns   |

| READY hold time (CLK †)                   | tHKRY               | 15                                      |      | 15                                      |     | ns   |

| CLK↑ → data output delay                  | t <sub>DKD</sub>    | 5                                       | 40   | 5                                       | 40  | ns   |

| Floating delay                            | t <sub>FK</sub>     | 0                                       | 50   | 0                                       | 50  | ns   |

| CLK↑ → DSTB delay                         | <sup>‡</sup> DKDS   | 5                                       | 40   | 5                                       | 40  | ns   |

| Address/status output → DSTB ↓ delay time | <sup>‡</sup> DADSL  | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |      | t <sub>KKL</sub> + t <sub>KR - 15</sub> | -   | ns   |

| DSTB ↑ address/status hold time           | thosha              | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |      | t <sub>KKL</sub> + t <sub>KR</sub> ~ 15 |     | ns   |

| DSTB low-level width                      | t <sub>DSDSL</sub>  | t <sub>CYK</sub> (n+1) - 10             |      | t <sub>CYK</sub> (n+1) - 10             |     | ns   |

| DSTB high-level width                     | t <sub>DSDSH</sub>  | t <sub>KKL</sub> + t <sub>KR</sub> - 10 |      | t <sub>KKL</sub> + t <sub>KR</sub> 10   |     | ns   |

| CLK ↓ → DSTB ↑ delay for read cycle       | <sup>‡</sup> DKDSRD | 5                                       | 40   | 5                                       | 40  | ns   |

| Address/status output → data delay time   | <sup>‡</sup> DAD    | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |      | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |     | ns   |

| DSTB ↑ → data output delay time           | <sup>‡</sup> DDSHD  | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |      | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |     | ns   |

| Data setup time (CLK ↓)                   | t <sub>SDK</sub>    | 7                                       |      | 7                                       |     | ns   |

| Data hold time (CLK ↓)                    | t <sub>HKD</sub>    | 10                                      |      | 10                                      |     | ns   |

| Data hold time (DSTB ↑)                   | t <sub>HDSD</sub>   | 0                                       |      | 0                                       |     | ns   |

| Data hold time (R/W ↓)                    | thrwd               | 0                                       |      | 0                                       |     | ns   |

| BS8/BS16 setup time                       | t <sub>SBSK</sub>   | 7                                       |      | 7                                       |     | ns   |

| BS8/BS16 hold time                        | t <sub>HKBS</sub>   | 15                                      |      | 15                                      |     | ns   |

| HLDRQ setup time (CLK↑)                   | t <sub>SHQK</sub>   | 7                                       |      | 7                                       |     | ns   |

| HLDRQ hold time (CLK↑)                    | tнкна               | 15                                      |      | 15                                      |     | ns   |

| CLK ↑ → HLDAK delay time                  | t <sub>DKHA</sub>   | 5                                       | 40   | 5                                       | 40  | ns   |

| Output float → HLDAK delay                | <sup>t</sup> DFHA   | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |      | t <sub>KKL</sub> + t <sub>KR</sub> - 15 |     | ns   |

| NMI, INT, CPBUSY setup time (CLK ↓)       | <sup>t</sup> sıĸ    | 10                                      |      | 10                                      |     | ns   |

| NMI, INT, CPBUSY setup time (CLK ↓)       | tнкі                | 10                                      |      | 10                                      |     | ns   |

Note: 'n' means number of wait cycles to be inserted into bus cycle

## **Timing Waveforms**

## Input/Output Voltage Reference Levels

## Input Setup/Hold Time

## Clock Input

## Reset

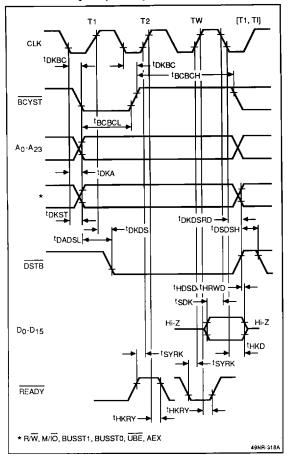

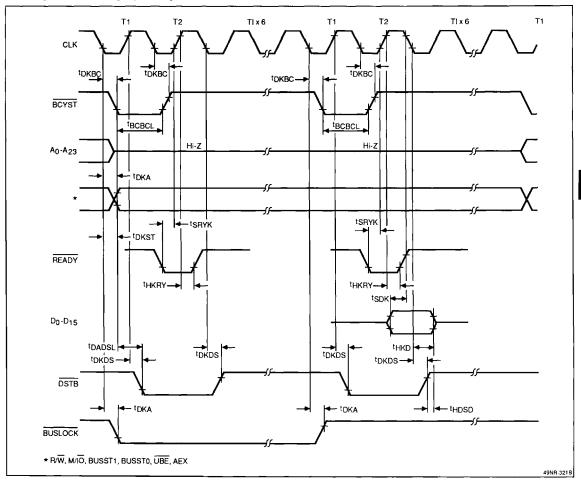

## Basic Read Cycle (0 WAIT)

### **Bus Lock**

## Basic Write Cycle (0 WAIT)

## Basic Read Cycle (1 WAIT)

## Basic Write Cycle (1 WAIT)

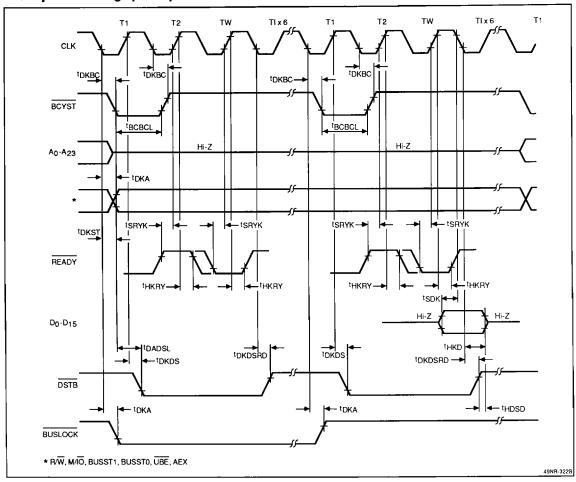

## Bus Sizing Cycle (0 WAIT)

## Bus Sizing Cycle (1 WAIT)

## Interrupt Acknowledge (0 WAIT)

## Interrupt Acknowledge (1 WAIT)

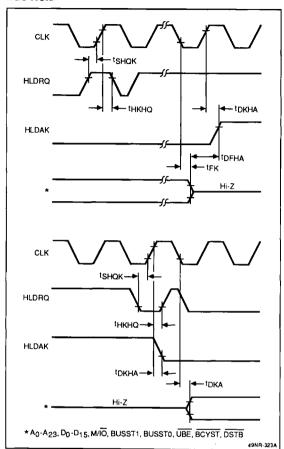

### **Bus Hold**

36

#### **FUNCTIONAL DESCRIPTION**

#### Architecture

A unique hardware architecture feature of the  $\mu$ PD70136 is that there is no microcode. Instruction decode and data path control are implemented using logic and small independent state machines. This greatly enhances the speed with which instructions can be executed, in the same way that programs written in assembly language can be faster and more efficient than high-level language code. The  $\mu$ PD70136 is four times faster than the  $\mu$ PD70116.

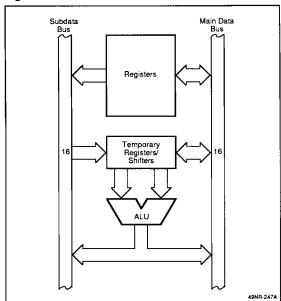

The  $\mu$ PD70136 hardware comprises the execution unit, a bus interface, and the address generator. See the  $\mu$ PD70136 Block Diagram.

#### **Execution Unit**

The μPD70136 execution unit consists of a register file, an ALU, instruction decode, and execution control logic.

Besides the hardware control logic, the most significant feature of the execution unit is a dual-bus internal data path. See figure 1. The ALU and many registers are dual-ported, with a data bus on each port. This allows two operands to be transferred in one clock cycle instead of two. Performance is improved by as much as 30 percent using the dual data bus concept.

Figure 1. Dual Data Buses

Register File. There are 12 registers in the internal RAM. Four are temporary registers used in the execution of certain instructions (LC, TA, TB, TC). The other eight are general-purpose registers (AW, BW, CW, DW, IX, IY, BP, SP) and either contain operand data or point to operand data in memory.

The temporary registers speed up instruction execution by serving as scratch pad registers during complex operations.

The loop counter (LC) is used during primitive block transfer operations. It contains the count value. It is also used as a shift counter for multiple-bit shift and rotate instructions.

Temporary registers TA, TB, and TC are the inputs to the ALU. They are used as temporary registers/shifters during multiply, divide, shift/rotate, and BCD rotate operations.

**ALU.** The ALU consists of a complete adder and logical operation unit. It executes arithmetic (ADD, SUB, MUL, DIV, INC, DEC, NEG, etc.) and logical (TEST, AND, OR, XOR, NOT, SET1, CLR1, etc.) instructions.

Data Path Control Logic. This logic comprises the main instruction decoder and the execution control blocks. Its purpose is to decide what operations must be done and to schedule them. It transfers operands as needed and controls the ALU. State machines are used to implement long, complex instructions.

## **Bus Interface**

The bus interface comprises bus control logic, an operand data register (ODR), an 8-byte instruction prefetch queue (IPQ), and an effective address generator.

The bus control state machines implement the  $\mu$ PD70136 bus interface. To allow the bus machine to run independent of the execution unit, an operand data register is used. During a CPU write cycle, the write data is placed in the ODR and the execution of the next instruction proceeds without waiting. The bus interface finishes the write cycle when the bus is available. During a read cycle, if the operand requires two bus cycles (as in a read from an odd address), the full 16-bit value is assembled in the ODR, one byte at a time.

Instruction Prefetching. The µPD70136 is a pipelined machine. To keep the pipeline running efficiently, it should be kept full of instructions in various stages of execution. Instructions are fetched before they are needed and placed in the IPQ. Data in the IPQ is broken out by the pre-decoder logic to determine what addressing modes will be used and what CPU resources will be required to execute the prefetched instruction. To keep

the 8-byte IPQ full, the bus control logic will schedule an instruction prefetch cycle whenever there are at least 2 unused bytes in the IPQ.

The IPQ is cleared whenever a control transfer instruction (any branch, call, return, or break) is executed. This is done because a different instruction stream will be used following a control transfer, and the IPQ will then contain instruction data that will never be used. When this happens, the  $\mu$ PD70136's pipeline will empty out, hampering performance. To maximize performance, the number of control transfers should be minimized.

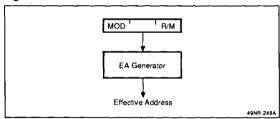

Effective Address Generator. The EAG logic computes a 16-bit effective address for each operand, which is an offset into one of the four segments. This effective address is passed on to the address modifier adder. The EAG decodes the first byte(s) of each instruction to determine the addressing mode and initiates any bus cycles required to fetch pointers/offsets from memory. Effective addresses are calculated in a maximum of 1 clock period, compared to 5 to 12 clocks for a microprogrammed machine. See figure 2.

Figure 2. Effective Address Generator

#### Address Generator

The address generator comprises the address register file, the address modifier (ADM), the address translation table, and the needed control logic.

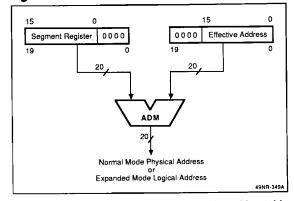

The registers in the address register file are PS, SS, DS0, DS1, PC, and PFP. The ADM is a dedicated adder that adds one of the segment registers to the effective address to produce the 20-bit normal address. The ADM also increments the prefetch pointer. If expanded addressing is enabled, the address translation table is accessed to map the 20-bit address into a 24-bit expanded address.

For instruction stream data, addresses are generated differently. The prefetch pointer contains a 16-bit offset into the PS segment that points to the next instruction word to be prefetched. The program counter contains an offset into the PS segment that points to the instruction

that is currently being executed. As part of all control transfers, the PFP is set to the same value as the PC.

#### ADDRESSING MECHANISM

The  $\mu$ PD70136 is completely compatible with the  $\mu$ PD70108/116 in its addressing modes, and in the way that addresses are computed. It offers a method of expanding the memory address space to 16M bytes.

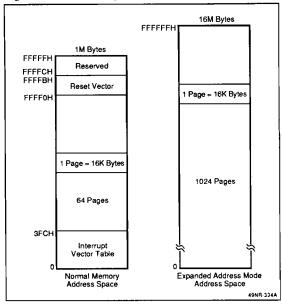

The I/O space is 64K bytes (16-bit address). The normal memory address space is 1M byte (20-bit address), and the expanded address space is 16M bytes (24-bit address). Expanded addressing is enabled or disabled using the BRKXA and RETXA instructions.

The memory space is accessed when an instruction uses a memory addressing mode. Memory addresses are calculated as described below. The I/O space can only be accessed through the IN, OUT, INM, and OUTM instruction.

Certain areas of the  $\mu$ PD70136 address (physical for normal mode, and logical for expanded addressing mode) spaces are reserved. These areas are shown in figures 3 and 4. Memory addresses 0-3FCH are used for the Interrupt Vector table located in the Interrupt Operation section. Memory addresses FFFF0H-FFFFH must contain a branch to boot code; PC, PFP, and PS are initialized at RESET to point to this area. I/O addresses FF00H-FF80H are reserved for the address translation registers.

Figure 3. I/O Address Space

#### I/O Addresses

I/O addresses are always taken from 8-bit immediate data or the DW register. DW is always used as a direct pointer into the I/O address space. If I/O operations require the use of other more complex addressing modes, the I/O devices must be placed in the memory address space (using memory-mapped I/O techniques). For memory-mapped I/O devices, there are no restrictions on instruction or addressing mode usage. However,

the  $\mu$ PD70136 will not automatically insert 6 clock cycles after memory-mapped I/O operations; external logic must provide the needed I/O device recovery time.

Figure 4. Address Space

### Normal Memory Addresses

The μPD70136 is a 16-bit device with 16-bit registers. To allow a memory address space larger than 64K bytes, memory segmentation is used. The 1M-byte memory address space is divided into 64K byte segments. Up to four segments can be in use at any given time. The base addresses of the four active segments (program segment, stack segment, data segment 0, and data segment 1) are contained in four 16-bit segment registers (PS, SS, DSO, and DS1, respectively). The 16-bit value in each register is the upper 16 bits of the 20-bit memory address. Thus, segments always start on 16-byte boundaries.

As described above, the  $\mu$ PD70136 hardware generates a 16-bit effective address for each memory operation. This effective address is an offset into one of the four active segments. The actual 20-bit memory address is computed by adding the EA to the segment register value expanded with zeros to 20 bits. Figure 5 shows this process.

Figure 5. 20-Bit Address

If normal addressing mode is enabled, then this 20-bit result is presented on the address bus during the bus cycle. If expanded addressing mode is enabled, this address is used as a logical address.

## **Expanded Addresses**

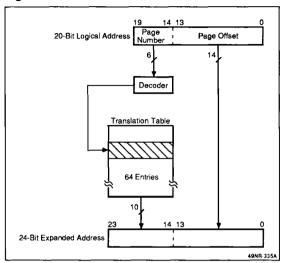

In the expanded addressing mode, the memory space is divided into 1024 pages. Each page is 16K bytes. Each page of the normal 20-bit address space is mapped to a page in the expanded address space using a 64-entry address translation table. The table is made up of 64 page registers that reside in the I/O space (figure 4).

The programming model of this mode is the same as for the normal mode. Address expansion is a layer added to the normal mode that is transparent to executing code. The program still sees a 20-bit contiguous logical memory address space, but the hardware sees 64 pages mapped into a set of 1024 physical pages.

The I/O space is not affected by the expanded addressing mode.

The address translation mechanism is shown in figure 6. The upper 6 bits of the logical 20-bit address select one of the entries in the address translation table, which supplies a 10-bit value. This value is substituted for the original 6 bits in the normal address to create a 24-bit expanded address.

Figure 6. Address Translation Mechanism

## **Address Expansion Registers**

These are the page and XAM registers. Word IN and OUT instructions are used to access these registers. The table below shows page register usage and I/O addresses. The page registers contain the 10-bit physical page base address.

| A <sub>19</sub> -A <sub>14</sub> |              |                 |

|----------------------------------|--------------|-----------------|

| Logical Address                  | PGR Selected | PGR I/O Address |

| 0                                | PGR1         | FF00            |

| 1                                | PGR2         | FF02            |

| 2                                | PGR3         | FF04            |

| 3                                | PGR4         | FF06            |

| :                                | :            | :               |

| 63                               | PGR64        | ·FF7E           |

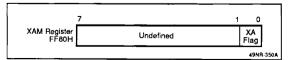

The XAM register (figure 7) is a read-only status flag that indicates whether expanded addressing is enabled. Unused data bits in the XAM register are undefined. Expanded addressing must be disabled before accessing any of the page registers. I/O operations to these internal registers are not passed to the bus interface and will not be seen by external logic.

Figure 7. XAM Register

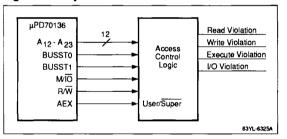

### Memory Protection Mechanism

The  $\mu$ PD70136 expanded mode provides a harware memory protection mechanism (figure 8) that does not sacrifice software compatibility with existing  $\mu$ PD8088/8086 or V20/V30/V40/V50 programs. In expanded mode, the XAM and PGR registers cannot be accessed. This provides simple two-level protection.

A supervisory system task running in normal mode can set up restricted memory spaces for less privileged user tasks by programming the PGR registers and then starting up the user task in expanded mode. The user task will not be able to change its memory map to access privileged memory areas. External access control logic can monitor the AEX output to determine at which privilege level the CPU is currently running (AEX = 0 is supervisor mode, AEX = 1 is user mode) and permit or prevent each bus cycle, thereby providing additional memory and I/O protection. This scheme provides the basic hardware protection needed for most operating systems without forgoing full software compatibility.

Figure 8. Expanded Mode Protection Mechanism

#### **OPERAND ADDRESSING MODES**

For operand addressing, the  $\mu$ PD70136 offers 9 modes:

- Register

- Based

- immediate

- Based index

- Direct

- Bit

- Register indirect

- Autoincrement/autodecrement

- Indexed

### Register

The operand is in a  $\mu$ PD70136 register pointed to by the instruction.

### Immediate

The operand is in the instruction stream following the opcode of the instruction. This data will have been prefetched. Immediate data uses the  $\mu$ PD70136 pipeline efficiently.

## μPD70136 (V33)

#### Direct

Immediate data in the instruction stream points directly to the operand. This data can be a 16-bit effective address or a 4-bit bit field length.

### Register Indirect

A 16-bit register (IX, IY, or BW) contains a 16-bit effective address.

#### Indexed

One or two bytes of immediate data are treated as a signed displacement that is added to the contents of a 16-bit index register (IX or IY) to obtain a 16-bit effective address.

#### Based

One or two bytes of immediate data are treated as a signed displacement that is added to the contents of a 16-bit base register (BP or BW) to form a 16-bit effective address.

#### Based Indexed

One or two bytes of immediate data are treated as a signed displacement that is added to two 16-bit registers (one of BP or BW with one of IX or IY) to form the effective address. This mode is useful for array addressing.

#### Bit

Used with NOT1, SET1, CLR1, or TEST1. A 4-bit immediate data value is used to select a bit in a 16-bit operand. For 8-bit operands, only 3 bits are used.

#### Autoincrement/Autodecrement

Some interactive operations (such as MOVBK or INS) will automatically increment or decrement index registers after each iteration. Specifically, IX is used in addressing a source pointer, and/or IY is used in addressing a destination pointer. After the operation, both will be incremented or decremented (according to the PSW DIR control flag) to point to the next operand in the array.

## **INSTRUCTION ADDRESSING MODES**

These modes are basically the same as the operand addressing modes, but the PC is always used as the register. The seven modes are used in control transfer instructions:

Direct

- Relative

- Register

- Register indirect

- Indexed

- Based

- Based indexed

#### Direct

Four bytes of immediate data are taken as an absolute address and loaded directly into the PS and PC (and PFP).

#### Relative

One or two bytes of immediate data are a signed displacement that is added to the contents of the PC and then placed in the PC (and PFP). This mode is used to create position-independent code.

### Register

The register selected by the instruction (AW, BW, etc.) contains an effective address, which is loaded into the PC (and PFP).

### Register Indirect

An index register (IX, IY, or BW) points to a memory location that contains an effective address (short pointer) or a segment register value and an effective address (far pointer). This effective address is read from memory and loaded into the PS and/or PC (and PFP).

#### Indexed

One or two bytes of immediate data are a signed displacement that is added to the contents of a 16-bit index register (IX or IY) to form an effective address. This address is used to fetch another effective address, which is loaded into the PC (and PFP).

#### Based

One or two bytes of immediate data are a signed displacement that is added to the contents of a 16-bit base register (BP or BW) to form an effective address. This address is used to fetch another effective address from memory, which is then loaded into the PC (and PFP).

### Based Indexed

One or two bytes of immediate data are a signed displacement that is added to the contents of two 16-bit register (one of BP or BW with one of IX or IY) to form an

effective address. This address is used to fetch another effective address from memory, which is then loaded into the PC (and PFP).

#### REGISTER CONFIGURATION

## Program Counter (PC)

The PC is a 16-bit register that contains the effective address of the instruction that is currently being executed. The PC is incremented each time the instruction decoder accepts a new instruction from the prefetch queue. The PC is loaded with a new value during execution of a branch, call, return, or break instruction and during interrupt processing.

## Segment Registers (PS, SS, DS0, DS1)

There are four segment registers, each of which contains the upper 16 bits of the base address of a 64K logical segment. Since logical segments reside on 16-byte boundaries, the lower 4 bits of the base address are always 0. Normal 20-bit memory addresses are formed by adding the 16-bit effective address to the base address of one of the segments. When performing this operation, certain types of effective addresses will be paired with specific segment registers.

| Segment Register     | <u>Default Offset</u> |

|----------------------|-----------------------|

| PS (program segment) | PFP                   |

| SS (stack segment)   | SP, effective address |

| DS0 (data segment 0) | IX, effective address |

| DS1 (data segment 1) | IY                    |

Program instructions will always be fetched from the program segment. Whenever the IY index register is used to address an operand, the DS1 segment register will be used. DS0 is usually used with IX. Stack operations using the SP will always use the stack segment. For other effective addresses, the preceding table shows the default segment used, but another segment may be selected by using a segment override prefix instruction.

## General-Purpose Registers (AW, BW, CW, DW)

The four 16-bit general-purpose registers can be accessed as 16-bit or 8-bit quantities. When the AW, BW, CW, or DW designations are used, the register will be 16 bits. When AL, AH, BL, BH, CL, CH, DL, or DH is used, the register will be 8 bits. AL will be the low byte of AW, and AH the high byte, and so on.

Some operations require the use of specific registers:

AW Word multiplication/division, word I/O, data conversion

- AL Byte multiplication/division, byte I/O, BCD rotation, data conversion, translation

- AH Byte multiplication/division

- BW Translation

- CW Shift instructions, rotation instructions, BCD operations

- DW Word multiplication/division, indirect addressing I/O

## Pointer (SP, BP) and Index (IX, IY) Registers

These registers are used as base pointers and index registers when based, indexed, or based-indexed addressing modes are used. They may also be used as general-purpose registers in data transfer, arithmetic, and logical instructions. They can only be accessed as 16-bit registers.

Some operations use these registers in specific ways:

- SP Stack operations

- IX Source pointer for block transfer, bit field, and BCD string operations

- IY Destination pointer for block transfer, bit field, and BCD string operations

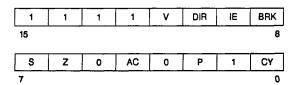

## Program Status Word (PSW)

The program status word reflects the status of the CPU with six status flags, and affects the operation of the CPU through three control flags:

| Stat | us Flags        | Contro | ol Flags         |

|------|-----------------|--------|------------------|

| V    | Overflow        | DIR    | Direction        |

| S    | Sign            | ΙE     | Interrupt enable |

| Z    | Zero            | BRK    | Break            |

| AC.  | Auxiliary carry |        |                  |

AC Auxiliary carry

P Parity

CY Carry

The PSW cannot be accessed directly as a 16-bit register. Specific instructions are used to set/reset the control flags. When the PSW is pushed on the stack (as during interrupt processing), the following image is used.

## **BUS OPERATION OVERVIEW**

The  $\mu$ PD70136 uses a synchronous bus interface. The CLK input supplies the  $\mu$ PD70136 with a clock. All

μPD70136 bus timings and instruction execution clock counts are specified relative to this clock. Bus cycles start on the falling edge of CLK. Each bus cycle is two clock periods long, and may be extended by adding wait states.

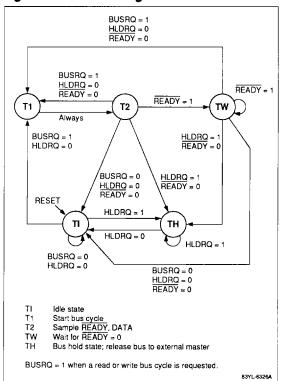

Figure 9 is the state diagram of the bus control state machine. The first state of every bus cycle is T1, followed immediately by T2. READY is sampled on the rising (middle) edge of T2. If READY is not asserted, then the next bus state will be a TW wait state. TWs will be inserted until READY is sampled low, after which the bus cycle will finish. The dynamic bus sizing input, BS8/BS16, is sampled at the same time as READY.

Figure 9. Bus State Diagram

Address and bus status are output after the leading edge of T1 and are maintained until after the cycle is completed. A strobe, BCYST, is asserted during T1 to indicate the beginning of a bus cycle. BCYST is output following the leading edge of T1 and is deasserted after the leading edge of T2.

Write data is driven on D<sub>0</sub>-D<sub>15</sub> following the rising (middle) edge of T1 and is maintained until after the rising edge of the cycle following T2 or the last TW. The read data is sampled on the trailing edge of T2 or the last TW state. A strobe ( $\overline{DSTB}$ ) gives the status of the  $\mu PD70136$  data bus.  $\overline{DSTB}$  is asserted after the rising edge (middle) of T1.  $\overline{DSTB}$  is deasserted after the rising edge of T2 or the last TW for a write cycle, and after the trailing edge of T2 or the last TW for a read cycle.

I/O cycles are identical to memory cycles except for the encoding of the bus status lines. However, six idle states are inserted after every I/O bus cycle to provide a recovery time for slow I/O devices.

## **Dynamic Bus Sizing**

The  $\mu$ PD70136 supports dynamic bus sizing. On a cycle by cycle basis, the width of the data bus can be changed from 16 to 8 bits. This simplifies the connection of 8-bit I/O devices that may have internal registers at consecutive byte addresses. Other 16-bit CPUs require two ROMs for startup code, but the  $\mu$ PD70136 dynamic bus sizing makes it possible to use a single 8-bit wide ROM.

External logic requests an 8-bit data path by driving  $\overline{BS8}/BS16$  low in time for the  $\mu PD70136$  to sample it on the rising edge of T2 (or TW). The  $\mu PD70136$  will perform an additional bus cycle if needed to finish the operation in byte-wide pieces.

Referring to tables 5 and 6, if the bus operation is 8 bits wide, no further bus cycles will occur. For a read cycle, the data will be sampled on  $D_0$ - $D_7$ . For a write cycle to an even address, data will be driven on  $D_0$ - $D_7$ . On all byte writes to an odd address, the  $\mu$ PD70136 will put the byte data on both upper and lower data buses; the write data will be on  $D_0$ - $D_7$  as well as  $D_8$ - $D_{15}$ .

If the bus operation is 16-bit, then two bus cycles will be required. The first one, in which  $\overline{BS8}/BS16$  is sampled low, will handle the low byte. The second cycle will take the form of a byte read or write using  $D_0$ - $D_7$ .

## **Bus Cycle Types**

The 11 different types of µPD70136 bus cycles are classified as read, write, and acknowledge cycles.

## Read Cycles

The read cycles are memory, I/O, coprocessor, data reads, and instruction fetch. All have the general timing described above. Coprocessor reads are used to access the internal registers of a coprocessor. Coprocessor data reads are used to transfer data from memory to an internal coprocessor register.

Table 5. Write Cycle Bus Sizing

|              |      |     |       |                                 | 16-Bit Bus (B                  | \$8/BS16 = 1)                   | 8-Bit Bus (BS                  | 88/BS16 = 0 |

|--------------|------|-----|-------|---------------------------------|--------------------------------|---------------------------------|--------------------------------|-------------|

| Type Address | Ao   | UBE | Cycle | D <sub>15</sub> -D <sub>8</sub> | D <sub>7</sub> -D <sub>0</sub> | D <sub>15</sub> -D <sub>8</sub> | D <sub>7</sub> -D <sub>0</sub> |             |

| Byte         | Even | 0   | 1     | 1st                             | Invalid                        | Byte                            | invalid                        | Byte        |

|              | Odd  | 1   | 0     | 1st                             | Byte                           | Byte                            | Byte                           | Byte        |

| Word         | Even | 0   | 1     | 1st                             | Upper                          | Lower                           | Upper                          | Lower       |

|              |      | 1   | 0     | 2nd                             | Not needed t                   | or 16-bit bus                   | Upper                          | Upper       |

|              | Odd  | 1   | 0     | 1st                             | Lower                          | Lower                           | Lower                          | Lower       |

|              |      | 0   | 1     | 2nd                             | Upper                          | Upper                           | Invalid                        | Upper       |

Table 6. Read Cycle Bus Sizing

|      |         |                 |     |       | 16-Bit Bus (B                   | <del>\$8</del> /B\$16 = 1)     | 8-Bit Bus (BS                   | $\bar{8}/BS16 = 0)$            |

|------|---------|-----------------|-----|-------|---------------------------------|--------------------------------|---------------------------------|--------------------------------|

| Туре | Address | _A <sub>0</sub> | ÜBE | Cycle | D <sub>15</sub> -D <sub>8</sub> | D <sub>7</sub> -D <sub>0</sub> | D <sub>15</sub> -D <sub>8</sub> | D <sub>7</sub> -D <sub>0</sub> |

| Byte | Even    | 0               | 1   | 1st   | Not used                        | Byte                           | Not used                        | Byte                           |

|      | Odd     | 1               | 0   | 1st   | Byte                            | Not used                       | Not used                        | Byte                           |

| Word | Even    | 0               | 1   | 1st   | Upper                           | Lower                          | Not used                        | Lower                          |

|      |         | 1               | 0   | 2nd   | Not needed                      | for 16-bit bus                 | Not used                        | Upper                          |

|      | Odd     | 1               | 0   | 1st   | Lower                           | Lower                          | Not used                        | Lower                          |

|      |         | 0               | 1   | 2nd   | Not used                        | Upper                          | Not used                        | Upper                          |

I/O and memory reads are used to transfer data to the  $\mu\text{PD70136}$  from an I/O device or a memory location, respectively. Instruction fetches are used to fill the  $\mu\text{PD70136}$ 's 8-byte instruction queue from the memory space.

#### Write Cycles

There are four types of write cycles. Memory writes transfer data from the  $\mu$ PD70136 to a memory location. I/O writes transfer data from the  $\mu$ PD70136 to an I/O device. Coprocessor data writes transfer data from the coprocessor to a memory location. Coprocessor writes transfer data from the  $\mu$ PD70136 directly to a coprocessor internal register.

#### Interrupt Acknowledge Cycle

The interrupt acknowledge operation takes two consecutive INTAK bus cycles. The first cycle is used to freeze the state of an external interrupt controller, such as the  $\mu$ PD71059. The second INTAK bus cycle reads an 8-bit vector number on D<sub>0</sub>-D<sub>7</sub> supplied by the  $\mu$ PD71059. This vector number is used to index into the interrupt vector table to select an interrupt handler.

### Hait Acknowledge Cycle

When a HALT instruction is executed, a halt acknowledge cycle is issued to notify external logic that the

$\mu$ PD70136 is entering standby mode. This cycle is always two clocks long;  $\overline{READY}$  is ignored and  $\overline{DSTB}$  is not asserted.

#### Hold Request and Hold Acknowledge

At times, an external bus master will need to use the  $\mu$ PD70136 bus. When the HLDRQ input is asserted by external logic, the  $\mu$ PD70136 recognizes this as a request for external bus mastership. The  $\mu$ PD70136 will finish the current bus operation, stop driving its address, data, and control buses, and assert HLDAK. The external device, such as the  $\mu$ PD71071 or  $\mu$ PD71037 DMA controller, may then drive the  $\mu$ PD70136 bus. Note that if the current bus operation involves more than one bus cycle, such as a 16-bit access to an odd address or due to dynamic bus sizing, the  $\mu$ PD70136 will finish both cycles before releasing the bus.

If the current instruction uses the BUSLOCK prefix, HLDRQ will be ignored. This will be indicated by the BUSLOCK output. Also, during interrupt acknowledge, BUSLOCK is asserted between the two INTAK cycles so that HLDRQ is ignored until after the second INTAK.

#### SYSTEM INTERFACING

### System Memory Access Time

Table 7 shows the system memory access time required for 12.5-MHz and 16-MHz μPD70136 systems to run with

zero, one, two, and three wait states. This is the time from when the address bus is valid to when the external system must present the read data on the data bus. These numbers are based on the preliminary ac timing given in this document and are subject to change.

Table 7. Performance vs. Wait States

|                             |                                 | 12.5 MHz                         | 2                                   | 16 MHz                          |                                  |                                     |  |  |

|-----------------------------|---------------------------------|----------------------------------|-------------------------------------|---------------------------------|----------------------------------|-------------------------------------|--|--|

| Number<br>of Walt<br>States | Memory<br>Cycle<br>Time<br>(ns) | System<br>Access<br>Time<br>(ns) | Relative<br>Perfor-<br>mance<br>(%) | Memory<br>Cycle<br>Time<br>(ns) | System<br>Access<br>Time<br>(ns) | Relative<br>Perfor-<br>mance<br>(%) |  |  |

| 0                           | 160                             | 113                              | 78                                  | 125                             | 78                               | 100                                 |  |  |

| 1                           | 240                             | 193                              | 64                                  | 187.5                           | 140.5                            | 82                                  |  |  |

| 2                           | 320                             | 273                              | 52                                  | 250                             | 203                              | 67                                  |  |  |

| 3                           | 400                             | 353                              | 43                                  | 312.5                           | 265.5                            | 56                                  |  |  |

Note: Performance is relative to the 0 wait state, 16 MHz.

#### **Wait States**

Table 7 also shows the effect of wait states on performance. The  $\mu$ PD70136 overlaps bus interface operations in time with instruction execution. This greatly reduces the effect of wait states on performance. Each bus cycle is nominally two clocks long, while the minimum instruction time is two clocks, with many instructions taking longer. There is some idle bus time when the CPU is processing a long instruction and the prefetch queue is full. Wait states can often fill these idle states.

However, adding wait states to bus cycles reduces the bus bandwidth available for other bus masters, such as DMA controllers, since some of the idle time that would have been available to them is used for CPU cycles.

Note that in all cases, a 16-MHz  $\mu$ PD70136 with N+1 wait states is faster than a 12.5-MHz device with N wait states while using slower memories.

Please note also that these numbers were measured using a particular set of benchmarks and should be used for comparison purposes only. Different results will be obtained for other program mixes.

# Interfacing to the $\mu$ PD72291 Floating-Point Coprocessor

The  $\mu$ PD72291 (AFPP) is a very-high-performance floating-point coprocessor for the  $\mu$ PD70136 offering in excess of 530K floating-point operations per second at 16 MHz. The AFPP is programmed as an extension of the  $\mu$ PD70136 instruction set. The AFPP executes floating-point operations, computes transcendental functions, and performs vector multiplications.

AFPP instructions use the FP01 and FP02 formats. When one of these opcodes is encountered and an AFPP is connected, a coprocessor protocol routine is entered. The  $\mu\text{PD70136}$  will compute any effective addresses required, read or write the operands for the AFPP, and instruct the AFPP as to what operation should be performed. The AFPP reponds by asserting its BUSY output when it starts the operation. The  $\mu\text{PD70136}$  will not start another AFFP operation until BUSY is deasserted, but may execute CPU instructions. When BUSY is deasserted, the  $\mu\text{PD70136}$  will transfer the AFPP status to the AW register.

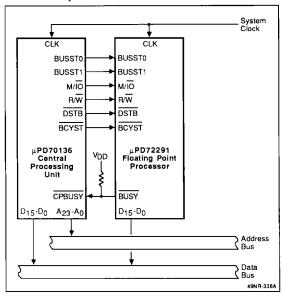

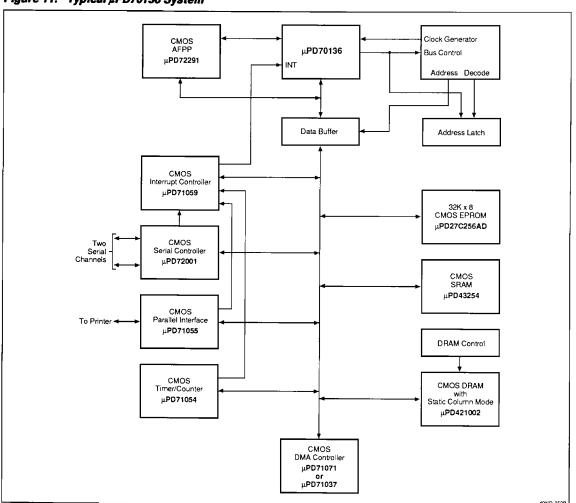

Figure 10 shows how to connect a μPD70136 CPU to a μPD72291 AFPP. Figure 11 shows a typical system. The CPU reads and writes status and commands to the AFPP using coprocessor read and write cycles, which always take two clocks. AFPP operands are written/read using coprocessor memory write/read cycles, which always require one wait state. External READY logic must take care to include this wait state.

Figure 10. Connections Between μPD70136 and μPD72291

On RESET,  $\overline{\text{CPBUSY}}$  is sampled. If it is low, the  $\mu\text{PD70136}$  assumes that a coprocessor is connected.  $\overline{\text{CPERR}}$  is also sampled to determine what kind of coprocessor is connected, as follows.

| <b>CPBUSY</b> | <b>CPERR</b> | Coprocessor |

|---------------|--------------|-------------|

| 1             | X            | None        |

| 0             | GND          | μPD72291    |

| 0             | $V_{DD}$     | Other       |

AFPP memory operands must always begin on even addresses and may not reside in 8-bit wide memory. Dynamic bus sizing may not be used for AFPP operands.

Figure 11. Typical µPD70136 System

## μPD70136 (V33)

### INTERRUPT OPERATION

The interrupts supported by the  $\mu$ PD70136 can be divided into two types: interrupts generated by external interrupt requests and traps generated by software processing. They are:

## **External Interrupts**

- NMI input (nonmaskable)

- INT input (maskable)

## **Software Traps**

- Divide error during DIV or DIVU instruction

- Array bound error during CHKIND

- Single-step (PSW BRK flag = 1)

- Undefined instruction

- Coprocessor error

- Coprocessor not connected

- Break instructions

BRKV BRK imm8

BRK3 BRKXA

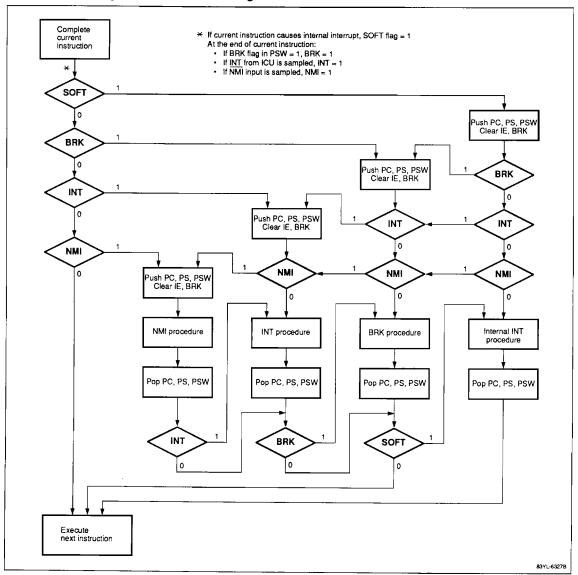

### Interrupt Priorities

Interrupts are prioritized as follows:

NMI > INT > BRK flag > others at same level

Interrupts are not accepted during certain times.  $\overline{\text{NMI}}$ , INT and BRK flags are not accepted in these cases:

- Between execution of MOV or POP that uses a segment register as an operand and the next instruction.

- (2) Between a segment override prefix and the next instruction

- (3) Between a repeat or BUSLOCK prefix and the next instruction

INT is not accepted when the PSW IE flag is 0, or between an RETI or POP PSW and the next instruction. Figure 12 is a flow diagram for processing interrupt requests.

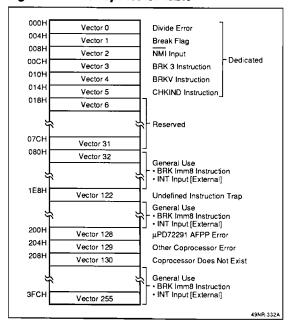

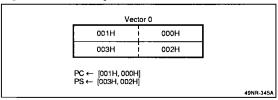

## Interrupt Vectors

Once an interrupt has been accepted, an interrupt service routine will be entered. The address of this routine is specified by an interrupt vector, which is stored in the interrupt vector table. For most interrupts, the vector used depends on what interrupt is being processed (e.g.,  $\overline{\text{NMI}}$  always uses vector 2). For INT and BRK imm8 interrupts, any vector may be used; the vector number is supplied by an external device in the case of INT (e.g., a  $\mu\text{PD71059}$ ), or by immediate data in the case of BRK.

Figure 13 is the interrupt vector table. The table uses 1K bytes of memory—addresses 000H to 3FFH—and stores up to 256 vectors (4 bytes per vector).

Figure 12. Interrupt Prioritization Flow Diagram

Each interrupt vector consists of 4 bytes. The 2 bytes in the low addresses of memory are loaded into PC as the offset, and the 2 high bytes are loaded into PS as the base address. Interrupt vector 0 in figure 14 is an example. The bytes are combined in reverse order. The lower-order bytes in the vector become the most significant bytes in the PC and PS, and the higher-order bytes become the least significant.

Based on this format, the contents of each vector should be initialized at the beginning of the program. The basic mechanism for servicing an interrupt is:

$$(SP - 1, SP - 2) \leftarrow PSW$$

$(SP - 3, SP - 4) \leftarrow PS$

$(SP - 5, SP - 6) \leftarrow PC$

$SP \leftarrow SP - 6$

$IE \leftarrow 0, BRK \leftarrow 0$

$PS \leftarrow vector high bytes$

$PC \leftarrow vector low bytes$

Figure 13. Interrupt Vector Table

Figure 14. Interrupt Vector 0

During interrupt servicing, the third item pushed on the stack is the return PC value. For some types of traps (divide error, CHKIND, illegal opcode, AFPP error, coprocesor not present, or other CP error), this value points to the instruction that generated the trap. For the other interrupts (single-step, BRK3, BRKV, NMI, or INT), this value points to the next instruction. Trap handlers for error traps can thus easily find the offending opcode, and other handlers can simply return after processing the interrupt.

#### STANDBY FUNCTION

The  $\mu$ PD70136 offers two standby modes to reduce power consumption: HALT and STOP. Both are entered after executing a HALT instruction.

### **HALT Standby Mode**

In the HALT standby mode, the internal clock is supplied only to those circuits related to functions required to exit this mode and bus hold control functions. As a result, power consumption is reduced to one-fifth the level of normal operation.

The HALT standby mode is exited when RESET or an external interrupt (NMI, INT) is received. If INT is used and interrupts were enabled before the HALT state was entered, an INTAK cycle will be performed to fetch a vector number. The interrupt service routine will be executed. After RETI, execution will resume with the instruction following the HALT. If interrupts were disabled, the interrupt service routine will not be entered, but execution will resume with the instruction following the HALT.

If  $\overline{\text{NMI}}$  is used to exit the HALT standby mode, the  $\overline{\text{NMI}}$  service routine will always be entered.

The bus hold (HLDRQ/HLDAK) function still operates during HALT standby mode. The CPU returns to HALT standby mode when the bus hold request is removed.

During HALT standby mode, when all control outputs go low, the address and data buses will be either high or low. Refer to table 1 for information about the states of other outputs in the standby mode.

## STOP Standby Mode

In the STOP standby mode, the  $\mu$ PD70136 clock is stopped for maximum power reduction. To enter this mode, special steps must be taken to prepare the  $\mu$ PD70136 for having its clock stopped.

INT,  $\overline{\text{NMI}}$  and HLDRQ must not be asserted while the  $\mu\text{PD70136}$  is in STOP mode, or for at least 10 clock periods before STOP is entered, or for at least 10 clock periods after STOP mode is exited. External hardware must ensure that these intputs are not asserted during this time.

STOP mode is entered by disabling  $\overline{\text{NMI}}$ , INT, and HLDRQ, entering the HALT standby mode, and stopping the clock input 10 clock periods after the HALT acknowledge but cycle is issued. The CLK input must be stopped during the low phase of the clock. STOP mode is exited when external logic starts the clock, waits 10 clock periods, and enable  $\overline{\text{NMI}}$ , INT, and HLDRQ; the  $\mu$ PD70136 will return to the HALT standby mode.

All output pins in STOP mode are in the same state as in HALT standby mode. Refer to table 1.

#### INSTRUCTION SET HIGHLIGHTS

### **Enhanced Instructions**

Instruction

PUSH Imm

In addition to the  $\mu$ PD8088/86 instructions, the  $\mu$ PD70136 has enhanced instructions listed in table 8.

Pushes immediate data onto stack

Table 8. Enhanced Instruction

**Function**

| FOOT IIIIII                                                                         | rushes inilitioulate data offic stack                                     |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| PUSH R                                                                              | Pushes 8 general registers onto stack                                     |

| POP R                                                                               | Pops 8 general registers onto stack                                       |

| MULL imm                                                                            | Executes 16-bit multiply of register or memory contents by immediate data |

| SHL Imm8<br>SHR Imm8<br>SHRA Imm8<br>ROL Imm8<br>ROR Imm8<br>ROLC Imm8<br>RORC Imm8 | Shifts/rotates register or memory by immediate value                      |

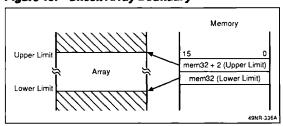

| CHKIND                                                                              | Checks array index against designated boundaries                          |

| INM                                                                                 | Moves a string from an I/O port to memory                                 |